JTAG(Joint Test Action Group,联合测试行动组)是一种国际标准测试协议(IEEE 1149.1),其主要用于芯片,PCB 和系统的测试,调试和编程。通过专用的硬件接口和协议,提供对芯片内部电路的非入侵式访问,JTAG 协议被广泛用于嵌入式开发,硬件验证验证和故障诊断等领域。本文主要用于介绍JTAG 协议在芯片ATE测试的常见应用场景及主要失效模型分析。· JTAG 模块及PIN 脚功能介绍 JTAG模块一般使用4/5个必需信号实现与其他系统间的交互,JTAG 的常见PIN 脚及功能描述如下图所示:

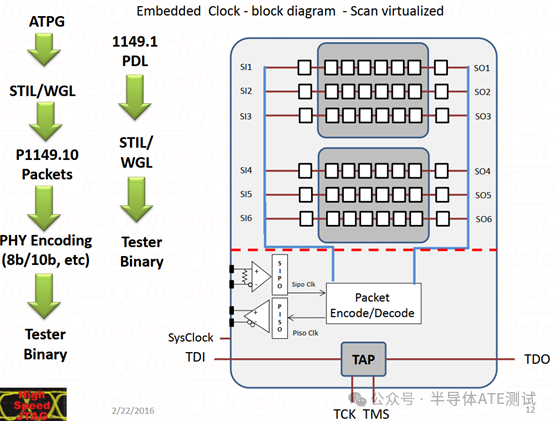

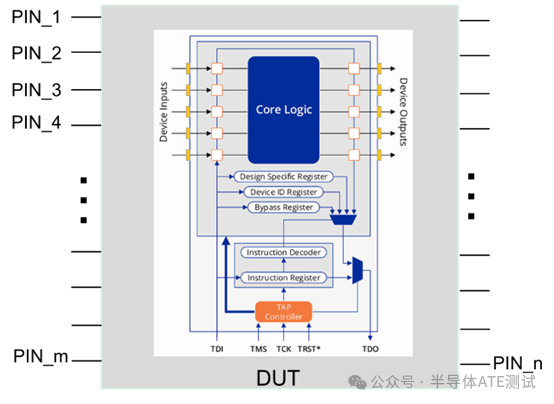

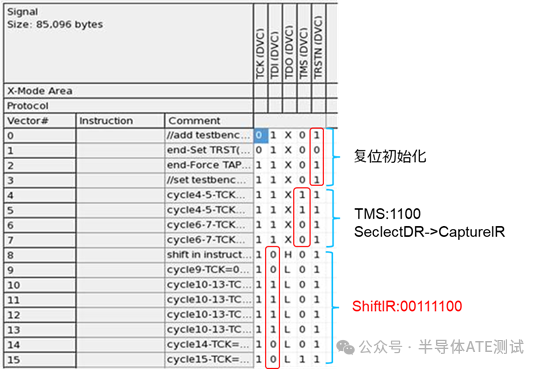

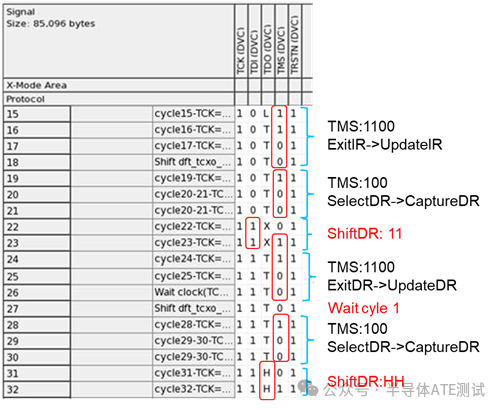

引用IEEE 1149.1标准文档中对JTAG 系统内部功能模块展示图如下:  如上图所示,JTAG 接口主要由状态机TAP, 编/解码器,和扫描链 三部分组成: 1.状态机-TAP controller(Test Access Port Controller): JTAG 的核心组件,通过TMS信号实现JTAG 内部数据流的控制,TMS 可控制的信号状态共有16种(常见的有: Shift-IR, Shift-DR,Run-Test 等,具体可参照IEEE 1149.1标准文档 ), 2.编/解码器(PacketEncode/Decode):编/解码器主要由: 指令寄存器(IR)和数据寄存器(DR)两部分组成。 · 指令寄存器-IR(Instruction Register):选择操作类型(如BYPASS, SAMPLE,EXETEST)实现对数据寄存器的控制。指令寄存器允许TAP将接收到的特定指令叠加,用来选择需要执行的测试,或这选择需要访问的测试数据寄存器 · 数据寄存器-DR(Instruction Decoder):存储具体数据(如扫描数据链,调试指令等),实现对芯片输入输出观察的控制。数据寄存器一般用于捕获或者写入所需的数据及地址信息。 3. 扫描链(Scan Chain): 不同IP 的DFT扫描链可以相互串联成一条链,通过TDI->TDO 依次访问,为了精准定位Pass/Fail 的IP,需要给JTAG 串联的IP 有唯一的ID 标识。 · JTAG 在ATE 测试中的应用 在芯片ATE (Automatic Test Equipment) 测试中,JTAG 是DFT(Design for Testability)测试向量(Pattern)的一种关键技术,其可以提高测试覆盖率,降低测试成本,并且JTAG接口还可支持复杂芯片的量产测试,以下是JTAG 在芯片ATE 和DFT 测试中的具体应用和实现方式。下图展示了JTAG 在DUT(Device Under Test) DFT测试的测试原理。  JTAG在芯片DFT测试中的常见应用有:边界扫描测试(Bscan),内部逻辑测试(InTest),内置自测试(BIST)三种。 · 边界扫描测试(Boundary Scan Test) · 利用JTAG 协议控制芯片内部IP 互联I/O 引脚单元组成测试链路(Chain),以实现通过4/5个JTAG 引脚完成内部成千上百I/O,Mux 互联通路的测试。实现芯片可测性提高,节省芯片ATE测试资源的目的。 · 基于JTAG 的边界扫描测试,也可用来检测输入/输出缓冲器(IO Buffer)是否正常工作 · 内置自测试(BIST) · 可通过JTAG 触发芯片内部的BIST 逻辑(如Memory BIST, Logic BIST)的测试,并读取测试结果 Bscan 配置Pattern 实例-93K(BIST配置模式类似) ·  内部逻辑测试(InTest) 通过JTAG 实现芯片内部逻辑(如寄存器,存储器及深嵌入式CPU 内核等),以替代传统的ATE 芯片逻辑向量测试。其优势是:可减少对ATE 测试通道的需求,进而降低测试成本。  · JTAG DFT Pattern 常见失效模型 1. 扫描链(Scan Chain)断裂或错位 · 表现: o ATE 读取IDCODE 失败,或扫描链长度与预期不符。 o Pattern 执行时,输出捕获(Capture)数据为全0/全1或随机噪声。 . 可能原因: o 设计问题:扫描链未正确插入(DFT工具配置错误) o 制造缺陷:扫描单元(Scan Cell)或链接线短路/断路 o 封装问题: JTAG引脚虚焊或绑定线断裂。 2. 时钟(TCK) 或控制信号(TMS)问题 表现: o TAP 控制器状态机无法正常跳转(如卡死在Reset 状态) o 数据移位(Shift)阶段出错,导致Pattern 对比失败 .可能原因: o TCK 频率超出芯片规格(ATE 时钟配置错误) o TMS信号时序违例(建立/保持时间不足) o 信号完整性差(反射,串扰,地弹噪声) 3. 边界扫描失效(Boundary Scan Fail) 表现: o EXETEST 模式下,输入/输出引脚电平不符合预期 o SAMPLE/PRELOAD 指令无法正确捕获引脚状态 . 可能原因: o 边界扫描单元(BSC)未正确插入或连接 o PCB互联问题(如开路,短路) o 测试向量生成错误(如未覆盖所有BSC) 4. 内部逻辑测试失效(BIST Fail) 表现: o INTEST模式下,内部寄存器读写异常 o RUNBIST指令执行后,BIST结果错误 .可能原因: o 测试逻辑(如BIST 引擎)未正确集成 o 时钟域交叉(CDC)问题导致信号不同步 o 测试向量未覆盖目标逻辑路径 5. 多器件链同步问题(Daisy Chain Synchronization Fail) .表现: o 链中部分器件无响应,或IDCODE顺序错误 o 数据移位时链间干扰(如TDO信号串扰) .可能原因: o 器件扫描链长度配置错误(ATE与设计不匹配) o 某器件JTAG接口被禁用(如熔丝位烧录错误) 6. 电源环境敏感性问题 .表现: o 高温/低温或低压下Pattern失效 o 随机性错误(如偶发TDO数据错误) .可能原因: o 电源噪声导致JTAG 信号抖动 o 温度漂移影响TCK时序 · 常见Debug思路与步骤: 1. 隔离硬件问题 确认芯片JTAG相关PIN脚是否正确接通(PerPin PMU 测试相关channel OS value,注意此时PIN 脚ac relay 需断开) 检查芯片供电情况(在机台Pogo 利用示波器/万用表抓取PowerUp 时,相关Power PIN 的实际上电波形/上电电压值) 确认当前Pattern 配置(system) o Scan mode(BIST pattern test), o Extest Mode(external test mode:常用于Bscan Pattern test ), o Function mode(SLT test,交付客户正常使用)。 o 在条件允许的情况下:交换芯片, LB/PC ,测试机,排除测试硬件对测试结果的影响。 2. ATE 失效Pattern分析Tools 在利用ATE 机台抓取FailCycle 时特别关注首个失效点,DFT 部门可根据FailCycle 定位究竟是哪个Scan Cell 异常,进而给出该Scan Cell 相关Pin 脚List及失效模型,及调试思路(可根据此调试思路采用"隔离硬件问题"中的第1,2步,进一步定位问题所在。) 协同DFT 部门同事,拆分Pattern, 逐步缩小出问题的IP范围,此举也能排除芯片内部IR Drop对Pattern 测试结果的影响(为降低测试成本,一条Pattern 中经常会包含多个IP 的Test cell, fail 出现时,split Pattern可方便我们尽快确认具体Fail IP) 抬升测试程序中关于TDI PIN脚输入电压值的设置,relex TDO PIN 脚电压设置,(可排除ATE 相关硬件对pattern 测试结果的影响) Relex test Period,确认是stack fail 还是transtation fail Burst setup pattern 和 Scan pattern,排除test suit 切换导致clock 重启进而引发的Fail 修改system clock 占空比,排除DUT系统时钟树裕量不够导致的Fail 利用Timing Diagram 手机分析关键PIN脚波形图。 JTAG在芯片ATE和DFT测试中是不可或缺的技术,它通过边界扫描和标准化接口,显著提升了测试效率和覆盖率。对于DFT工程师,合理设计JTAG链和指令集是关键;对于ATE工程师,需熟练掌握JTAG协议与测试程序的集成。随着芯片复杂度提升,JTAG与BIST、SCAN等技术的结合将更加紧密。 |