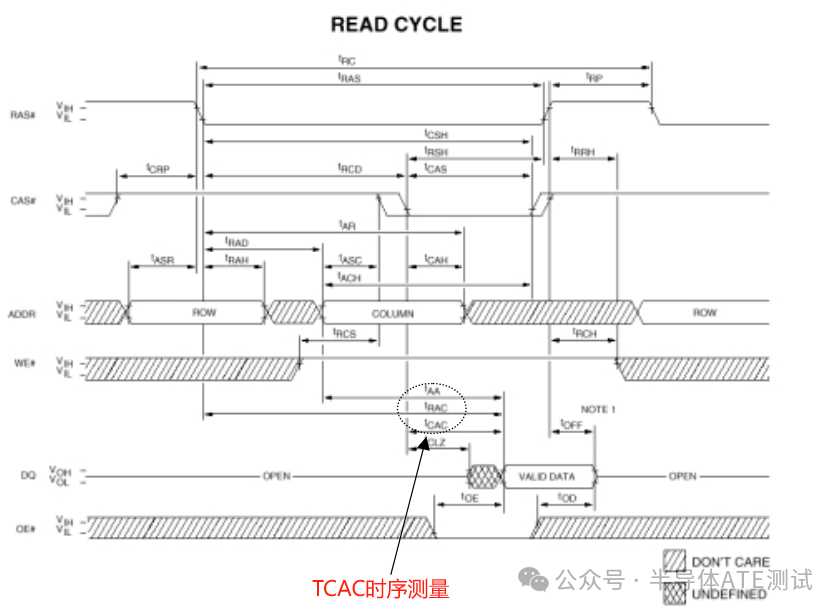

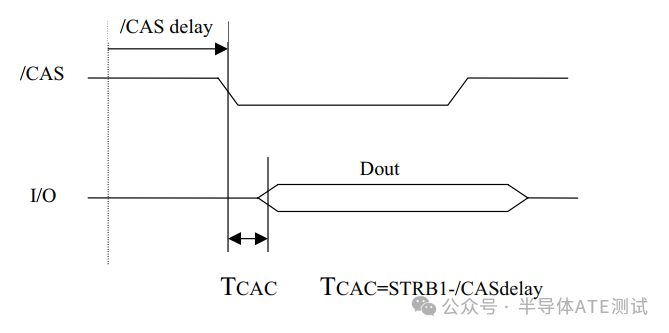

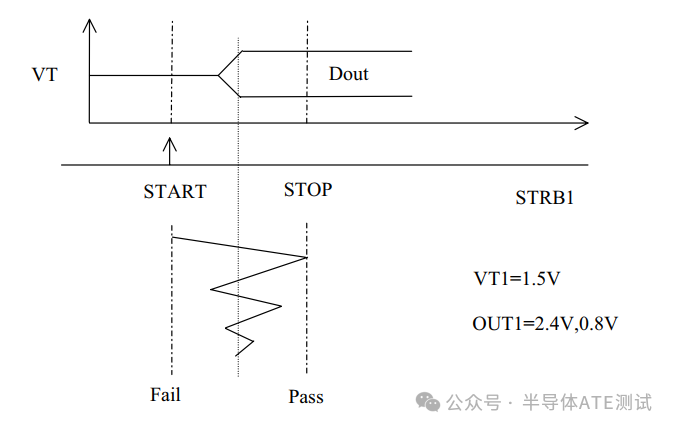

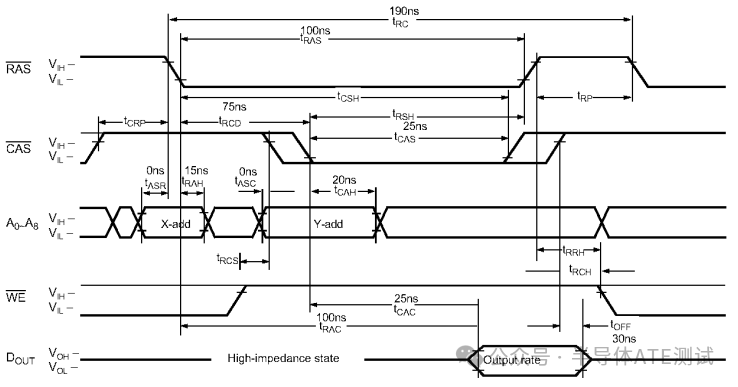

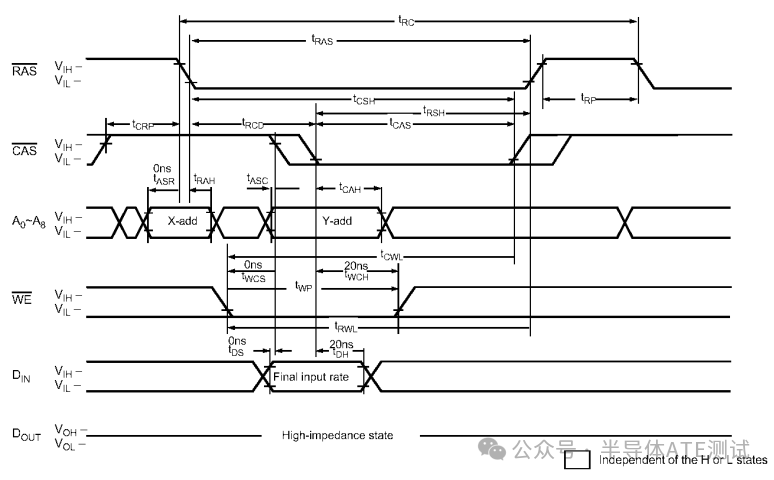

书接上文 (Memory测试浅谈) 我们来继续探讨ATE Memory常见测试项目--交流参数测试。交流参数测试(AC Parametric Test): 交流参数测试的目的是确保集成电路(IC)能够符合时序(Timing)规格。在第一章中有一份spec示例,其中很多内容就是用来规范时序规格的,如下图所示。 以TCAC为例进行说明,TCAC是指当CAS信号变为低电压时,集成电路数据线上的数据稳定的时间。  使用 TMEAS Utility函数来测量 TCAC 的时间 TMEAS 是一个实用程序,它通过改变测试条件并比较测试结果,采用二分搜索(Binary Search)的方式来确定所需的时间点。在此示例中,TMEAS 通过调整 STRB 的时间点,来确定 Dout 的时间点,从而计算出 TCAC 时序。 时序图(Timing Chart)   功能测试(FUNCTION TEST) 功能测试旨在验证集成电路的逻辑功能是否正常运作,例如: · 存储器集成电路:验证写入与读取功能是否正确 · 逻辑集成电路:验证AND(与)、OR(或)等逻辑门功能是否正常 读取时序:  写入时序:  1. 功能测试(FUNCTION TEST)为验证存储器元件的读写功能,需按照被测元件的时序图(如前页所示)执行以下测试流程: 2. 写入阶段:依据时序规范将测试数据写入存储单元 3. 读取阶段:从相同地址读取存储数据 4. 数据比对:将读出数据与原始写入数据进行校验 通过该测试流程可判定存储器的写入、存储和读取功能是否正常运作。 存储器元件中存储数据与存储地址的对应关系称为 测试模式(PATTERN)。由于存储器元件内部电路结构及其存储数据(0/1电平)的对应关系会影响元件性能,因此在存储器测试中,不同测试模式的验证成为核心工作。 测试模式的生成是通过微指令运算程序控制 模式发生器(Pattern Generator) 来实现的,该发生器可产生相应的周期性信号。以下是典型的测试 模式示例: 1. 测试程序架构 (1)主程序(Main Program) ① 测试条件设置(Set Test Condition) 2. 时序设定: · 测试速率(Test Rate) · 驱动时钟(Driver Clock) · I/O驱动使能时钟(I/O Driver Enable Clock) · 比较器选通信号(Comparator Strobe) · 电压设定: · 驱动器:INn · 比较器:OUTn · 终端电阻:VTn · 程序加载:ILn · 器件电源:VSn=2V · DC测量单元:VSIM=2V · 引脚状态配置: 将时序和电压参数分配至对应引脚 Pn = [电压值, 时序参数, 波形, 测试模式分配] ② 测试流程控制(Control Test Sequence) 硬件单元启停控制(RON/ROFF) 传输测试模式程序至PG(Pattern Generator) STOP/END指令处理(程序停止与编译结束) 控制位读取 调用PBDATA 执行时序补偿 测试项目编号设置 分类(Category)与分选表(Sort Table)配置 ③ 启动测试 MEAS MPAT(模式测量) MEAS DC(直流测量) MEAS VS(电压测量) (2)测试模式程序(Pattern Program) 使用ALPG(算法模式发生器)微指令集编写,用于定义测试模式。 (3)接口程序(Socket Program) 多芯片测试硬件映射配置文件。 |