存储器作为存储信息的媒介,在集成电路产业里占据着重要的地位。 随着三维存储技术在 NAND Flash 生产制造中的广泛应用, NAND Flash 正朝着更高存储密度、更大存储容量、更快数据传输速率的方向发展

1. NAND Flash 存储器结构

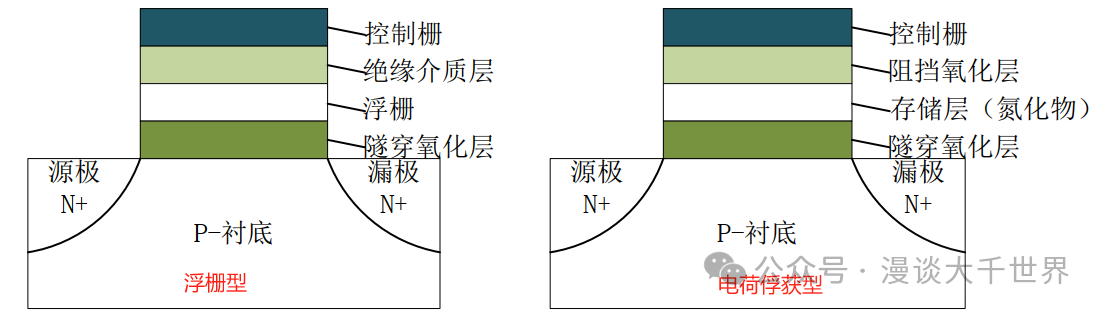

NAND Flash根据基本组成单元的不同可以分成浮栅(Floating Gate, FG)型和电荷俘获(Charge Trap, CT)型。这两种技术在存储单元的基本组成和工作原理上有所不同。

1. 浮栅(FG)型NAND Flash:

. 结构:浮栅型NAND Flash存储单元包含控制栅(Control Gate, CG)、绝缘介质层、浮栅、隧穿氧化层(Tunnel Oxide, TOX)、源极、漏极和衬底。

. 工作原理:浮栅中存储电荷,控制栅用于控制浮栅的电荷状态。在编程时,电子通过隧穿氧化层从衬底注入到浮栅中;在擦除时,电子从浮栅返回到衬底。

2. 电荷俘获(CT)型NAND Flash:

. 结构:电荷俘获型NAND Flash存储单元由控制栅、阻挡氧化层、存储层(通常由氮化硅制成)、隧穿氧化层、源极、漏极和衬底组成。

. 工作原理:电荷被存储在绝缘材料(如氮化硅)中,而不是浮栅。在编程时,电子通过隧穿氧化层进入存储层;在擦除时,电子从存储层释放到衬底。

两种技术各有优缺点,浮栅型技术相对成熟,但随着制程技术的发展,电荷俘获型技术因其更好的缩放能力和耐久性而越来越受到重视。随着技术的进步,这两种类型的NAND Flash都在不断地发展和改进,以满足不断增长的数据存储需求。

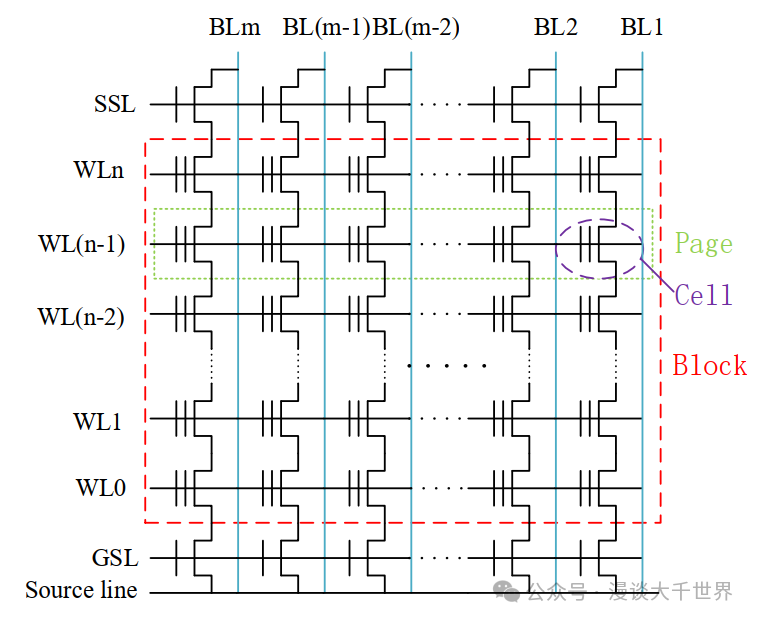

2. NAND Flash 芯片组成

NAND Flash芯片的组成结构由大到小依次为芯片(Chip)、颗粒(Die)/逻辑单元(Logical Unit Number, LUN)、平面(Plane)、块(Block)和页(Page)。其中,页是执行读取/编程操作的最小单位,块是执行擦除操作的最小单位。NAND Flash存储器物理块的阵列结构如图所示。

1. 存储字符串(Bit Line, BL):

. 在NAND Flash中,存储字符串是由多个NAND Flash单元的漏极连接组成的一条位线(BL)。这些单元是串联在一起的,形成一个垂直的链。

. 一个存储字符串通常包含8到64个存储单元,这些单元共享同一个漏极连接。

2. 物理页(Word Line, WL):

. 从水平方向来看,多个存储单元的控制栅串联组成一条字线(WL)。

. 每条WL对应一个物理页,物理页是NAND Flash中可以被单独读取或编程的最小单位。

3. 多比特存储技术:

. 随着多比特存储技术的发展,一个物理页可以包含多个逻辑页,这意味着每个存储单元可以存储多个比特的信息,从而提高存储密度。

4. 字符串选择线(String Select Line, SSL):

. SSL用于选择特定的存储字符串(BL),以便进行读取、编程或擦除操作。

5. 地选择线(Ground Select Line, GSL):

. GSL用于选择特定的源线,控制哪些存储单元的源极被连接到一起,以便进行操作。

6. 源线(Source Line, SL):

. 源线连接着所有存储单元的源极,是NAND Flash阵列中的一个重要组成部分,用于控制电流流向。

这些组件共同构成了NAND Flash的存储阵列,使得数据可以被有效地存储和访问。通过精确控制这些线路,NAND Flash能够实现快速的数据读写和擦除操作。

3. 存储器测试算法

在进行存储器测试时,最关键的一点就是测试算法的选择,存储器的测试算法种类非常多,近年来由于存储器的发展呈现高集成度大容量的趋势,所以大家都追求高效率的测试算法,各种算法的发展也成了伴随存储器发展的一个核心内容。

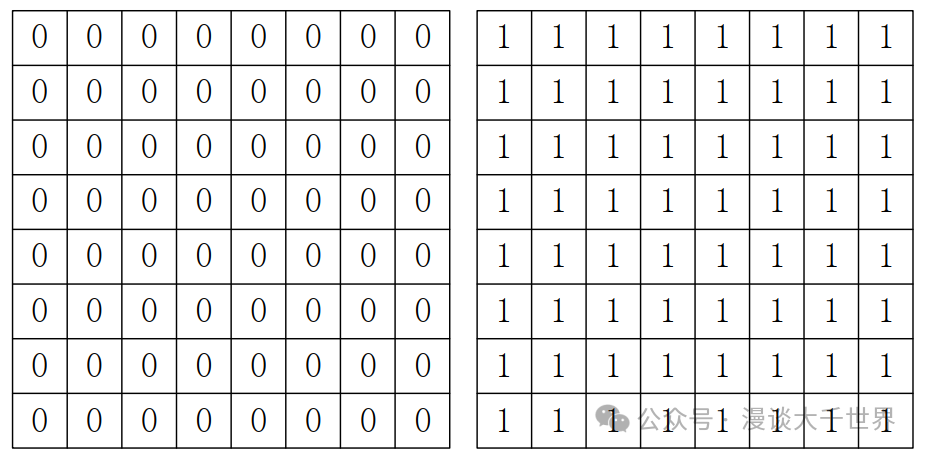

MSCAN算法:存储器扫描算法就是对整个存储单元阵列进行一次扫描式的编程。MSCAN算法的原理很简单,即对存储阵列进行全“0”和全“1”的检测,这种测试方法速度很快,可以用于检测固定故障、固定开路故障和翻转故障,但是缺点也很明显,对整个存储单元阵列的故障检测的覆盖率比较低。

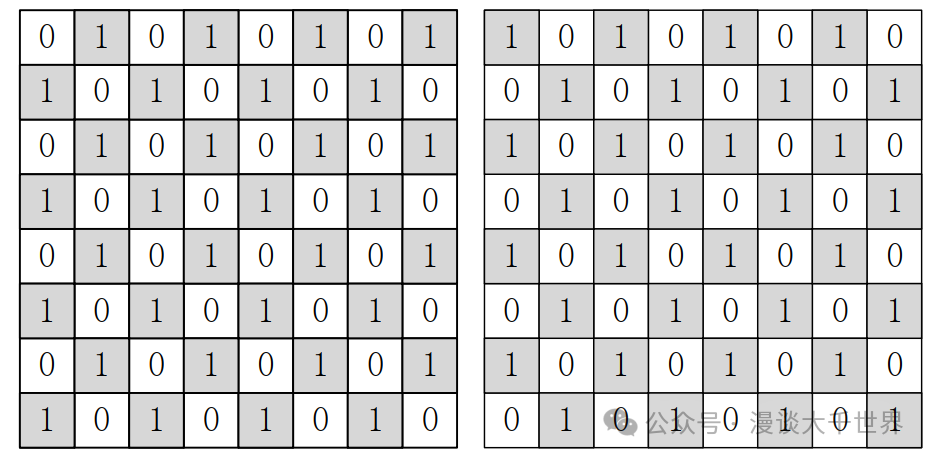

Checkerboard算法,又称为棋盘测试,这也是一种基础测试算法,这种测试适合于检测单元间距越来越小的情况下,相邻两个单元是否能正常赋值,相互之间是否会受到影响,同样可以检测固定故障、固定开路故障和翻转故障。棋盘测试的特征就是相邻两个单元值都不相同,可以用于检测耦合故障。

伪随机测试图形是NAND Flash测试中应用最为广泛的测试图形。伪随机测试图形可以很好地模拟闪存在实际使用场景中的故障情况,可以综合闪存中存在的各种各样的故障类型,对于闪存测试中具有良好的普适性。伪随机测试图形可以检测出部分固定故障、固定开路故障和翻转故障,此外还可以用于检测耦合故障和地址译码故障。

4. 基于V93k 的测试系统结构

ATE系统和测试流程描述:

1. PC机:安装有V93000测试软件SmarTest,用于创建和管理测试工程,包括定义待测芯片参数、设置电平和时序、生成测试向量、编写测试方法、调试测试程序以及进行测试结果的统计与分析。

2. 电源板卡DPS64:为待测NAND Flash芯片提供稳定的电源,并可用于测试电源电流。

3. 数字板卡PS1600:发送控制信号和数据信号到NAND Flash,配置电平、时序、测试向量,相当于NAND Flash的控制器,控制NAND Flash的操作。

4. 设备接口板(DIB):设计用于匹配ATE测试头管脚分布,将ATE发出的信号传输到待测芯片(DUT)。

5. 待测芯片(DUT):待测的NAND Flash芯片,放置在翻盖式插座中,便于更换和检查。

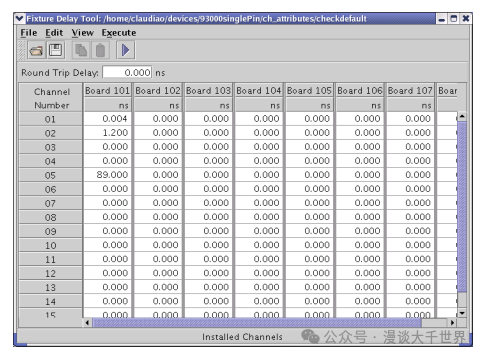

管在PCB设计时考虑到等长设计的原则,但由于PCB板在制作过程固有的工艺缺陷或其他因素,很可能造成接收端口各个引脚接收到信号的时间不同步,彼此之间还存在较大的时序误差,尤其是在传输高速数字信息时,会造成传输故障。所以在PCB制作完成安装到测试后,需要对测试平台进行系统校准。测量每条传输线的延迟大小,调整测试信号的收发时序,同步芯片上各个引脚接收测试信号的时间。下图展示了V93K的校准方法:

整个测试系统通过这些组件协同工作,完成NAND Flash芯片的测试过程,确保芯片的性能和可靠性。

|