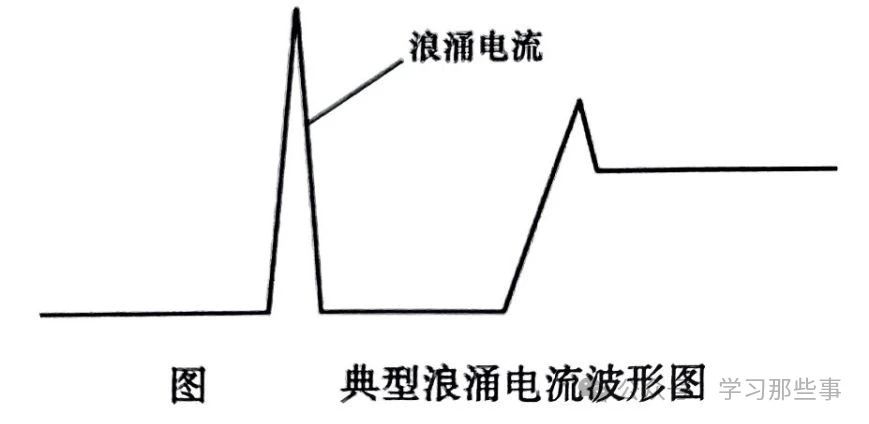

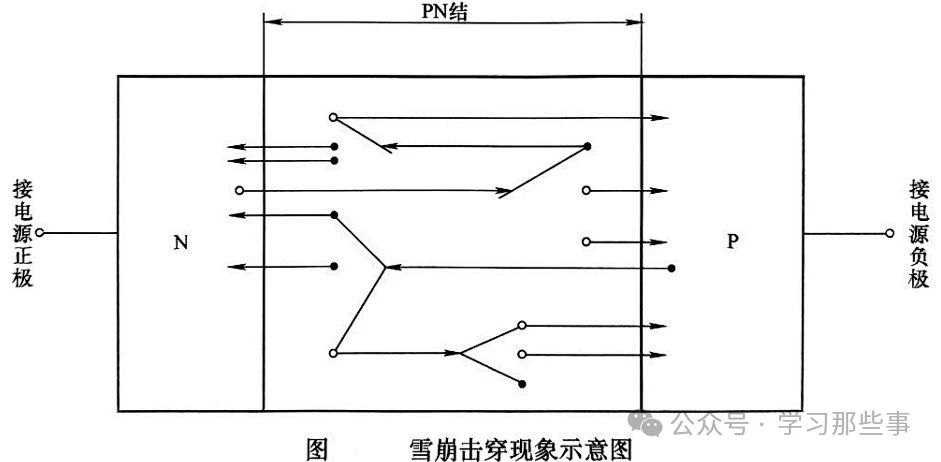

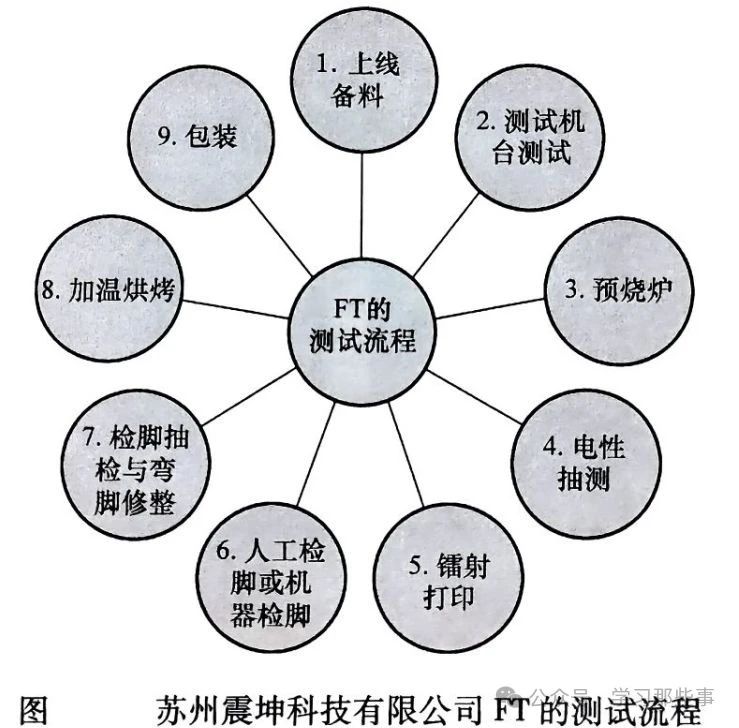

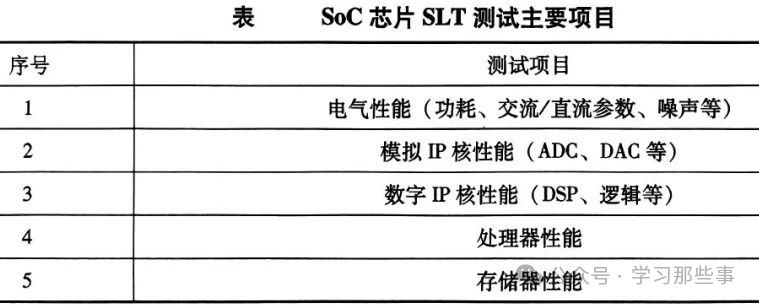

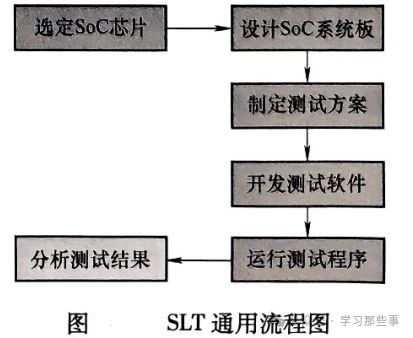

芯片极限能力、封装成品及系统级测试有关功率器件测试的文章已有半导体器件的失效分析及可靠性测试,功率器件的电特性测试两文,本文是对其中未涉及的部分进行简单介绍,分述如下: 极限能力测试 封装成品测试(Final Test, FT) 系统级测试(SLT) 1.极限能力测试 极限能力测试包括以下两个方面: 浪涌电流测试 大容量的电气设备接通或断开瞬间,由于电网中存在电感,将在电网中产生浪涌电压,从而产生浪涌电流。 浪涌电流测试的目的是评估电气设备在遭受浪涌电流冲击时的耐受能力。测试过程中,通常会使用专门的测试仪器,如浪涌发生器,来模拟真实的浪涌现象。测试步骤包括确定试验条件、安装与连接待测设备、设定试验参数、执行试验、结果分析和改进措施等。  在测试过程中,需要关注浪涌电流的波形、峰值和持续时间等参数。那些参数对电气设备的性能和安全运行具有重要影响。如果浪涌电流过大,可能会导致设备损坏或故障,甚至可能引发火灾等安全事故。 为了避免浪涌电流对电气设备的影响,电源通常会限制整流桥、熔断器、AC开关、EMI滤波器所能承受的浪涌水平。同时,在设备设计和制造过程中,也需要采取相应的措施来提高设备的抗浪涌能力。 雪崩能量测试 雪崩能量测试是针对功率场效应晶体管(如MOSFET)的一种极限能力测试。 雪崩能量测试的目的是评估器件在雪崩击穿状态下能够承受的最大能量。测试过程中,通常会使用专门的测试电路和设备来模拟雪崩击穿现象,并测量器件在击穿过程中消耗的能量。 雪崩能量测试包括可逆测试和不可逆测试两种类型。可逆测试是指在测试过程中,器件在经历雪崩击穿后能够恢复正常工作状态的测试。不可逆测试则是指器件在经历雪崩击穿后无法恢复正常工作状态的测试。不可逆测试不仅可以判定器件是否能承载电路的关断回馈能量,还可以进行器件最大雪崩能量的测试。  在测试过程中,需要关注雪崩能量的值、器件的击穿电压和电流等参数。那些参数对器件的性能和可靠性具有重要影响。如果雪崩能量过大,可能会导致器件损坏或失效。 为了提高器件的雪崩能量承受能力,可以在器件设计和制造过程中采取相应的措施,如优化器件结构、提高材料质量、改进封装工艺等。同时,在器件使用过程中,也需要注意避免过高的漏源电压和电流等条件,以防止器件发生雪崩击穿现象。 综上所述,极限能力测试是评估电气设备或器件在极限条件下性能和安全性的重要手段。通过浪涌电流测试和雪崩能量测试等测试方法,可以全面认知设备或器件在极端条件下的表现,并为设备或器件的设计、制造和使用提供重要的参考依据。 2.封装成品测试(Final Test, FT) 封装成品测试(Final Test, FT)是半导体生产流程中的一个关键环节,它针对封装好的芯片进行设备应用方面的全面检测。  以下是FT测试流程的详细分述: 上线备料 目的:将待测的芯片整理并放置在标准容器中,以便在测试机台上进行自动化测试。 操作:确保待测品在分类机内能够被准确定位,便于自动化机械结构自动上下料。 测试机台测试 功能:测试机台通过PE Card发出待测品所需的电信号,并接收待测品反应的电信号,最终判断产品的电性测试结果。 流程:待测品经过入库检验及上线备料后,进入测试机台进行测试。 预烧炉(针对高单价芯片) 目的:为待测品提供一个高温、高电压、大电流的环境,使生命周期较短的芯片在加热过程中提早暴露问题,降低客户使用时的失败率。 应用:主要测试存储器类产品。 电性抽测 目的:验证测试机台测试的准确性,通过抽取一定数量的待测品重回测试机台进行测试,比较测试结果的一致性。 处理:若测试结果不一致,需检查测试机台、测试程序、测试配件及测试过程是否存在问题。 镭射打印 操作:利用镭射打印机,根据客户的正印规格,在芯片上打印指定的标识。 设备:如图4-22所示,为镭射打印机的实物图。 人工检脚或机器检脚 目的:检验待测品的正印和接脚的对称性、平整性及共面度等。 方式:有时利用镭射扫描进行,有时则采用人工检验。 检脚抽检与弯角修整 抽检:对弯角品进行抽检,确保产品质量。 修整:对弯角品进行修复作业,确保接脚符合规格。 加温烘烤 目的:在所有测试及检验流程之后,通过烘烤炉烘干待测品上的水汽,防止水汽腐蚀影响产品品质。 操作:将待测品置于烘烤炉中进行烘烤。 包装 操作:根据客户的指示,将待测品从标准容器内分类包装到客户指定的包装容器内,并粘贴必要的商标。 要求:确保包装符合客户的规格和要求。 综上所述,封装成品测试(FT)是一个复杂而细致的过程,它涵盖了从上线备料到包装的多个环节,旨在确保封装好的芯片在设备应用中表现出色,满足客户的品质要求。 3.系统级测试(SLT) 系统级测试(SLT)是半导体及电子设备制造领域中的一项关键测试技术,它旨在弥补ATE(自动测试设备)测试在复杂度和故障覆盖率方面的不足。 以下是SLT测试流程及相关内容的分述: 系统级测试(SLT)的重要性 技术进步的挑战:随着工艺节点的不断缩小和AI等设备中晶体管数量的激增,ATE测试的故障覆盖率难以满足100%的需求。SLT能够发现并修复ATE测试中遗漏的故障,提高产品质量。 复杂性的增加:SoC(系统级芯片)、SIP(系统级封装)和软件的复杂性增加,导致异步接口数量增多,软硬件交互更加频繁。SLT在复杂接口的测试方面更具优势,能够经济有效地实现高故障覆盖率。 产品上市时间的压力:产品上市时间缩短,制造工艺缺陷较多,制造商需要在工艺缺陷率较高时加速出货。SLT能够在设备开发早期提高测试故障覆盖率,减少后续返工修复,缩短上市所需时间。 工艺和封装技术的进步:前沿工艺和封装技术的采用增加了潜在故障和新故障模式的概率。SLT能够检测到那些潜在故障,降低设备的整体成本。 SoC芯片的SLT测试主要项目  对于SoC芯片,SLT的测试主要项目包括但不限于功能测试、性能测试、功耗测试、稳定性测试、兼容性测试等。 那些测试项目旨在全面评估SoC芯片的性能和可靠性。 SLT的通用流程  分析测试结果:一旦出现故障,测试工程师需要依靠自身经验来判断故障的原因,可能是SoC芯片设计问题、SoC系统板设计问题或测试软件问题。根据故障原因,采取相应的修复措施。 综上所述,系统级测试(SLT)在半导体及电子设备制造领域中具有重要意义。通过SLT测试,可以全面评估SoC芯片的性能和可靠性,提高产品质量和竞争力。 |