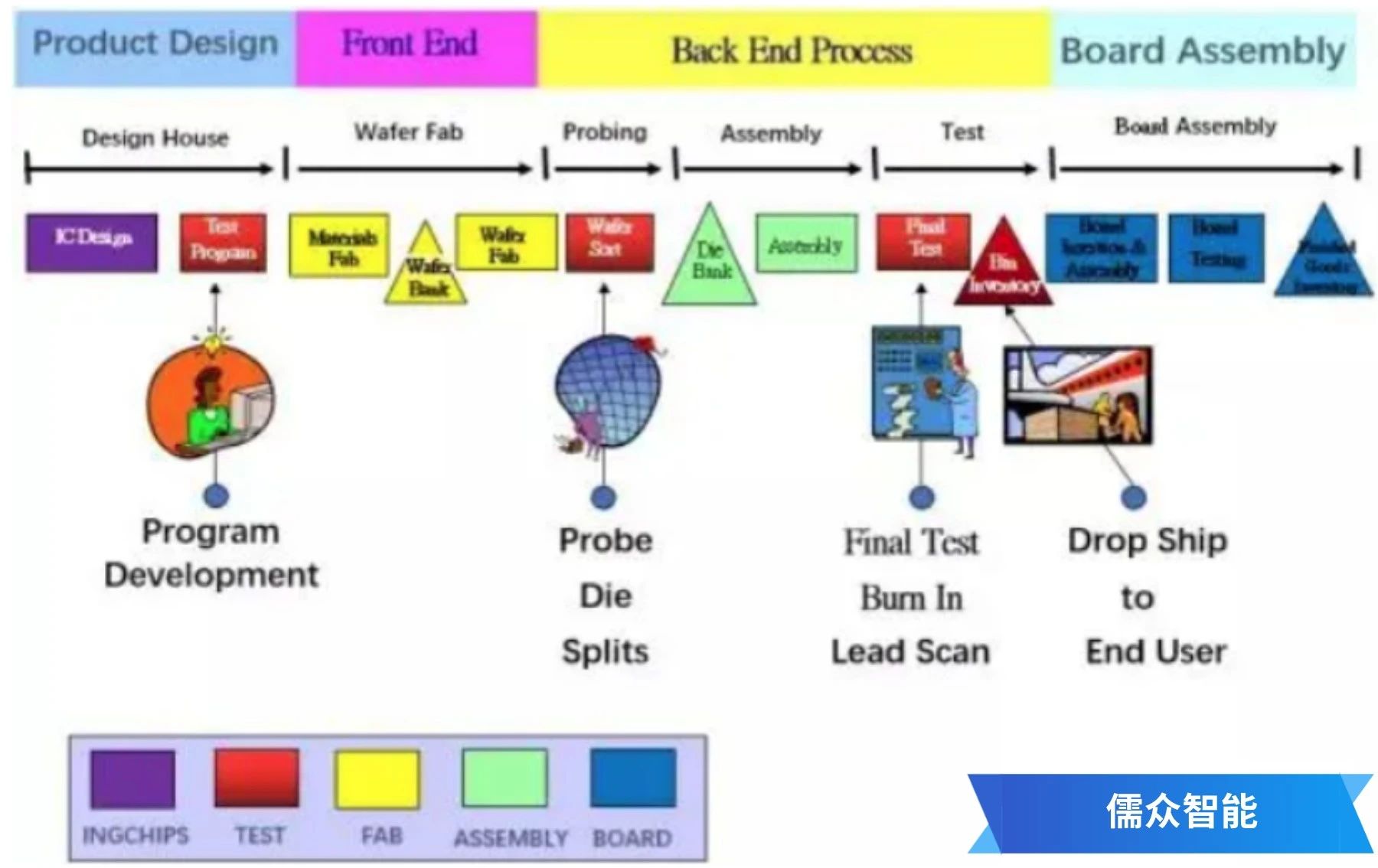

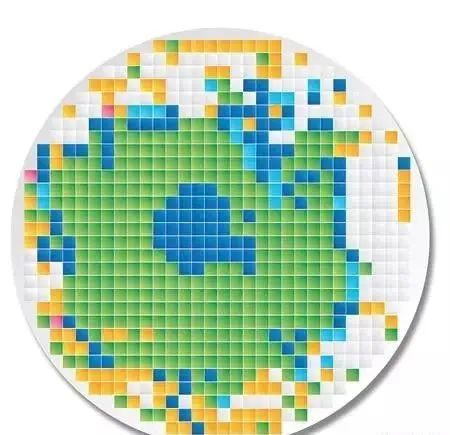

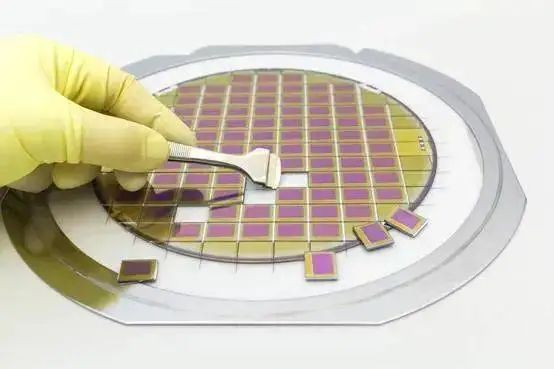

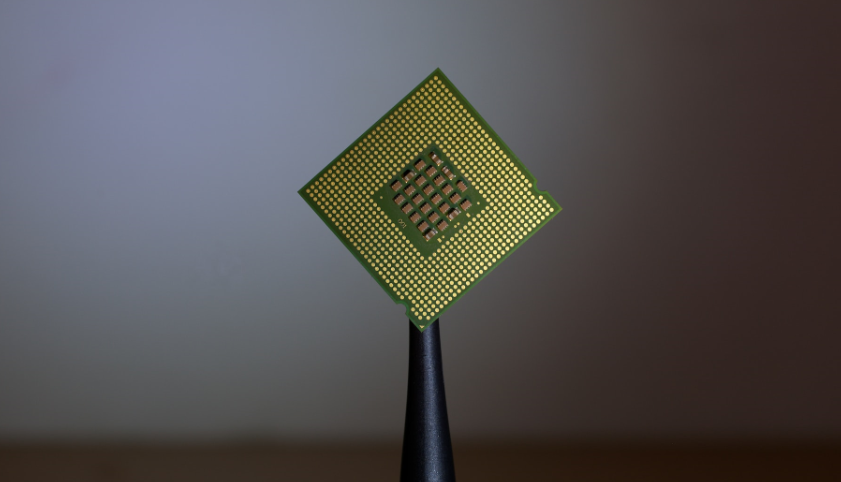

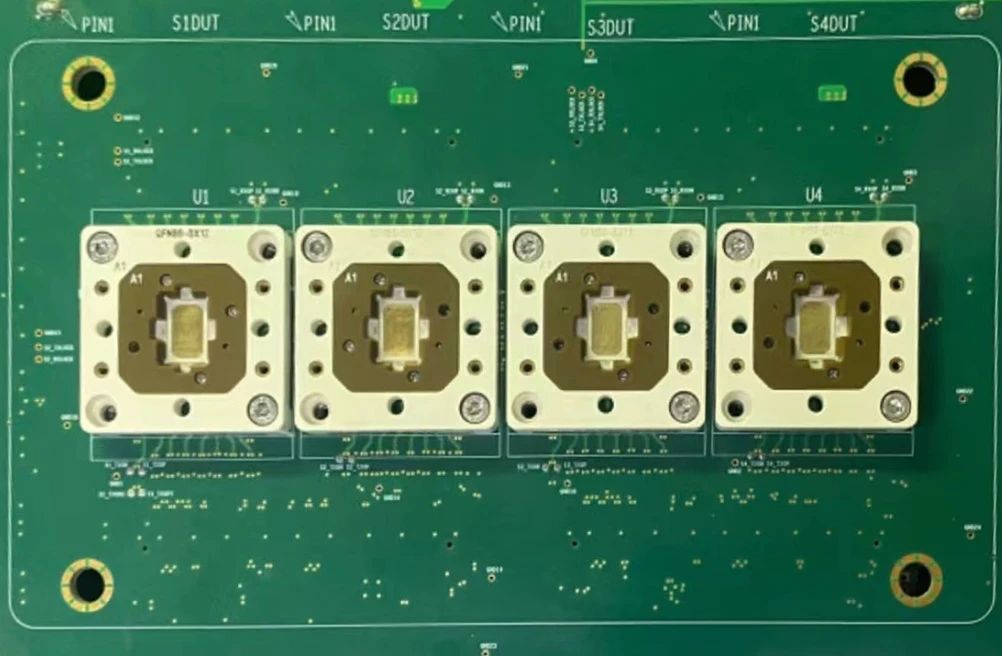

为了保证芯片的质量和稳定性,每一颗晶圆芯片在生产和封装后都需要经过严格的测试。不论是单颗晶圆还是芯片集成电路,都需要经过一系列的测试。 主要目的是确定芯片电子元器件的质量、性能、可靠性等参数是否符合设计要求,保证其在实际使用中达到预期的指标和稳定性。  同时,芯片测试也可以发现芯片制造工艺存在的问题和不足之处,帮助优化芯片设计和制造工艺。 最终,芯片测试结果可用于评估芯片产品的竞争力、商业价值和市场前景。 半导体生产流程由晶圆制造,晶圆测试,芯片封装和封装后测试组成。 测试环节主要集中在CP(chip probing)、FT(Final Test)和WAT(Wafer Acceptance Test)三个环节。  芯片测试的主要环节 DFT(Design For Test)简而言之,DFT就是通过某种方法间接观察内部信号的情况,例如scan chain之类。 然后通过特定的测试仪器来测试——这种仪器不是简单的示波器,它要能产生各种测试波形并检测输出,所以一套平台大概要上百万。 而且这些DFT比较适合于小芯片,大芯片像CPU之类的还会使用内建自测试(built-in self test),让芯片自己在上电后可以执行测试,这样就大大减小了测试人员的工作量。  DFT测试通过之后,就到正式的芯片测试环节了。 一般是从测试的对象上分为WAT、CP、FT三个阶段。 WAT:Wafer Acceptance Test,是晶圆出厂前对testkey的测试。在晶圆加工过程中进行的测试,通过WAT,晶圆厂可以早期识别晶圆加工中的问题,如掺杂浓度不一致、光刻问题或蚀刻缺陷等,从而及时调整生产过程,避免大规模生产不良产品。 采用标准制程制作的晶圆,在芯片之间的划片道上会放上预先一些特殊的用于专门测试的图形叫testkey。这跟芯片本身的功能是没有关系的,它的作用是Fab检测其工艺上有无波动。 因为代工厂只负责他自己的工作是无误的,芯片本身性能如何那是设计公司的事儿。只要晶圆的WAT测试是满足规格的,晶圆厂基本上就没有责任。如果有失效,那就是制造过程出现了问题。  CP测试:Circuit Probe,是封装前晶圆级别对芯片测试。这里就涉及到测试芯片的基本功能了,不同项目的失效,会分别以不同颜色表示出来。 失效的项目反映的是芯片设计的问题。 在半导体制造结束后,芯片从晶圆分割并封装之前,使用探针卡接触晶圆上的芯片,进行电气测试以确保它们符合规格,一般包括vt(阈值电压),Rdson(导通电阻),BVdss(源漏击穿电压),Igss(栅源漏电流),Idss(漏源漏电流)等,不同类别的产品测试的参数也不同。  通过了这两项后, 晶圆会被切割,切割后的芯片按照之前的结果分类。只有好的芯片会被送去封装厂封装,封装的地点一般就在晶圆厂附近, 这是因为未封装的芯片无法长距离运输。 封装的类型看客户的需要, 有的需要球形BGA, 有的需要针脚, 总之这一步很简单, 故障也较少.。由于封装的成功率远大于芯片的生产良品率, 因此封装后不会测试。 FT测试:Final test,封装完成后的测试,也是最接近实际使用情况的测试,会测到比CP更多的项目,处理器的不同频率也是在这里分出来的。 通常是在芯片封装完成后进行的最终测试。 这个测试目的是验证封装好的芯片在功能上是否完全符合设计规格,包括其性能、功耗、可靠性等。  这里的失效反应封装工艺上产生的问题,比如芯片打线不好导致的开短路。 为了保证出厂的芯片都是没问题的, Final test也即FT测试是最后的一道拦截, 也是必须的环节。 总而言之,CP,WAT在晶圆上测,FT则是对封装好的每颗芯片进行测试。 CP是所有半导体制造工艺结束后测,WAT在特定半导体制造工艺结束后测,而FT是芯片封装完毕后测。 测的频率不同:WAT一般是抽测,CP可抽测可全测,FT是全测。 FT测试解决方案 FT测试主要是为了解决各种不确定因素,找出芯片运行过程中是否存在功耗过大、温度过高等问题,并通过提取数据反馈给客户,帮助客户发现问题,提高成品芯片的产量。 基于芯片种类的差异,芯片封装流程中的测试节点也不尽相同,测试方案与测试程序也都有所差异,因此成品测试更偏向于为客户提供定制化的服务。  儒众智能以客户需求为导向,多元化探针TOP设计、多样化探针结构设计、满足多样封装测试需求,为企业提供优质的FT测试解决方案,协助客户降低生产成本并完善产能准备,严守芯片出货最后一道关口。 核心技术以及高竞争力的服务与价值使得儒众智能一路走来深获众多客户信赖,并建立良好的长期合作关系,成为半导体测试大厂在测试治具采购上优质的选择。 |