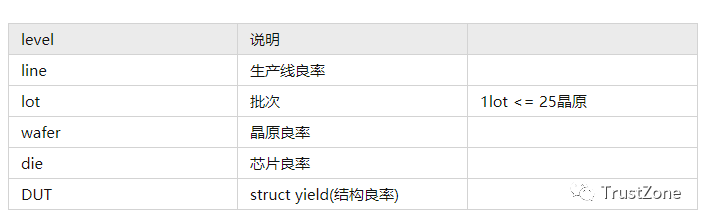

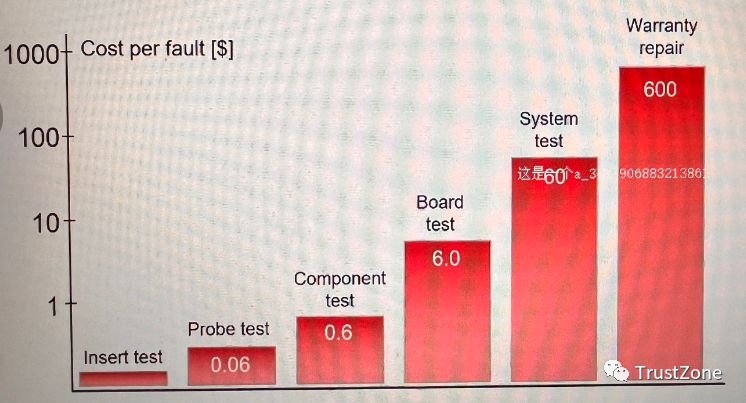

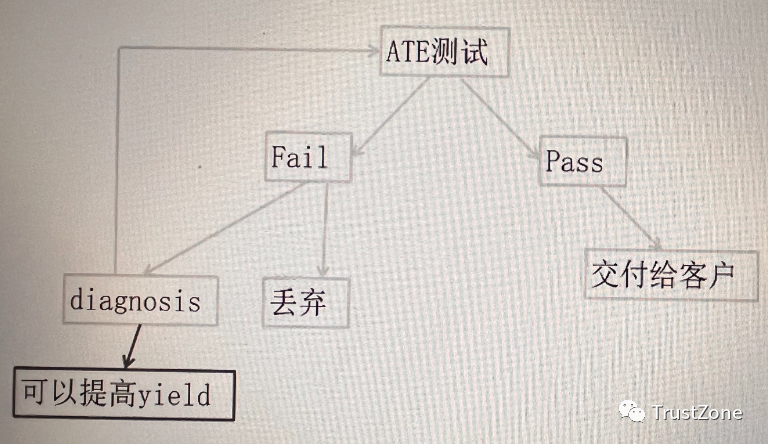

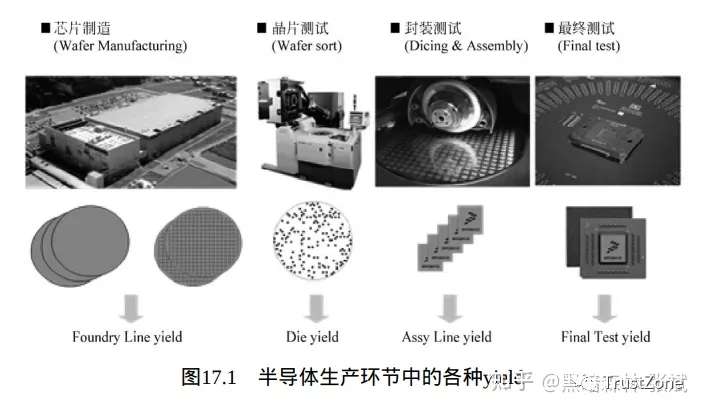

一、什么是DFT?• DFT(Design for Test),即可测性设计 • 一切为了芯片流片后测试所加入的逻辑设计,都叫DFT。 • DFT只是为了测试芯片制造过程中有没有缺陷,而不是用来验证芯片功能的。芯片功能的完善应该应该是在芯片开发过程用先进验证方法学去做的。 • 芯片制造过程相当复杂,工艺缺陷难免会存在,DFT的目的就是从制造完成的芯片里挑出有缺陷的芯片,以免有缺陷的芯片到了客户于上,造成更大的经济和时间损失。 二、测试的重要性在某层测试上漏掉了一个有故障的芯片,可能在下一层测试上需要花费10倍的cost才能发现它,所以,需要依赖DFT技术尽可能早的发现有故障的芯片。  在这里插入图片描述 在这里插入图片描述三、测试的主要目的主要目的是确认芯片没有问题,问题来自两个方面:设计与制造 功能性问题:• 仿真 • 验证 • 功耗时序问题: • EDA分析辅助 工艺库问题:• 工艺库不准确, • 工艺的漂移 • 硅片的缺陷, • 生产环境问题, • 掺杂,溅射光刻等等问题 四、DPPM• 芯片从工厂里生产出来后通过机台产品测试把有缺陷的芯片找出来 • 产品测试就是在测试设备上,用测试向量来给芯片施加激励,通过比较输出结果来发现芯片的问题。 • 没有问题的芯片就可以输送给客户 • 但是有时有问题的芯片也可能通过测试,这称为“逃逸”片。“逃逸”片送到客户手中最终会造成很大损失。 • 所以新的概念用来评判测试品质:DPPM(defective parts per million) 五、为什么需要DFT• 芯片规模越来越大 • 测试数据越来越大 • 测试时间越来越长 • 复杂的SOC芯片架构 • 需要多种测试方法 • 内部有很多memory • 工艺尺寸越来越小 + 新材料 = 新的制造缺陷 • 传统的测试方法不能满足要求 • 互联越来越复杂 • 数百万上千万个晶体管 • 上亿个Via • 6km互连线/cm2 • 有限的IO PAD管脚 • 通过IO直接诊断越来越不可能 • 内部复杂的逻辑就像汪洋大海,通过IO PAD上的激励去定位一个故障犹如大海捞针

|

在这里插入图片描述

在这里插入图片描述

在这里插入图片描述

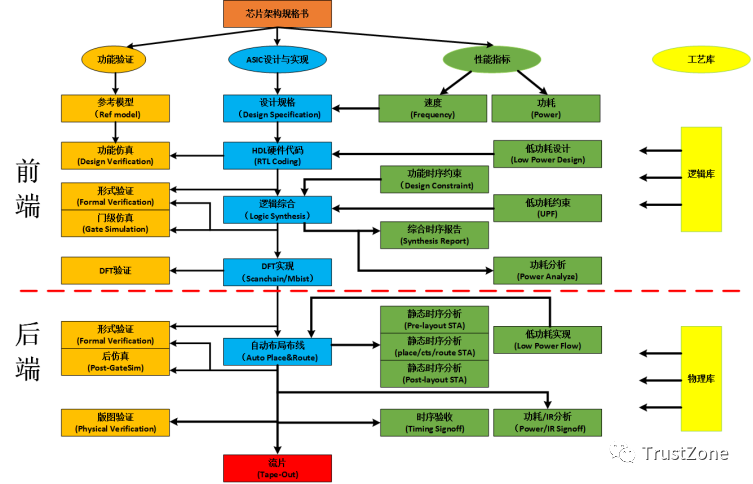

在这里插入图片描述 IC设计的流程

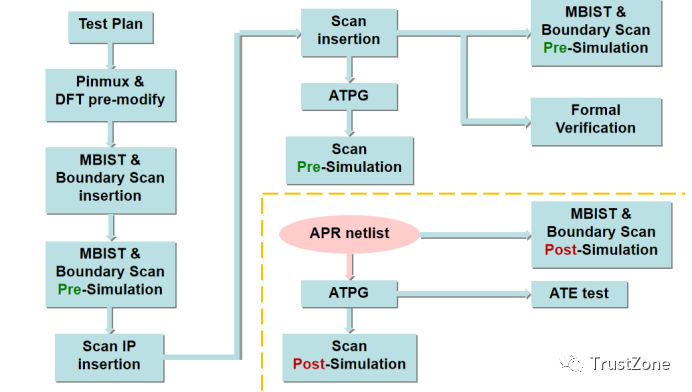

IC设计的流程 dft的设计流程

dft的设计流程 在这里插入图片描述

在这里插入图片描述 在这里插入图片描述

在这里插入图片描述