|

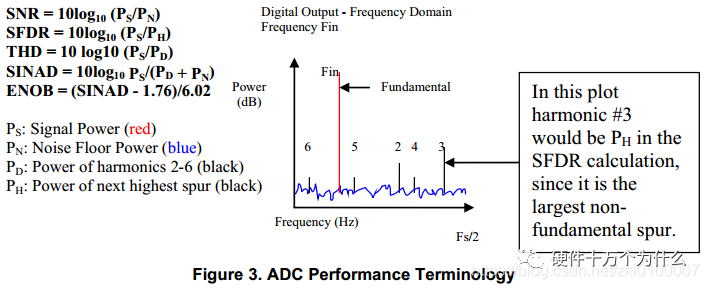

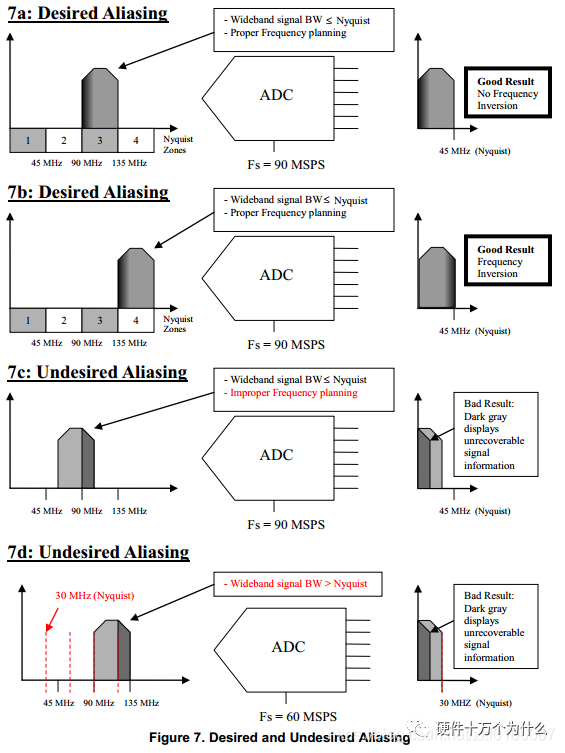

2. 频谱性能术语 SNR:信噪比,是指基频功率与除去直流及前5次谐波的噪底功率之比,有些数据手册可能是要除掉前9次谐波。基频也叫信号或者载波。SNR的单位是dBc(当用基频的绝对作参考时);或者dBFS。 SFDR:无杂散动态范围。SFDR是基频功率与最高的杂散功率之比。 THD:总谐波失真。THD是基频功率与前5次谐波功率之比。THD在单位通常是dBc。与SNR类似,有的数据手册可能取前9次谐波来计算THD。 SINAD:信号噪声与失真。SINAD的单位可能是dBc或者dBFS。 ENOB:有效位数。  理想SNR=6.02*n+1.76,当n=ENOB时,理想SNR=SNR。对于理想ADC而言,由于没有谐波,其SINAD=SNR。 例如,设计师需要一个SINAD为75dB的ADC,则ENOB=(75-1.76)/6.02=12.2bits,那么至少要选14位甚至16位的ADC才能满足要求。 3. 奈奎斯特、混叠、欠采样、过采样和带宽 根据奈奎斯特采样定理,采样时钟频率至少是输入模拟信号频率的2倍。 过采样:采样频率大于信号频率的2倍,即FIN<FS/2。FS/2即奈奎斯特频率。 欠采样:信号频率大于奈奎斯特频率。此时,会导致混叠。 混叠并非一无是处,它可以将高频信号混频到低频信号,可以省去额外的混频器,以减少系统功耗和成本,但前提是必须慎重考虑频率规划和ADC选型。  从上图可知,在ADC选型时,需要考虑如下两点: A:ADC满足期望的频率规划 B:输入模拟信号的带宽小于ADC的奈奎斯特频率 另外,ADC的带宽还要满足输入模拟信号的频率需求。 4.ADC管脚接口 一般来说,ADC包括以下6种接口:

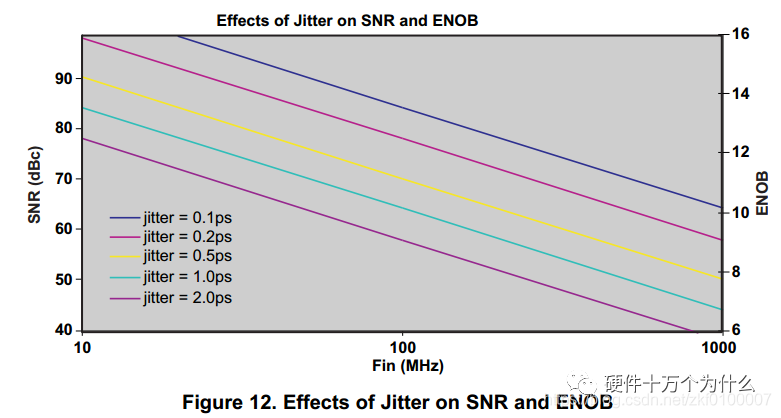

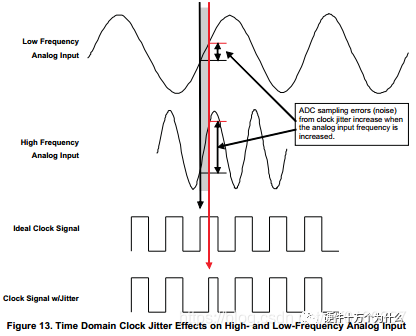

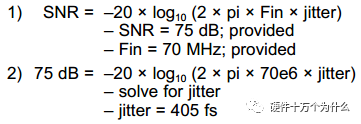

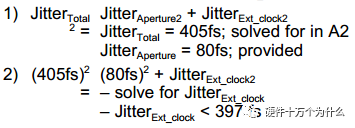

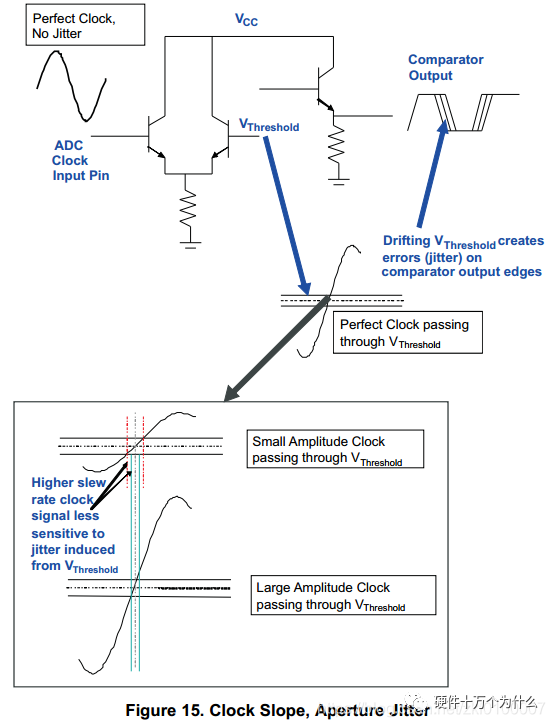

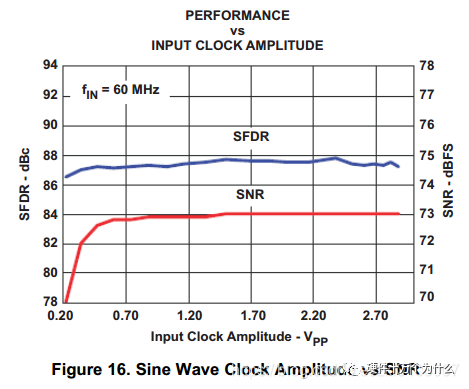

4.3时钟输入/抖动 高速ADC通常采用差分时钟输入。时钟抖动及斜率是影响ADC的SNR的重要因素。时钟抖动对SNR的影响如下所示:   由上可知,对于理想ADC,时钟频率并不会影响SNR。若不考虑时钟抖动,时钟频率达到ADC设计极限(诸如建立、保持或模拟建立时间),从而最终导致SNR下降。 抖动不变时,SNR随输入信号频率增加而降低。  由上图所示,指定时钟抖动时,SNR随信号频率增加而降低。高频模拟输入信号对于时钟抖动有较大的误差。如果时钟信号上有随机噪声,会表现在频谱图上。如果时钟信号上有确定的误差信号,这个信号会与ADC的输入信号混合在一起,在频谱图上表现为杂散。 设计师必须考虑时钟抖动的两个重要因素。其一是ADC的孔径延迟,其二是外部输入时钟的抖动。这两个因素共同产生的抖动影响ADC的采样误差。  设计实例: 设计需求如下: SNR=75dB FIN=75MHz 客户选定的ADC其孔径抖动=80fs 为了满足客户的SNR需求,客户应用所能容忍的最大抖动是多少? A:用公式3求解抖动  B:用公式4求解外部时钟抖动  因此,外部输入时钟抖动必须小于397fs。 下图展示了慢时钟沿导致较大的孔径抖动的情形。对于正弦时钟,增大时钟幅度可以改善孔径抖动进而提高ADC的SNR。  正弦波幅度与SNR的关系如下图所示:

|