|

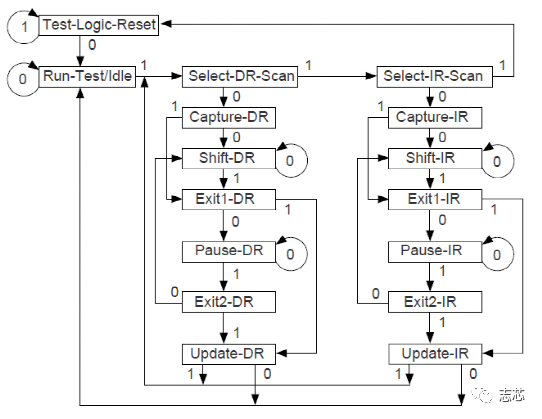

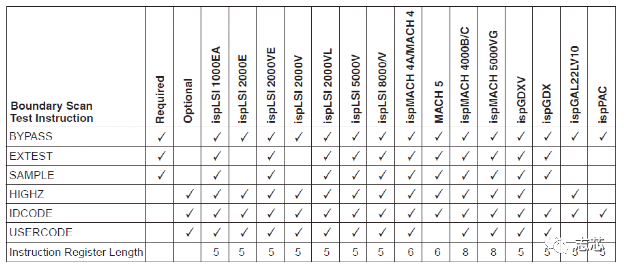

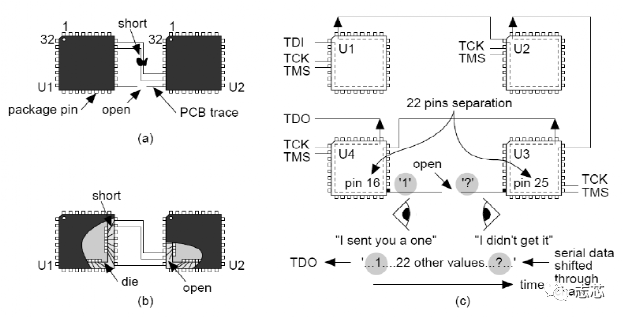

Boundary Scan中的reg ID CODE register:即身份辨别寄存器,身份辨别寄存器是一个32位的寄存器,它包含了元器件的一些制造信息。身份辨别寄存器也称ID CODE寄存器,因为ID CODE寄存器指令显示了身份辨别寄存器中的内容,并不是所有的boundary scan器件中都有身份辨别寄存器。 instruction register:即指令寄存器,包含了指令的解码,也包含了一些数据寄存所用的特殊指令。看起来似乎这不是一个单比特的寄存器。 ByPass register:即旁路寄存器,你可以使用ByPass寄存器通过那些没有被使用的Boundary –Scan寄存器链来进行数据传输的工作。假想你有一个很复杂的IC被用其它的技术象TEST JET之类的去测试而不用boundary scan,你也许会决定省略掉这个Boundary scan寄存器的长度并用单个单元的ByPass寄存器来代替,这样会节省测试时间。 Boundary Scan中的TAP控制器 TAP控制器是一种16位态的设备,它控制boundary scan测试的操作。由于TAP控制器 管理着大多数的数据和指令寄存器,理解TAP控制器在另一种意义上说等于理解了 Boundary scan, TAP控制器通过TCK,TMS,TRST*来实现控制。  图11 TAP的16位FSM示意图 虽然可以认为TAP 控制器是任何boundary scan器件的心脏,但指令寄存器和指令寄存器解码器可以认为是boundary scan器件的大脑。指令寄存器存储记录哪个test register或者test circuitry处于active状态等信息。对于选择的任何指令代码,test register或者test circuitry也被择。这是 IEEE 1149.1 标准中规定的要求之一。当 TAP 控制器处于 SHIFT-IR 状态时,指令移入指令寄存器,并在TAP控制器进入UDPATE-IR 状态时被激活。 TAP控制器的各种位态 Test-logic-Reset:在测试-逻辑-复位状态时,测试逻辑被禁用从而使此器件可以正常工作,当器件第一次被打开的时候,只要有ID寄存器存在,那个指令寄存器就会引入IDCODE指令,假如没有的话,会引入ByPass寄存器。一般的,测试-逻辑-复位在TAPcontroller 上电的时候才工作的,测试程序员能够通过使TRST*为低电平或使TMS为高电平并持续至少5个TCK周期来迫使TAP控制器进入上电的状态。 Run-Test/Idle: Run-Test/Idle允许在指令寄存器的指令的基础下激活被选种的测试逻辑电平,TAP controller 在TMS 保持低电平的状态下,会保持Run-Test/Idle的状态,而当TMS转换为高电平的时候,它转移到Select-DR-Scan上去。 Select-DR-Scan:这个TAP控制器扮演一个开关的角色,在下一个TCK的上升沿TAP控制器会开始数据寄存器的扫描或者转到Select-IR-Scan的状态上面。 Capture –DR: 在Capture –DR的状态时,夹具上连接到输入PIN的测试针的值,会替换一部分当前被指令选中的部分数据寄存器。并不是所有的指令都在这个状态做任何事,一些指令可以在数据寄存器现存的数据的基础上工作,TAP控制器会在一个时钟周期内保持这种状态,然后再转移到Exit1-IR或 Shift-IR。 Shift-DR: 在Shift-DR的状态,数据寄存器就好象一个转换寄存器在TDI和TDO数据之间并从TDI转移到数据寄存器然后再通过TDO在每一个TCK的上升沿从数据寄存器中出去。数据寄存器会保持这种状态直到TMS变为高电平,然后设备会转移到Exit1-DR的状态。 Exit1-DR :在到达Exit1-DR状态后,TAP controller转移到Pause-DR 或者Update-DR在TCK下一个上升沿,转到Update-DR时,扫描的过程就结束了,当移动到Pause-DR时可以暂停TAP controller的状态进程,此时可以允许测试机调用内存。 Pause-DR :当Pause-DR状态时,它允许一个暂停来通过指令寄存器来转换数据,一种情况是TAP controller执行其他的任务时可以使用此种状态,TAP controller会保持这种状态知道TMS变为高电平,然后TAP controller会转移到Exit2-DR状态。 Exit2-DR :在到达Exit2-DR状态之后,在下一个TCK的上升沿时TAP controller会转移到Shift-DR或Update-DR。转移到Shift-DR时会从新开始扫描,转移到Update-DR时中止扫描的进程。 Update-DR :在TCK的下降沿时,Update-DR状态从boundary scan寄存器锁住数据boundary scan寄存器的并联输出。在到达这个状态之后,状态设备转移到Run-Test/Idle或Select-DR-scan,当一个测试转移到Select-DR-scan时比转移到RUN-Test/Idle要快一个时钟周期,转到RUN-Test/Idle去压制ground bounce的影响是一个好办法。 Select-IR-Scan:TAP controller 充当一个开关的角色。在TCK下一个上升沿时,TAPcontroller开始IR扫描进程或者重置TAPcontroller到TEST-Logic-Reset状态。IR—SCAN进程放在TDI和TDO之间的指令寄存器中,并在下一个TAPcontroller指令中转换。 Capture-IR :Capture-IR状态在TCK的上升沿时从集成电路板上纳入一个逻辑电平到指令寄存器。一般都是01之类的信号,用于测试boudary-Scan 电路的完整性。其他的信号被设计员另外再特指标明或把值赋给变量,在Capture-IR状态待满一个时钟周期后,TAP controller转移到EXIT-IR或Shift-IR。 Shift–IR: 在Shift –IR的状态,指令寄存器在TDI和TDO之间扮演一个转换寄存器的角色,在Capture-IR抓到的数据在TCK的上升沿时转换到TDO并且一个新的指令从TDI转换进来。TAP controller直到TMS变为高电平才会改变状态到Exit1-IR. Exit1-IR:到达Exit1-IR 状态之后,在下一个TCK的上升沿时转换到Pause-IR或者Update-IR. 转移到Update-IR时中止扫描的进程。当移动到Pause-IR时可以暂停TAP controller的状态进程,此时可以允许测试机调用内存。 Pause-IR :当Pause-IR状态时,它允许一个暂停来通过指令寄存器来转换数据,一种情况是TAPcontroller执行其他的任务时可以使用此种状态,TAP controller会保持这种状态知道TMS变为高电平,然后TAP controller会转移到Exit2-IR状态。 Exit2-IR :在到达Exit2-IR状态之后,在下一个TCK的上升沿时TAP controller会转移到Shift-DR或Update-IR。转移到Shift-IR时会从新开始扫描,转移到Update-IR时中止扫描的进程。 Update-IR :在TCK的下降沿时,Update-IR状态latches the instruction register from the flip-flops into latches where the instruction decodeed,一旦一个新的指令被锁住它立刻转变为当前的指令。在到达这个状态之后,状态设备转移到Run-Test/Idle或Select-IR-scan,当一个测试转移到Select-IR-scan时比转移到RUN-Test/Idle要快一个时钟周期,转到RUN-Test/Idle去压制ground bounce的影响是一个好办法。 Boundary Scan Test Instruction 即Boundary scan中的各种指令。  图12 Boundary scan支持的各种指令框图 Bypass指令:放在一个单独的单元ByPass寄存器,在TDI和TDO之间,它并不象其他的测试一样去确认元件的放置和方向,在Bypass指令执行时,元件仍然保持正常的操作。根据IEEE 1149.1的标准,指令代码为1的必须解码为Bypass. EXTEST指令:是最有用的boundary scan的指令,因为它允许你在对元件的逻辑核心一无所知的情况下去测试所有的输入输出和双向引脚。EXTEST指令隔离了元件的逻辑核心测试,在元件的逻辑核心之外进行测试,他测试Boundary scan单元,引脚到板上的连接等等。 EXTEST指令有三种模式:标准-单独模式用于测试boudary 寄存器,和器件到板子上的连接情况。内部连接模式用于测试boudary 寄存器,和连接到boundary scan器件的电路。簇模式用于用于测试boudary 寄存器和在boundary scan器件和其它器件之间的电路。根据IEEE1149.1的标准,指令代码为0的必须解码为EXTEST。 Sample /preload指令:允许在元件正常工作的时候有有采样的输入和输出。然后Boundary scan测试可以对那些采样数据进行分析比并从TDO输出。当Boundary scan测试在转换采样数据并输出时,它可以通过TDI将采样数据预载到Boundary scan寄存器中,那些信号解码到Sample /preload指令并不属于IEEE1149.1标准,他们被元件设计师所制定。Sample /preload指令的预载功能是用来准备那些例如EXTEST的指令的,例如,假想一个芯片选择器件如下图它连接了两个ROMS并共享了一个输出BUS,在这个事例中你可以使用preload来确保芯片选择器件的输出不会同时出现高电平而导致BUS竟争。 IDCODE指令:被放在TDI和TDO之间的寄存器中间,由于在这里面放了元件的制造信息,所以可以通过此指令来辨别WRONG PART。 USERCODE指令:允许测试开发人员登入一个32位的代码从而可以被转换并输出用于校验。这个指令是根据有设计人员的定义来定的,并且它依赖于身份辨别寄存器的存在而存在。 Intest指令: Intest对元件的内部逻辑进行静态的测试,在进行静态的测试的时候,这些测试并不是在元件固有的测试速度下进行的,而是在TCK的单步测试模式下进行的。这种测试不会受元件的拓扑结构的影响。它的测试结果从TDO输出。 RUNBIST指令:是使元件进行自测的指令,当元件执行BIST时,TAP控制器处于RUN_TEST/IDLE状态。它测试的结果从TDO输出。同样这个测试不会受元件的拓扑结构的影响。 Clamp指令: CLAMP是一个设计人员定义的代码,它能设置所有的系统逻辑输出和双向引脚从Boundary scan寄存器中锁住一个常量值。在此指令执行的时候,处于TDI和TDO之间的ByPass寄存器在SHIFT-DR控制的状态。 HIGHZ指令: 是一个设计人员定义的代码,它能设置所有的系统逻辑输出和双向引脚到一个高阻状态。这就能允许测试机在不损坏元件的前提下去驱动信号到元件的输出和双向引脚上。在此指令执行的时候,处于TDI和TDO之间的ByPass寄存器在SHIFT-DR控制的状态。 Boundary Scan的优缺点 优点:可以使用来自不同供应商的混合组件;为内部电路提供了很好的接口;得到了来自EDA厂商,IC制造商,FPGA制造商的广泛支持;允许测试版和系统互连;高故障覆盖率;提供组件级故障隔离;支持实时采样;在晶圆测试中很有用(需要更少的探针);重新配置 了Boundary scan路径以绕过 IC 逻辑从而加快访问速度;等。 缺点:引入了额外逻辑;所有输入和输出引脚上的 1 个 MUX 延迟;无法以系统时钟速度测试;等。 boundary scan tools Corelis — ScanPlusTPG Teradyne — Victory Acculogic — ScanManager Goepel Electronic — System Cascon Asset InterTech — ScanWorks Intellitech — Eclipse Test Development Environment Flynn Systems — onTAP. boundary scan的应用  图13 用boundary scan测试IC接口的短路开路示意图 除了测试接口见的短路开路以外,常见应用还可大致总结如下。       部分参考文献 外文文献: 《Boundary-Scan Tests for ICs and PCB Assemblies》;作者:AMOS Kingatua; 《Boundary Scan Tutorial》;作者:CORELIS; 《Introduction to Boundary Scan Testand In-System Programming》;作者:latticesemi; 《Testing and Boundary Scan》;作者:未知; 中文文献: https://wenku.baidu.com/view/b2671e641ed9ad51f01df251.html;作者:coouoo; https://max.book118.com/html/2017/0502/103756660.shtm;作者:未知; |