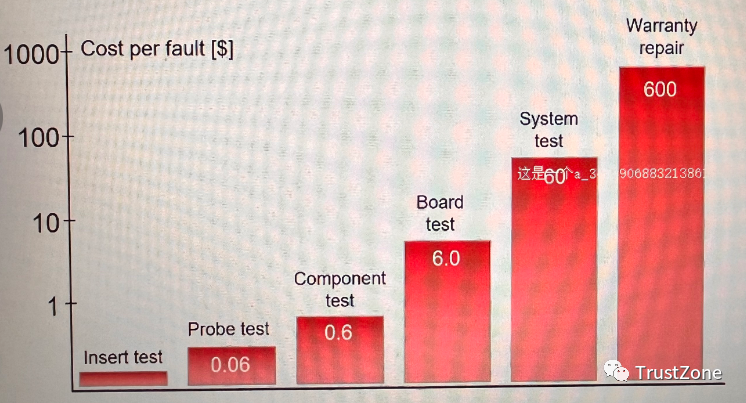

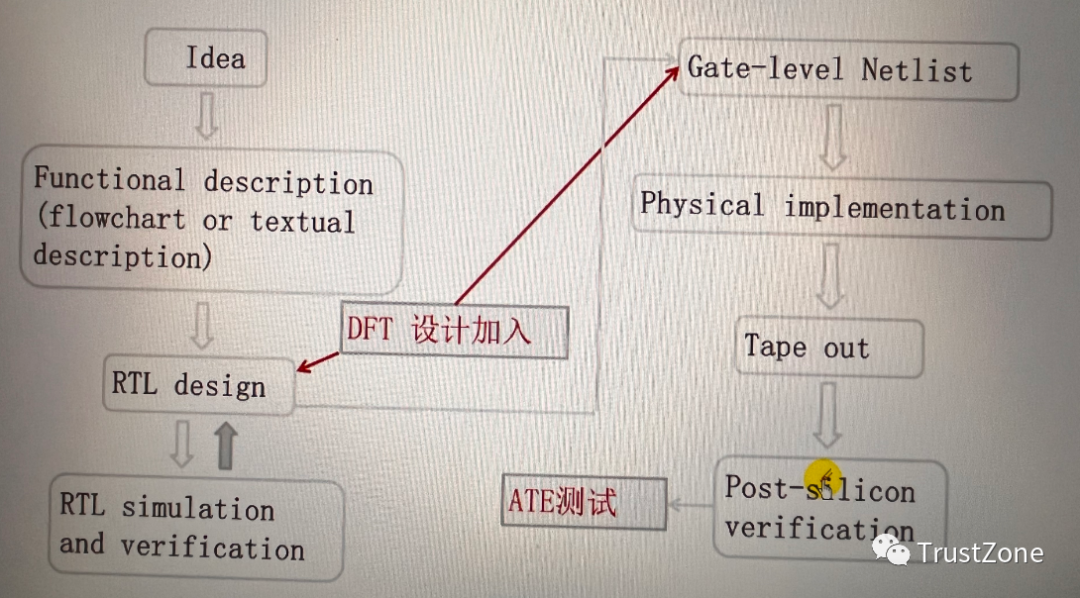

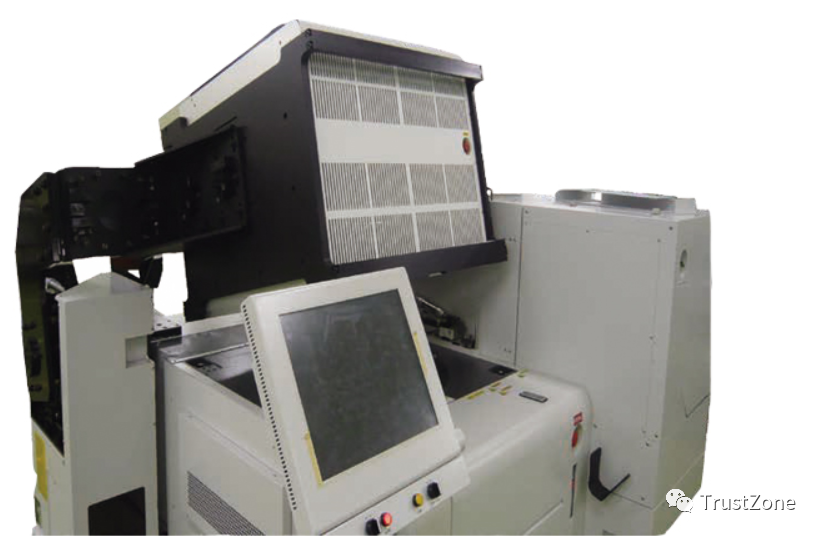

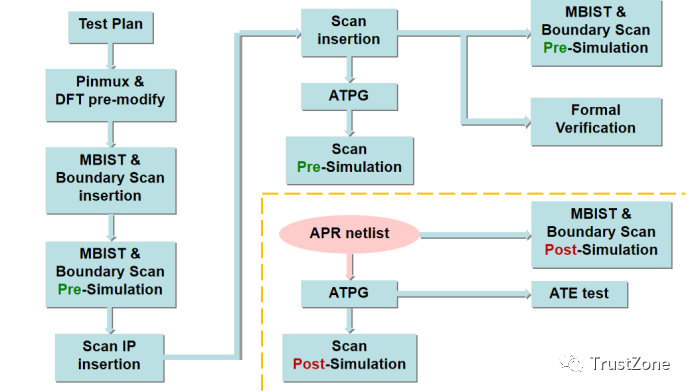

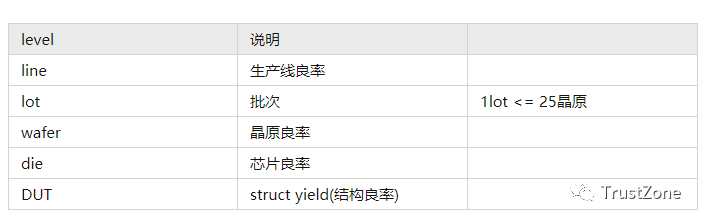

前段时间还记得我们一起看了OPENJTAG,后面我对那几个扫描链路比较感兴趣,于是顺便来来一起了解一下DFT吧。一、什么是DFT?• DFT(Design for Test),即可测性设计 • 一切为了芯片流片后测试所加入的逻辑设计,都叫DFT。 • DFT只是为了测试芯片制造过程中有没有缺陷,而不是用来验证芯片功能的。芯片功能的完善应该应该是在芯片开发过程用先进验证方法学去做的。 • 芯片制造过程相当复杂,工艺缺陷难免会存在,DFT的目的就是从制造完成的芯片里挑出有缺陷的芯片,以免有缺陷的芯片到了客户于上,造成更大的经济和时间损失。 二、测试的重要性在某层测试上漏掉了一个有故障的芯片,可能在下一层测试上需要花费10倍的cost才能发现它,所以,需要依赖DFT技术尽可能早的发现有故障的芯片。  在这里插入图片描述 三、测试的主要目的主要目的是确认芯片没有问题,问题来自两个方面:设计与制造 功能性问题:• 仿真 • 验证 • 功耗时序问题: • EDA分析辅助 工艺库问题:• 工艺库不准确, • 工艺的漂移 • 硅片的缺陷, • 生产环境问题, • 掺杂,溅射光刻等等问题 四、DPPM• 芯片从工厂里生产出来后通过机台产品测试把有缺陷的芯片找出来 • 产品测试就是在测试设备上,用测试向量来给芯片施加激励,通过比较输出结果来发现芯片的问题。 • 没有问题的芯片就可以输送给客户 • 但是有时有问题的芯片也可能通过测试,这称为“逃逸”片。“逃逸”片送到客户手中最终会造成很大损失。 • 所以新的概念用来评判测试品质:DPPM(defective parts per million) 五、为什么需要DFT• 芯片规模越来越大 • 测试数据越来越大 • 测试时间越来越长 • 复杂的SOC芯片架构 • 需要多种测试方法 • 内部有很多memory • 工艺尺寸越来越小 + 新材料 = 新的制造缺陷 • 传统的测试方法不能满足要求 • 互联越来越复杂 • 数百万上千万个晶体管 • 上亿个Via • 6km互连线/cm2 • 有限的IO PAD管脚 • 通过IO直接诊断越来越不可能 • 内部复杂的逻辑就像汪洋大海,通过IO PAD上的激励去定位一个故障犹如大海捞针 六、加入DFT逻辑后的影响Cost• development • application Impact• performance degradation • area overhead Quality• defect level • fault coverage 七、DFT在整个芯片设计流程中所处的阶段 在这里插入图片描述 八、常见的芯片制造故障(缺陷)制造过程中,由于粉尘污染,工艺偏差等因素,造成以下常见故障: • 短路 (short) • 断路 (open) 1. Stuck-at fault • 2.Transition fault 1. Bridge fault 九、DFT通常包括哪些技术1、Scan and ATPG(自动测试向量产生) • 用来测试芯片中的组合和时序逻辑 • 2.Mbist • 用来测试芯片中的Ram,Rom • 3.Boundary scan(TAP) • 主要用来测试芯片间互联 十、ATE (Automatic Test Equipment)测试 在这里插入图片描述 • 测试准备: • 2.测试向量 • 3.待测芯片 (通常加载到loading board上) 1. ATE 加载到loading board说明已经FT封装了 如果用probecard去测试说明在wafer die上去测试。 • 测试结果. • 1.Fail-> 进一步诊断或丢弃 • 2.Pass -> 进行后续流程 • 测试周期: • Wafer阶段测试:ATPG,Lbist, mbist • 封装后测试:ATPG,Lbist, mbist • PCB板级测试:Boundary scan, Lbist, mbist 十一、测试诊断分析 (Diagnosis) 在这里插入图片描述 十二、IC设计的流程 IC设计的流程 十三、dft的设计流程 dft的设计流程 名词1-yield在半导体生产制造的各个环节,都可能会引起最终产品的失效。yield(良率,合格率)是一个量化失效的指标,通常也是工艺改善最 重要的指标。图17.1所示为半导体生产环节中的各种yield。 在这里插入图片描述 在半导体生产制造中,yield的定义为  在这里插入图片描述 yield可以基于晶粒(die)或者晶片(wafer)或者批次(lot)定义。 定义在wafer或者lot上的yield,一般反映生产工艺中的控制问题, 如操作人员的误操作,设备故障等,通常也称为生产线良率(line yield)。例如,生产线下线1000片wafer,最后由于各种原因报废 (scrap)20片wafer,那么line yield就等于98%。  在这里插入图片描述 机制分类对于工艺引起的yield loss,按照失效的特征分为两大类: 参数性 (parametric)和功能性(functional)失效。一般的理解, • 功能性失效,往往由于物理缺陷引起,习惯上也被称为hard fail或者缺陷性失效; • 参数性失效,往往由于器件电参数的不优化或者漂移超出规格引起,习惯上也被称为soft fail。 对于功能性失效,根据在wafer表面的空间分布特征(spatial distribution),又可分为随机性(random)和系统性(systematic)失 效。 2-ATPG扫描测试(又叫ATPG)。scan path。与边界扫描测试的区别,是内部移位寄存器实现的测试数据输入输出。测试目标是std-logic,即标准单元库。(扫描测试和边界扫描,不是一个概念。需要区别对待。内部的触发器,全部要使用带SCAN功能的触发器类型。) 3-Boundary scan• Boundary scan:边界扫描测试;boundary scan test。测试目标是IO-PAD,利用jtag接口互连以方便测试。(jtag接口,实现不同芯片之间的互连。这样可以形成整个系统的可测试性设计。) 4-Lbist• Lbist:LBIST 是一种内置自测 (BIST) 形式,其中芯片内部的逻辑可以在芯片本身上进行测试,而无需任何昂贵的自动测试设备 (ATE)。BIST 引擎内置于芯片内部,只需要像测试访问端口 (TAP) 这样的访问机制即可启动。Lbist的组成部分 片上lbist一般由三部分组成:BIST controller、TPG (Test Pattern Generator)、RA (Response Analyzer)。 5-mbist• mbist:内建自测试BIST;(模拟IP的关键功能,可以开发BIST设计。一般情况,BIST造成系统复杂度大大增加。memory IP一般自带BIST,简称MBIST) 6-loading boardloading boardLOAD BOARD通常用于测试半导体器件的电气特性,例如电流、电压、功率等。它是连接测试设备和被测试芯片的桥梁,通常包括一些接口,例如引脚插座、测试点和电源接口等。LOAD BOARD的设计必须与被测试器件的引脚布局相匹配,以确保测试结果的准确性和可重复性。 7-BURN IN BOARDBURN IN BOARD则用于加速半导体器件的老化过程,以检测器件在长期使用中的可靠性。它通常包括一个温度控制系统,用于控制被测试器件的环境温度。BURN IN BOARD还可以模拟真实世界的使用条件,例如高温、低温、高压和高湿等。因此,LOAD BOARD和BURN IN BOARD的主要区别在于它们的用途。LOAD BOARD主要用于测试器件的电气特性,而BURN IN BOARD则用于测试器件在长期使用中的可靠性。 |