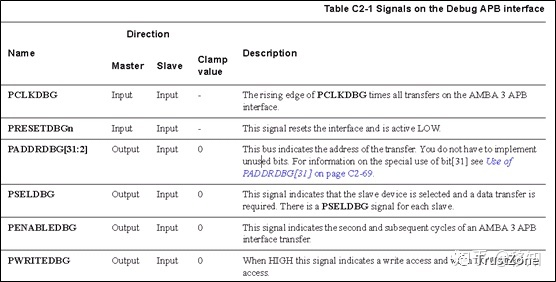

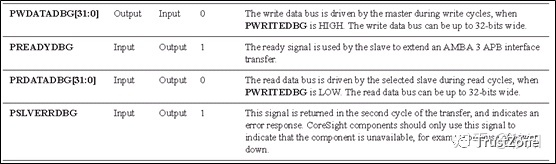

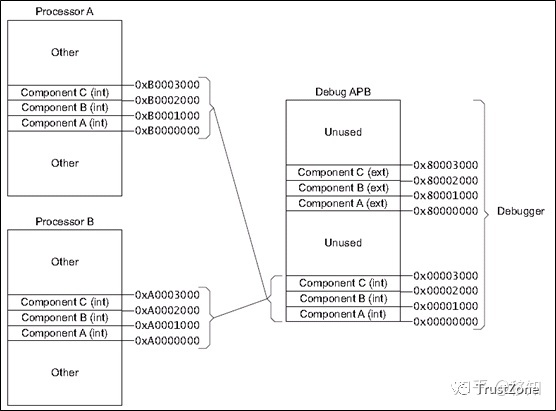

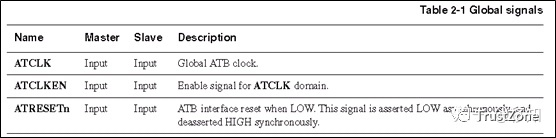

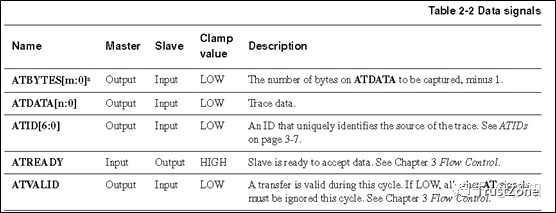

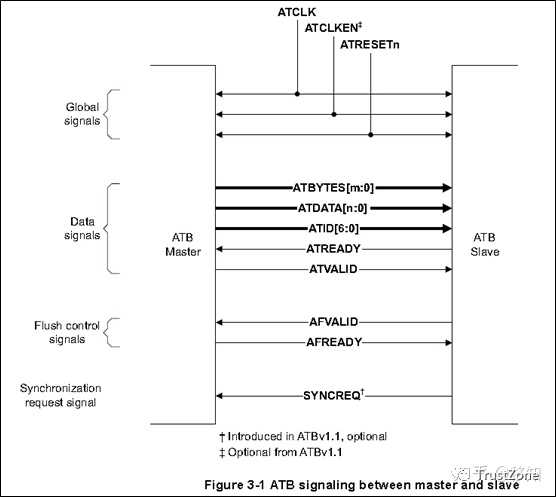

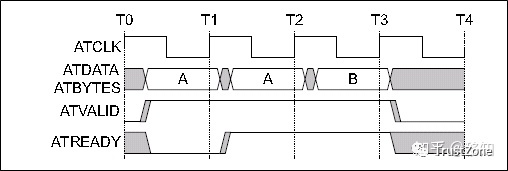

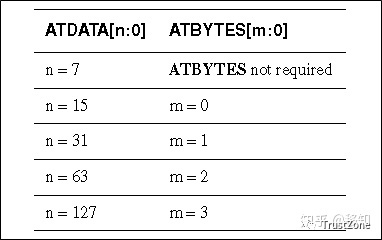

PerfaceAPB和ATB总线,是coresight中常用的2个总线。• 对于coresight组件的访问,使用debug APB总线进行访问。 • 而对于trace数据的传输,使用ATB总线进行传输。 APB总线以下是信号列表。  • clamp value,是指当一个组件是power down或者是disabled,输出的固定值。 • APB访问,数据最多是32bit,也就是coresight组件的寄存器的位宽最多是32bit的。 对于PADDRDBG[31],地址的最高位,表示当前的访问是internal access,还是external access。 • internal access,是指处理器执行指令的访问,比如load/store去访问,或者是外部debugger通过memory map的访问。 • external access,是指外部的访问,比如debugger,external access比internal access有更高的权限。 如下图,两个处理器,均有自己的coresight组件。每个组件的地址是不一样的。 对于外部的debugger而言,使用地址0x8000_0000和地址0x0000_0000都是访问的同一个coresight组件的寄存器,要不就是处理器A的组件A,要不就是处理器B的组件A。 这就是为什么Trace32需要设置一下Corebase,选择debug哪个Core。 但是如果debugger使用地址0x0000_0000访问,是internal access,此时受限于software lock的影响。 而使用地址0x8000_0000访问,是external access,不受限于software lock。  ATB总线ATB总线用来coresight组件之间传递trace信息用。包括两部分:• master: 在ATB总线上产生trace信息的接口。 • slave: 在ATB总线上接收trace信息的接口。 ATB总线以AT作为信号的前缀。 如以下:HTM和xTM是产生trace信息的master,通过ATB总线,发送给funnel,funnel将收到的两路ATB数据合并成一路ATB数据发送给replicator,replicator再将接收的一路ATB数据,重复以两路ATB数据分别发送给ETB和TPIU,TPIU通过trace port发送到外部。  trace信息,通过ATB总线进行传输。 • ETB: embedded trace buffer。 片内存储trace数据的大容量设备。 • xTM:trace macrocells。 从连接的处理器中,追踪数据,产生trace信息输出。 包括两个: • ETM: embedded trace macrocell,可以产生指令trace信息,也可以产生数据trace信息 • PTM:program flow macrocell,产生指令trace信息 • HTM: advanced high-performance bus trace macrocell。 连接到AHB互联总线上,产生总线的trace信息 • TPIU: trace port interface unit。接收ATB trace数据,传输到trace port上,将trace信息输出到片外。 • trace replicator: 将一个ATB数据发送给独立的两个ATB slave。 • trace funnel: 将多个trace源信息,合并成一个trace数据输出。 全局信号时钟和复位信号。复位信号低电平有效。数据在时钟的上升沿采样。 flow control数据信号。 master和slave之间的通信,通过ATVALID和ATREADY作为握手信号。  master将ATVALID拉高,表示master传输的数据有效。 slave将ATREADY信号拉高,表示slave准备好接收master的数据。 如果master发送数据,发现slave的ATREADY没有拉高,那么就要将数据重新发送一遍。 时序图如下:  • T1,master发送数据A,ATVALID拉高。但是master检测到ATREADY没有拉高。 • T2,master检测到上一次数据传输,ATREADY没有拉高,因此需要将数据A重新发送。此时ATREADY为1,表示此时数据发送成功。因此下一次可以发送新的数据。 • T3,master发送数据B,ATREADY为1,表示此时数据发送成功。下一拍可以发送新的数据。 • T4,master将ATVALID拉低,表示没有数据发送。 如果slave在master发送数据的时刻,不能及时接收master发送的数据(ATREADY不能在master发送数据时刻拉高),那么在slave端,建议实现internal buffer,接收master发送的数据。 然后再处理。这样的话,当buffer没有满的话,ATREADY信号就可以一直为高,master就不用一直重新发数据。 对于ATBYTES[m:0] 和 ATDATA[n:0]。 m = log2(n+1) – 4  对于ATID: trace的数据要伴随着ATID进行发送的。因为产生trace的组件有很多,因此需要一个ID来识别这些组件,ID就保存在ATID中发送。 ATID是一个7位的值。0x00和0x70-0x7f是coresight中规定的保留值,在soc实现中,coresight trace组件不应该使用这些ID。 在一个soc中,对于每个trace组件,ID必须是唯一的。对于ID,有两种选择: • fixed ID:在soc设计的时候,就将ID值给固定了。 • programmed ID: trace组件的ID可以通过外部的debugger进行更改,但是debugger要保证,组件的ID必须是唯一的。 ATID和ATDATA,在同一时刻被slave所接收。 flusing一般,trace数据都是从trace source发送到trace sink。但是在某些情况下,trace sink需要主动要求trace source发送数据,此时就会用到flusing。 sink发送flush信号给source,source将内部所有的trace数据全部发送出去,发送完毕后,回应sink flush complete信号。 flush使用以下两个信号来作为握手信号。  如下图:trace source追踪处理器的数据,通过trace generation,发送到下一级的buffer中,然后buffer将数据发送给FIFO中进行暂存。 FIFO中一旦有数据,FIFO就负责将数据通过output发送给trace funnel。 因此对于一个trace组件,中间是会存在多级的buffer对数据进行缓存的。  假设此时系统要power down,而source的FIFO中还有trace信息,那这些trace信息,就要在power down之前,发送出去。 此时funnel就可以向source发送flush信息,也就是将AFVALID信号拉高,trace source接收到该信号,就将自己FIFO中的所有剩余trace信息,全部发送给funnel,发送完毕后,将AFREADY信号拉高,表示数据发送完毕。 此时,就可以将系统给power down。 时序图:  • T1时刻,AFVALID为高,表示要求master进行flush操作。 • T2开始,就进行master的FIFO的trace数据排空操作。 • 从T2-T6,master将自己内部的FIFO数据发送出去。 • 在T6时刻,master将AFREADY信号拉高,表示master将数据发送外部,也就是flush完成。 |