|

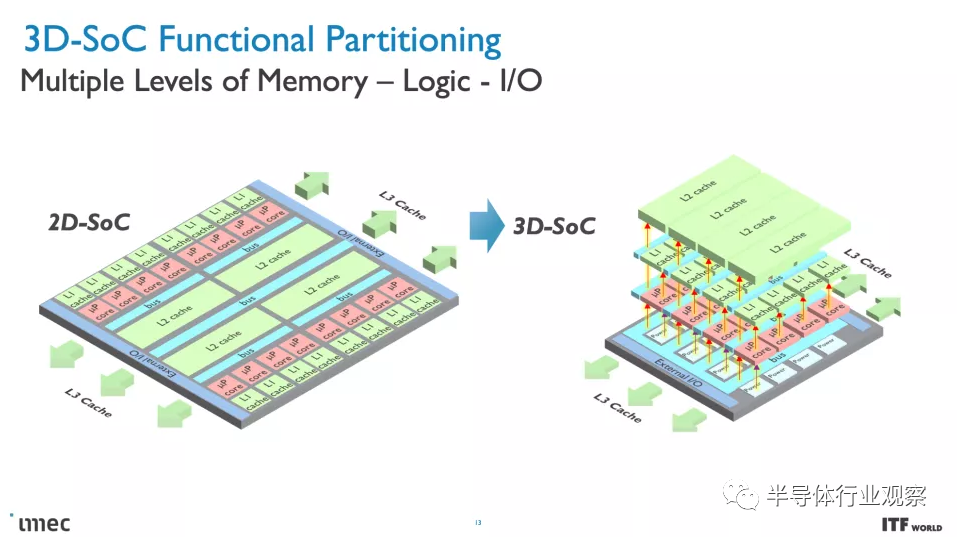

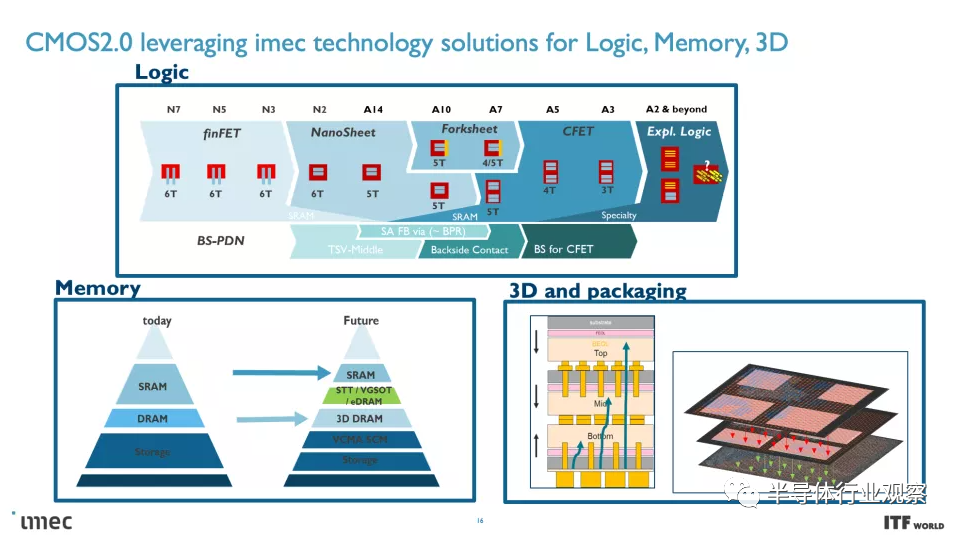

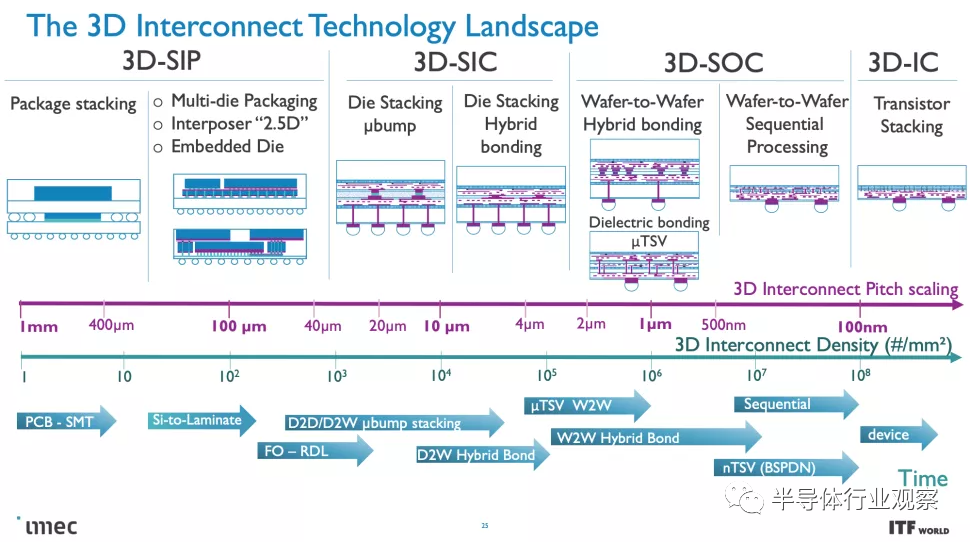

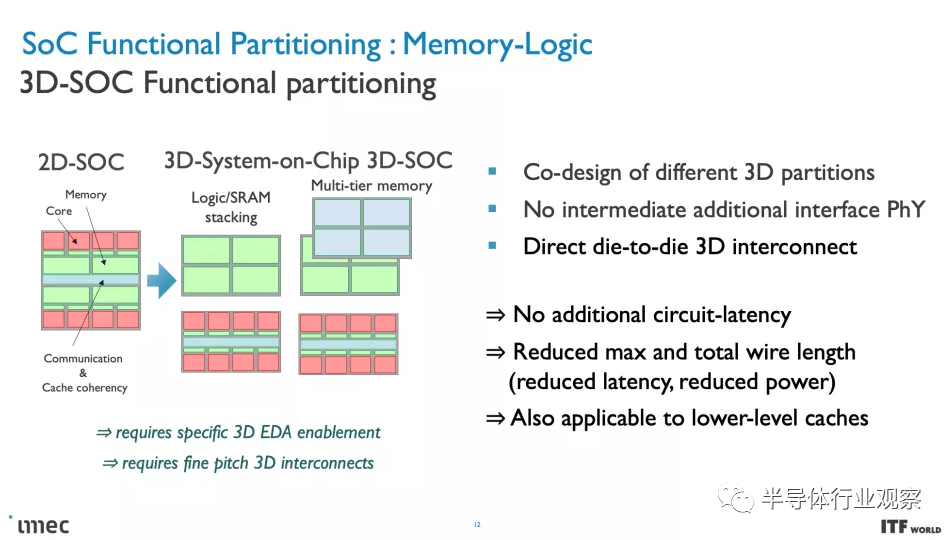

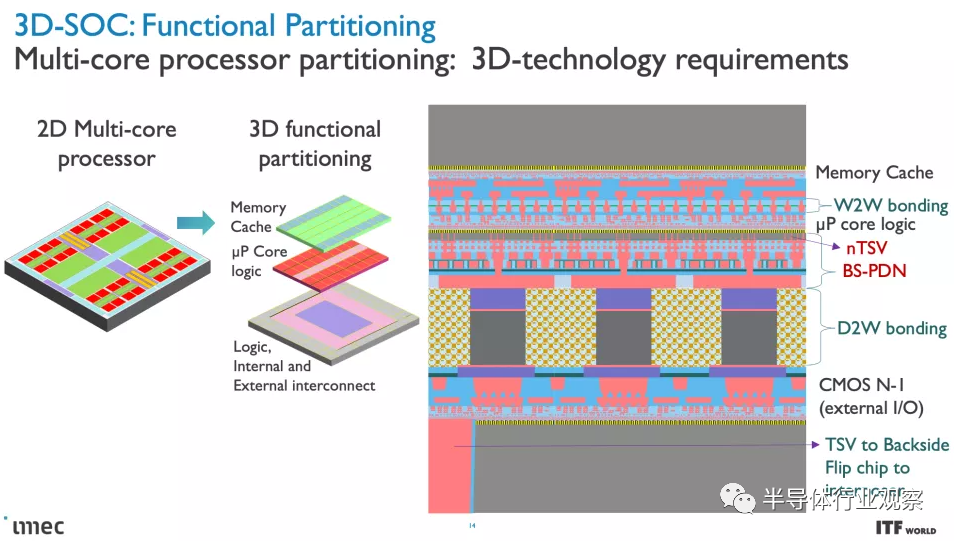

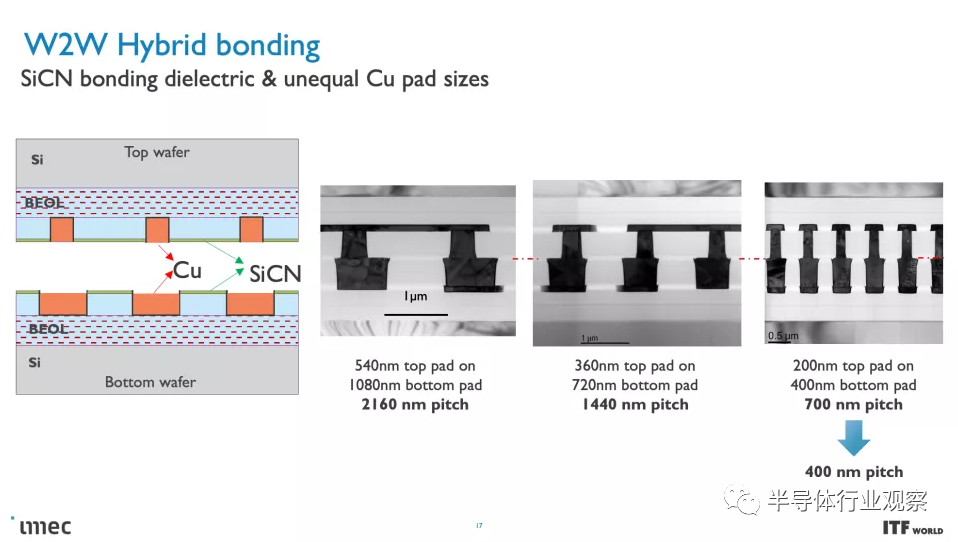

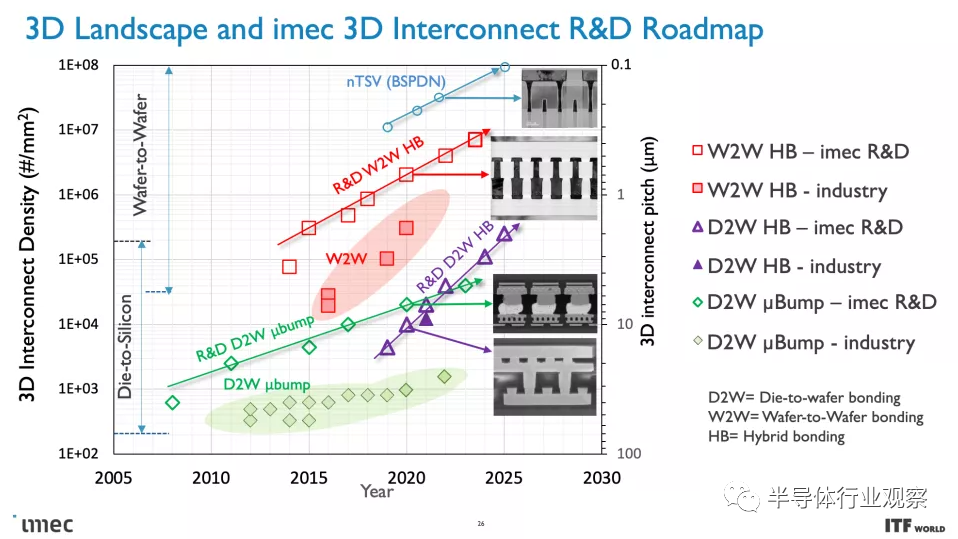

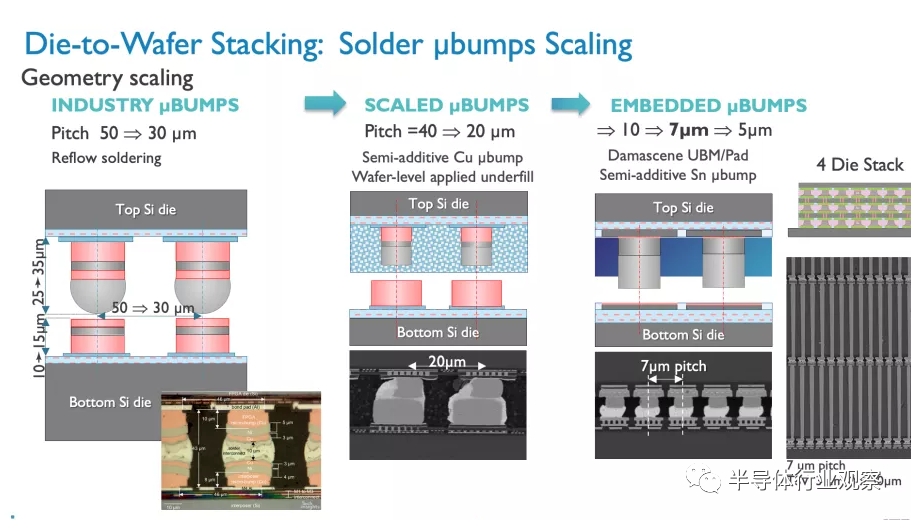

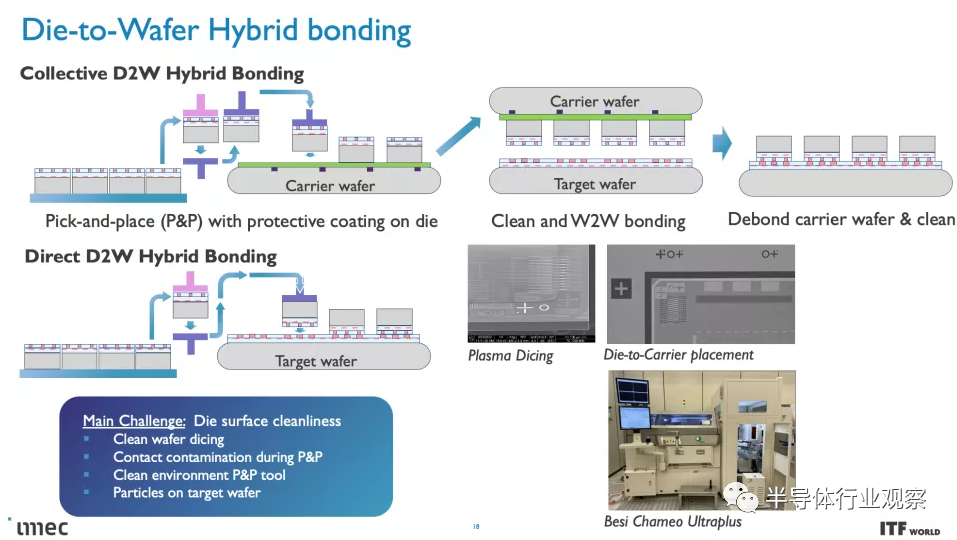

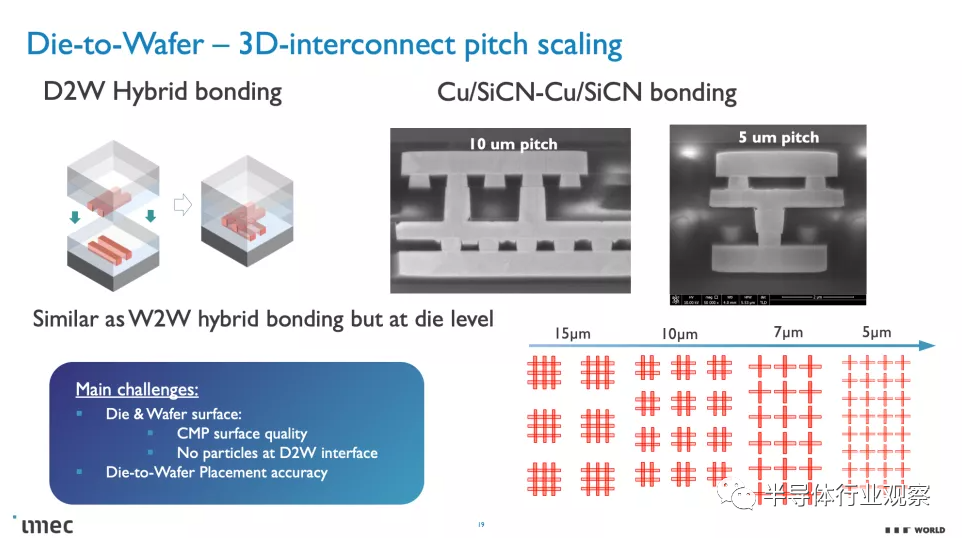

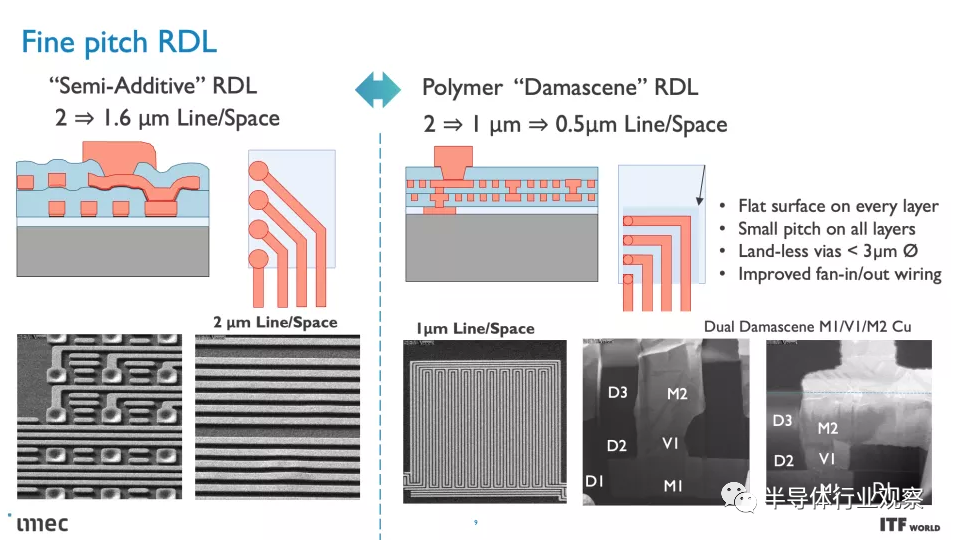

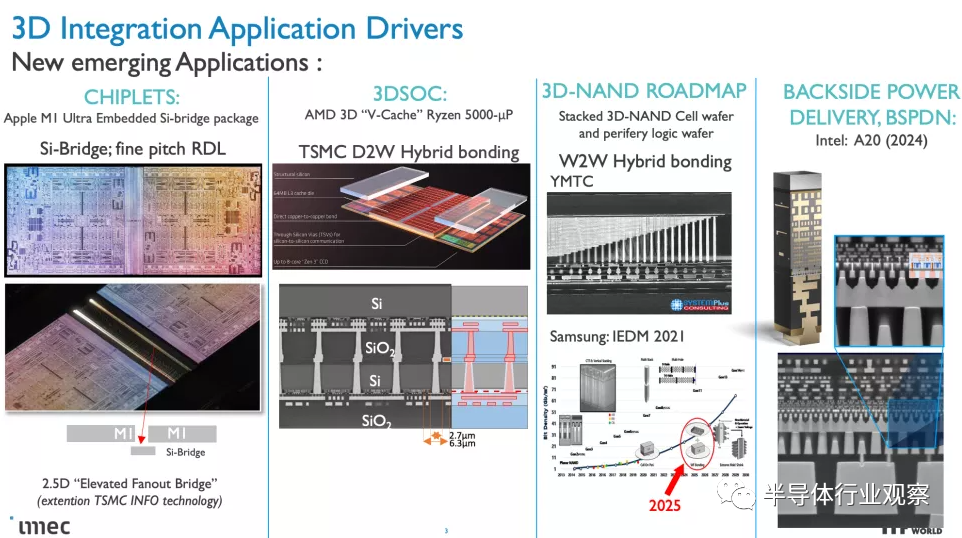

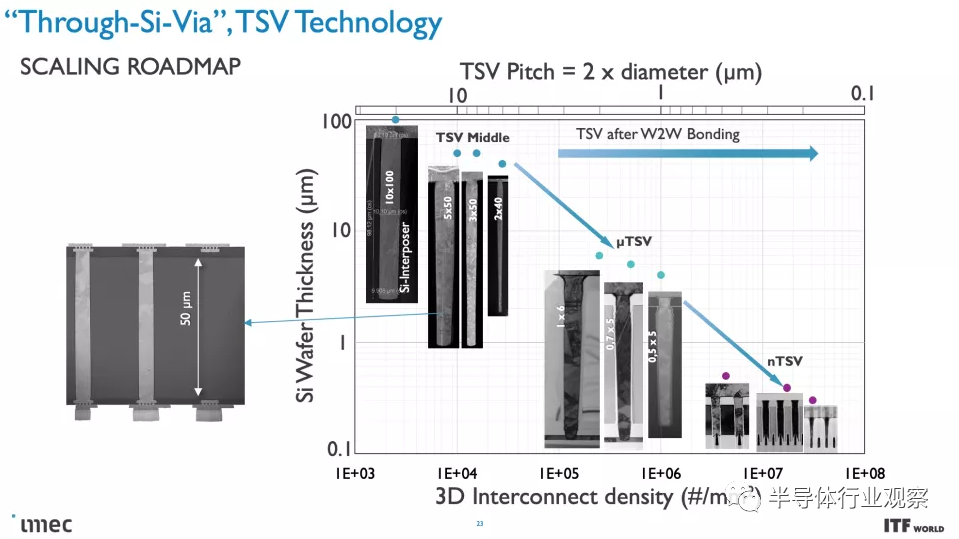

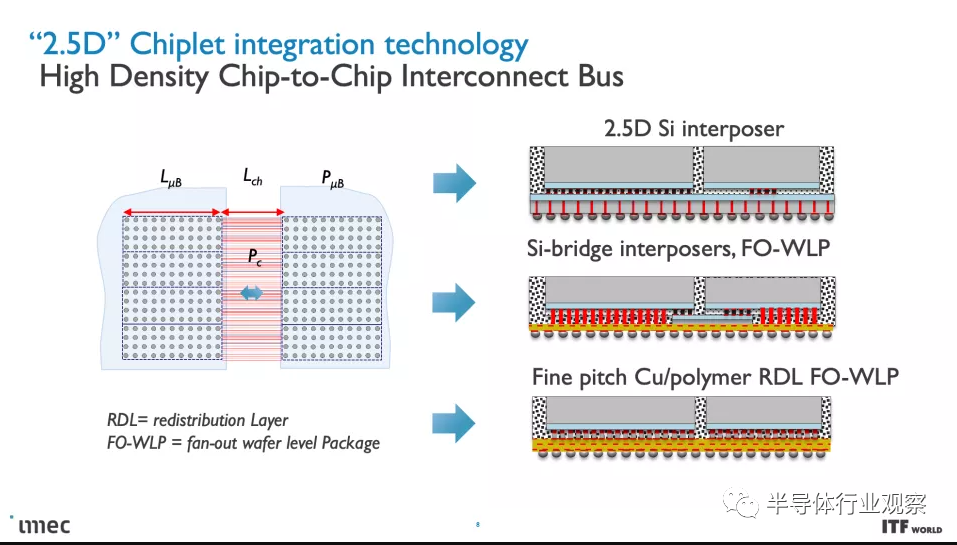

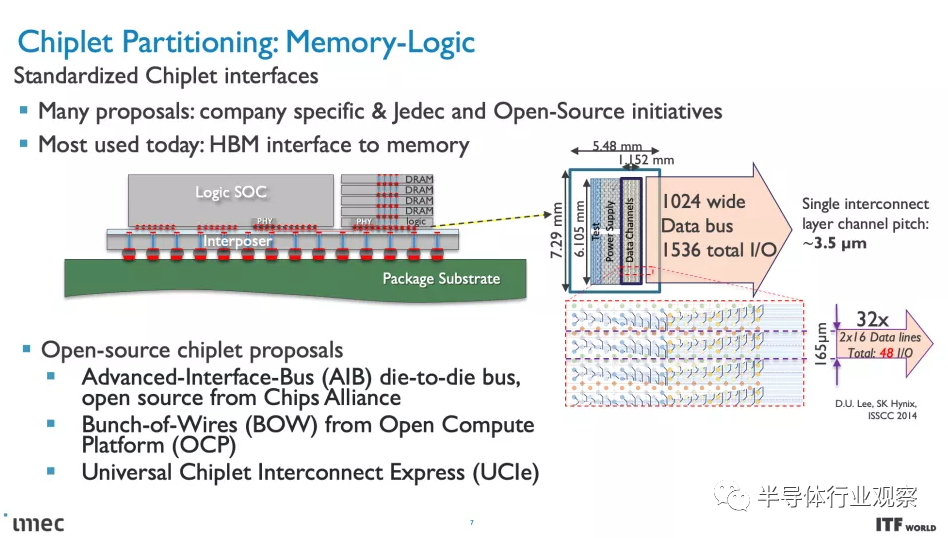

CMOS 2.0:真正的3D芯片之路 CMOS 2.0 是 imec 对未来芯片设计愿景的巅峰之作,涵盖了全 3D 芯片设计。我们已经看到 AMD 第二代 3D V-Cache 的内存堆叠,将 L3 内存堆叠在处理器之上以提高内存容量,但 imec 设想整个缓存层次结构包含在其自己的层中,具有 L1、L2 和 L3 缓存垂直堆叠在构成处理核心的晶体管上方的自己的芯片上。每个级别的缓存都将使用最适合该任务的晶体管创建,这意味着 SRAM 的旧节点,随着SRAM 缩放速度开始大幅放缓,  这变得越来越重要. SRAM 缩小的规模导致缓存占用了更高比例的裸片,从而导致每 MB 成本增加,并阻碍了芯片制造商使用更大的缓存。因此,将 3D 堆叠的缓存转移到密度较低的节点所带来的成本降低也可能导致比我们过去看到的缓存更大的缓存。如果实施得当,3D 堆叠还可以帮助缓解与较大缓存相关的延迟问题。  这些 CMOS 2.0 技术将利用 3D 堆叠技术(如晶圆到晶圆混合键合)来形成直接的芯片到芯片 3D 互连。  正如您在上面的专辑中看到的那样,Imec 也有一个 3D-SOC 路线图,概述了将 3D 设计结合在一起的互连的持续缩小,从而在未来实现更快、更密集的互连。这些进步将在未来几年通过使用更新类型的互连和处理方法来实现。              |