|

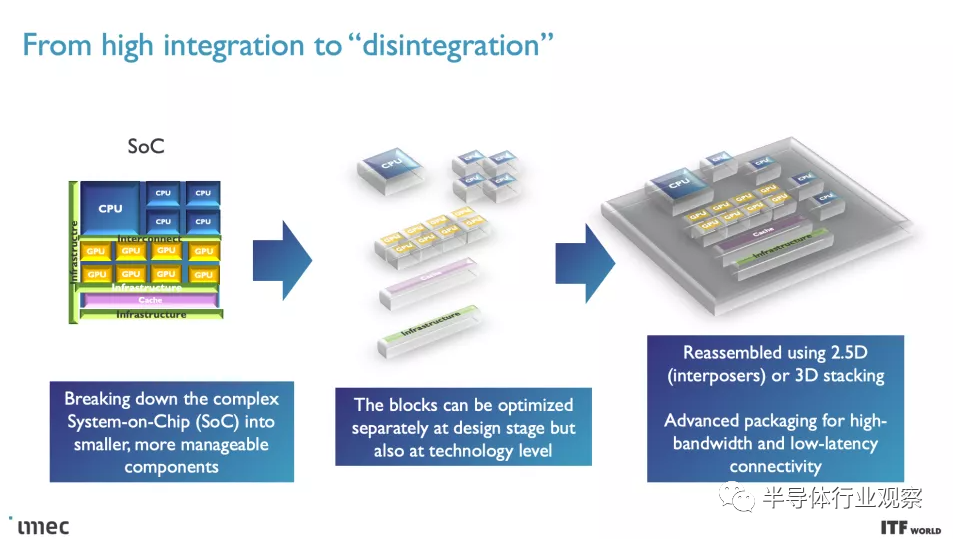

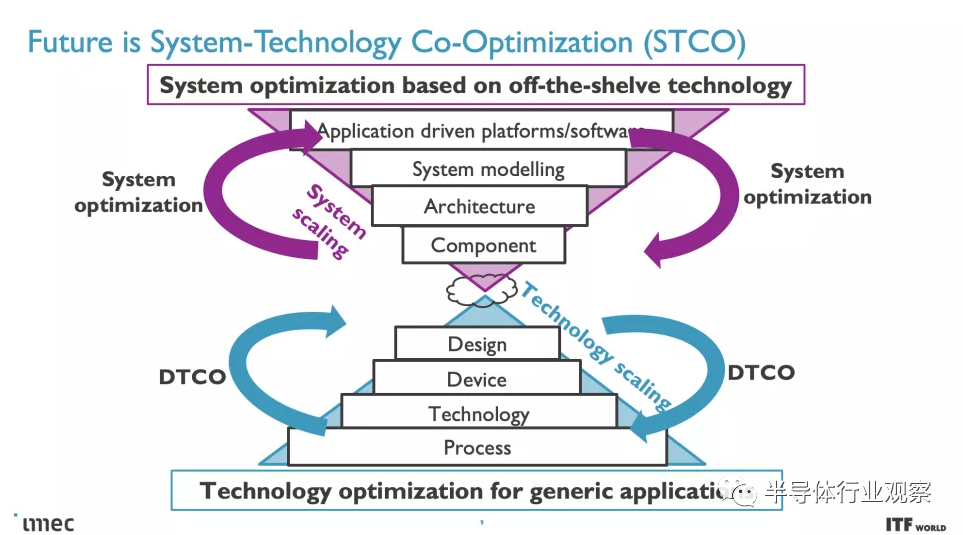

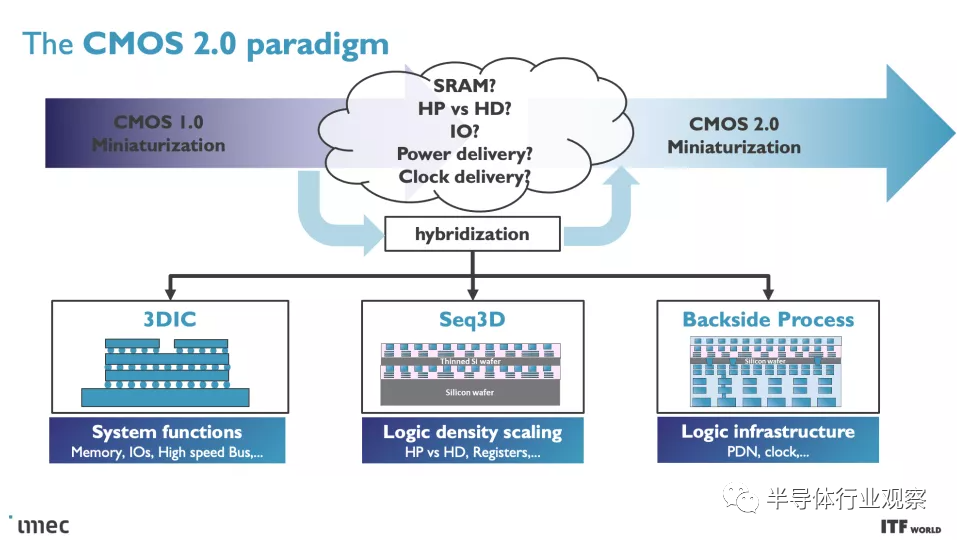

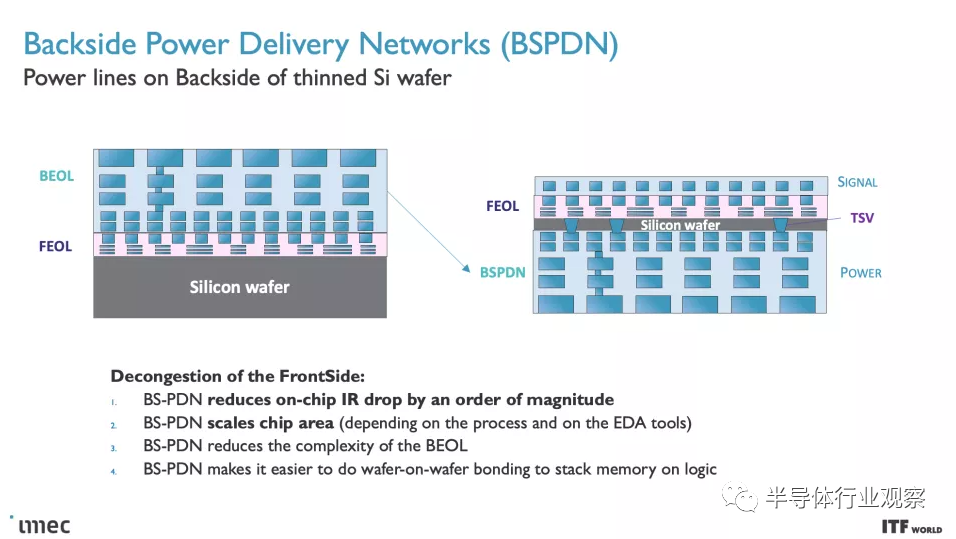

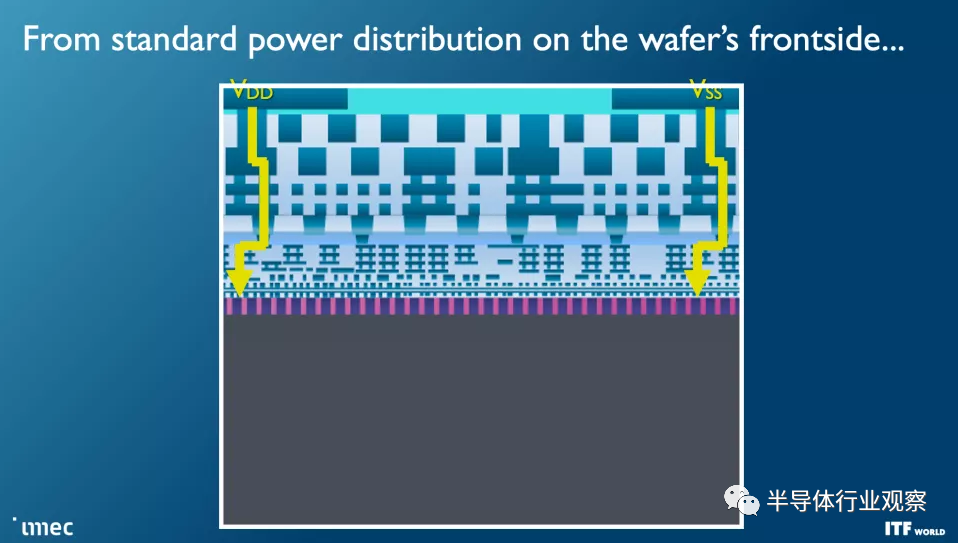

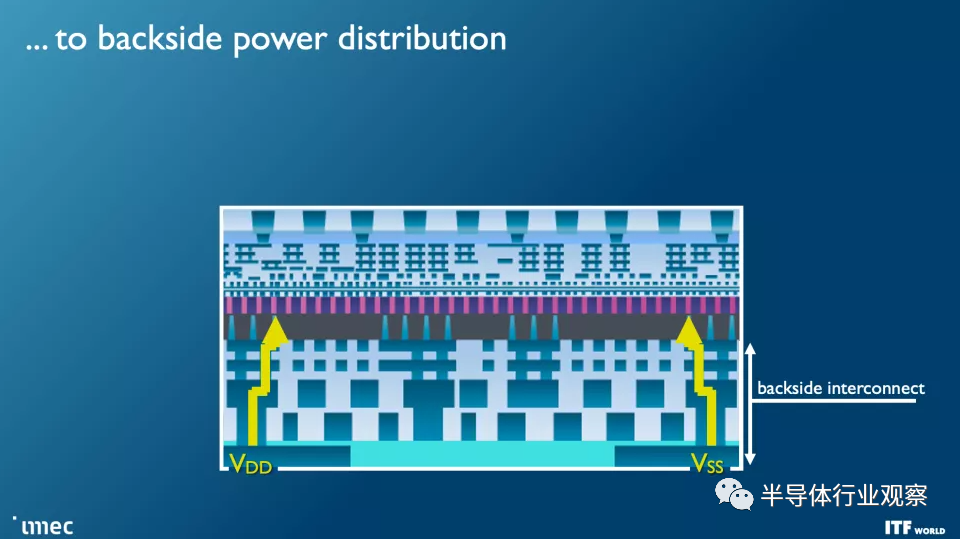

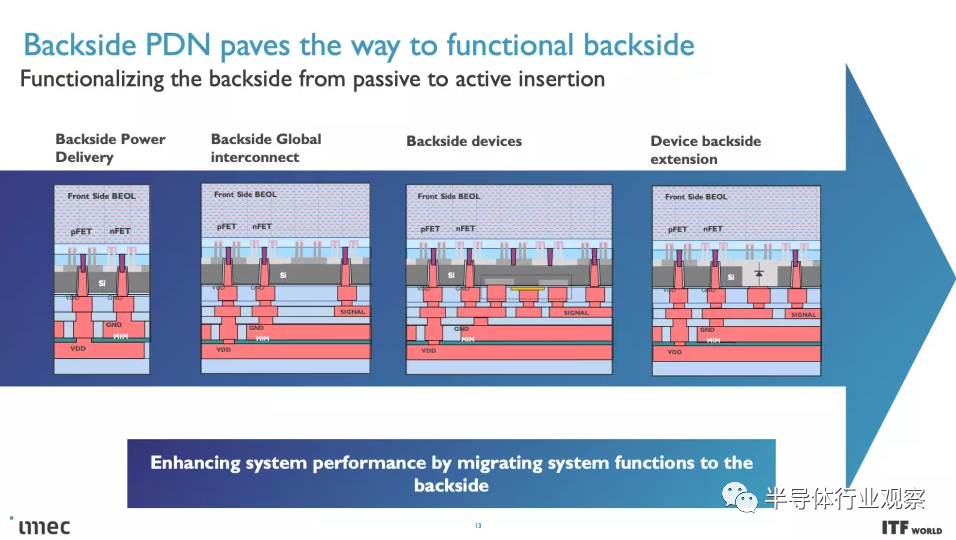

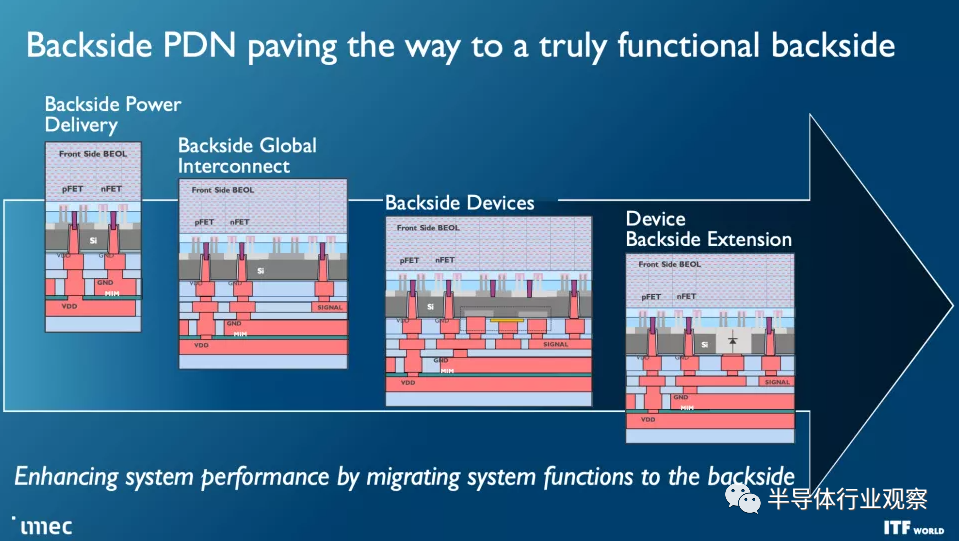

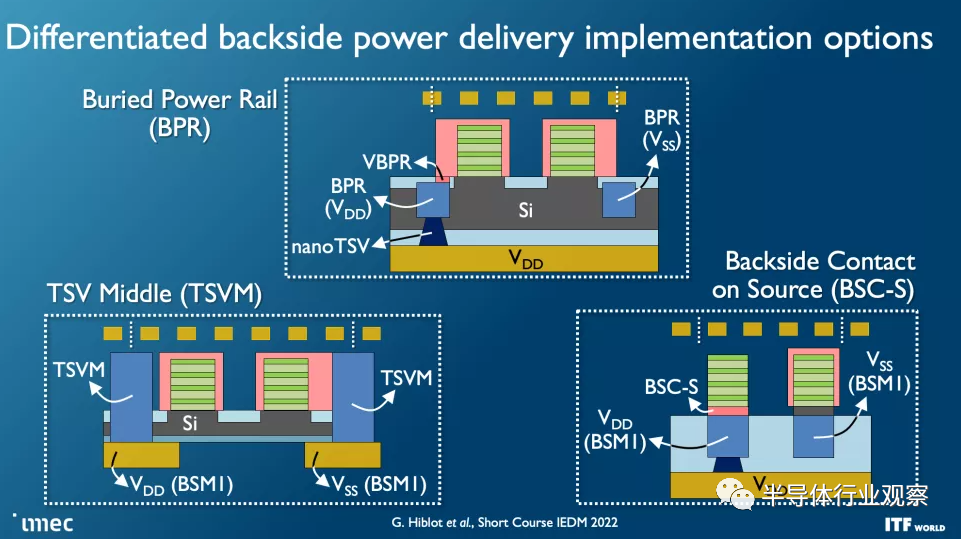

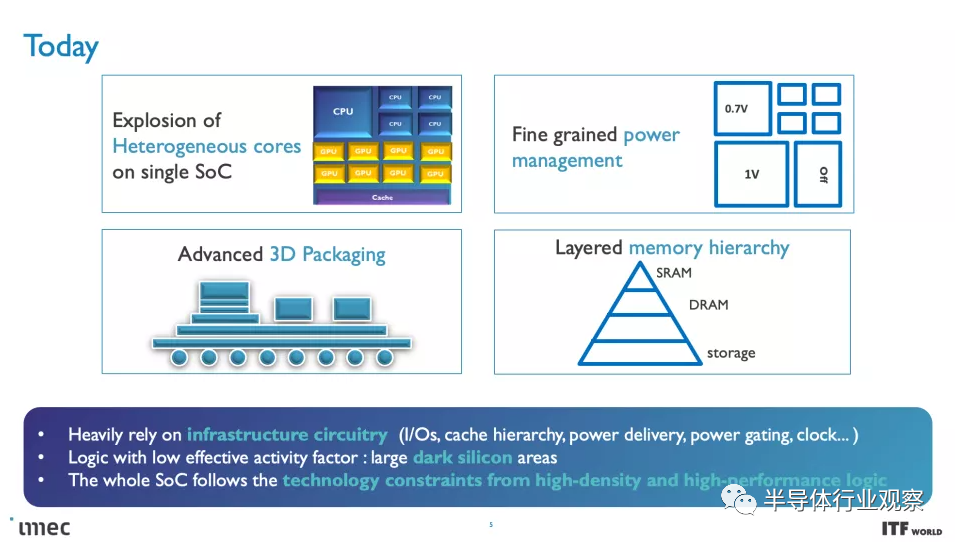

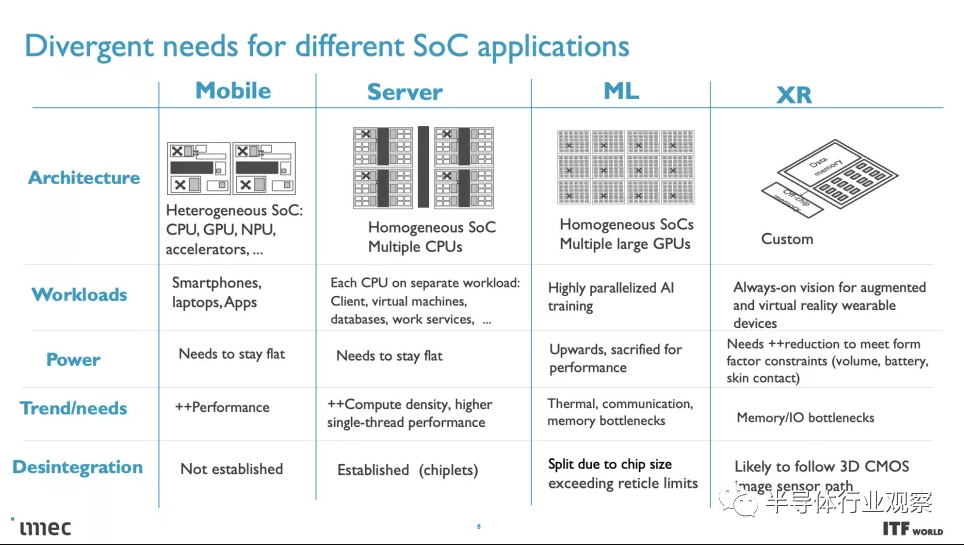

STCO 和背面供电 在最高级别,系统技术协同优化 (STCO:system technology co-optimization) 需要通过对系统和目标应用程序的需求建模来重新思考设计过程,然后使用这些知识来为创建芯片的设计决策提供信息。这种设计方法通常会导致“分解”通常作为单片处理器的一部分的功能单元,例如供电、I/O 和高速缓存,并将它们拆分为单独的单元,以通过使用不同的方法针对所需的性能特性优化每个单元类型的晶体管,然后也提高了成本。  完全分解标准芯片设计的目标之一是将高速缓存/内存拆分到 3D 堆叠设计中它们自己的不同层(更多内容见下文),但这需要降低芯片堆栈顶部的复杂性。改造后端生产线 (BEOL:Back End of Line) 流程,重点是将晶体管连接在一起并实现通信(信号)和电力传输,是这项工作的关键。  与当今从芯片顶部向下向晶体管传输功率的设计不同,背面配电网络 (BPDN:backside power distribution networks ) 使用 TSV 将所有功率直接路由到晶体管的背面,从而将功率传输与保留在其内部的数据传输互连分开另一边的正常位置。将电源电路和数据传输互连分开可改善压降特性,从而实现更快的晶体管开关,同时在芯片顶部实现更密集的信号路由。信号完整性也有好处,因为简化的布线可以更快地连接电阻和电容。  将供电网络移至芯片底部可以更轻松地在裸片顶部进行晶圆到晶圆的键合,从而释放在存储器上堆叠逻辑的潜力。Imec 甚至设想可能将其他功能转移到晶圆的背面,例如全局互连或时钟信号。  英特尔已经宣布了自己的 BPDN 技术版本,称为PowerVIA,将于 2024 年以intel 20A 节点首次亮相。英特尔将在即将举行的 VLSI 活动中透露有关该技术的更多细节。同时,台积电也宣布将BPDN引入其2026年量产的N2P节点,因此这项技术将落后于英特尔相当长的一段时间。也有传言称三星将在其 2nm 节点采用该技术。        |