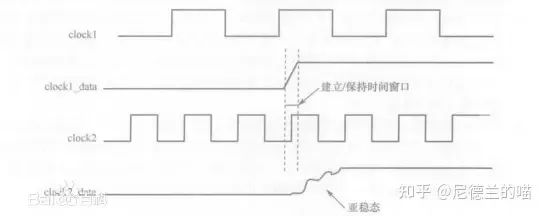

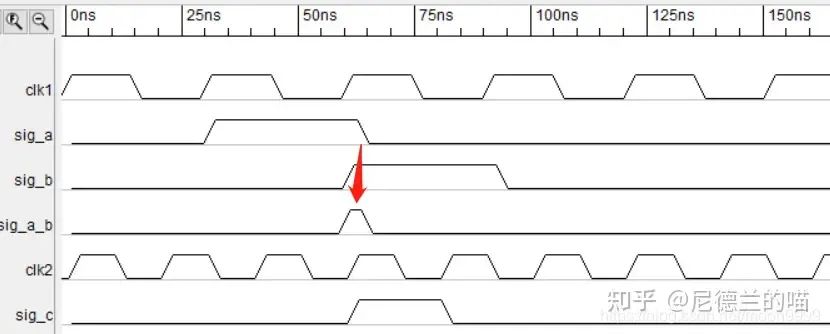

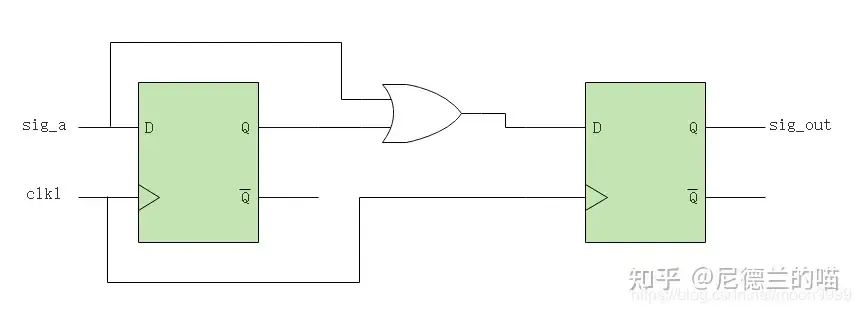

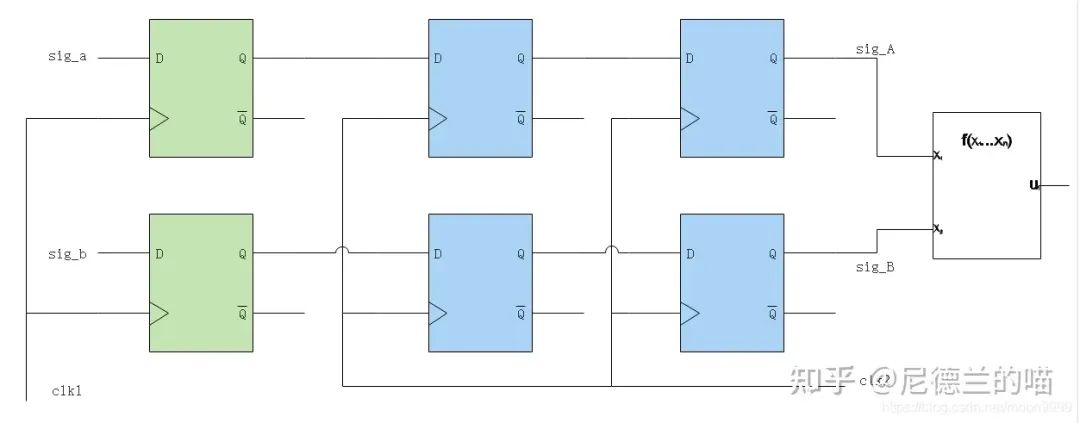

【芯片设计】异步电路碎碎念(一) 到底什么是异步电路异步逻辑本身呢是一种常见的信号处理,但是一旦处理不当就会引发多种电路危机,而这些电路危机大多与亚稳态有关。亚稳态是我们老生常谈的问题了,再来复习一下什么是亚稳态呢。在数字电路中信号处于非0非1、介于高低电平阈值之间未定义的状态称之为亚稳态。由于数字电路的特点只有高低电平和高阻态能够稳定存在,亚稳态会在0/1之间完全不确定的反复震荡。理论上亚稳态可以在零噪声场景下稳定维持,但是实际应用中不会存在零噪声场景。  在前端设计中我们主要关心的是触发器亚稳态,当触发器的输入信号无法在亚稳态窗内保持稳定的可采样的电平状态时,那么就进入了寄存器亚稳态,我们既无法预知最终的输出电平也无法预知何时会稳定到最终的输出电平上。亚稳态窗即由触发器的建立时间和保持时间在时钟上升沿左右定义的时间窗口,setup time + hold time即亚稳态窗的长度,亚稳态窗由器件本身物理属性所决定一般来说工艺越新亚稳态窗会越短,但是更新的工艺并不意味着亚稳态的传播会变短,这点我理解和电压的关系更大,工艺值越小越不能上高电压否则会发生击穿,电压越低那么稳定时间就会越长,这一点再问问后端大佬。 亚稳态的危害是显而易见的,在电路中直接使用可能存在亚稳态的信号可能会导致数字电路系统紊乱,比如计数器乱跳寄存器异常触发等,而且亚稳态触发问题具有很大的概率性(概率公式就不列了,看着头疼),这导致有限的测试时间内并不能保证发现问题,即使发现了问题也极难定位到亚稳态问题,只能说隐蔽性太高了。当然借助于有了PT/CDC/RDC等工具和检查,对于大部分跨异步亚稳态隐患是能够及时发现的。 在这里再顺便说一下,我之前有一段时间把亚稳态、X态和Z态记混了。当然Z态最容易区分,是仿真中常见的高阻态,一般只有在信号空接时候会出现。而X态呢主要是在验证时候的概念,指的是信号的状态未知但一定是某一确定的电平值或数值,比如说某一寄存器如果没有写入过数据也没有进行过初始化操作,那么在仿真时直接读取出的就是X态,差态会在电路中蔓延造成不确定的结果,X态行为是可以通过EDA验证发现的关键信号也必须添加X态的检查;亚稳态呢就是我们上面提到的那一大堆东西了,一般来说呢亚稳态问题或者其他的跨异步问题是无法通过功能仿真来发现的,因为在功能仿真中时钟是理想时钟,时钟采样通过time-slot时间片的方式进行,setup time和hold time阈值均为0即亚稳态窗不存在,那么自然不可能触发亚稳态问题。不过验证技术始终在发展,现在是不是已经有能够发现亚稳态问题的验证方法我不确定。 那么要怎么处理跨异步中的亚稳态,大家都知道要进行打拍。需要打几拍呢?之前书上给的结论呢是打2拍就可以消除99%以上的亚稳态采样概率,不过随之工艺的进步尺寸减小电压降低,2拍已经逐步管不住亚稳态传播了,在7nm以上的工艺时代,跨异步一般需要打3拍才可以。 在跨异步打拍时如果处理不当,一样会引发其他问题,比较突出的是误采样(毛刺)、漏采样和过采样。 毛刺误采样的典型场景是信号在跨异步前不进行寄存而是直接将组合逻辑的输出作为源端信号,举例可见下面的波形。sig_a & sig_b进行跨异步,sig_a和sig_b本身是有传播时间差的,因此sig_a & sig_b产生了一个微笑的毛刺,在同步电路中这不构成威胁因为满足了setup time和hold time的采样要求。但是对于跨异步来说这就是灾难性的毛刺了,因为可能会被目的端时钟捕获,从而“无中生有”产生了一个周期的脉冲信号,直接影响了目的端的电路功能。  要避免毛刺被误采样,在信号处理中我们就要秉承一个原则,信号一律进行寄存器寄存后再进行跨异步,换句话说信号在跨异步之前不允许进行逻辑操作。 漏采样多发生于慢时钟采样快时钟信号场景下,在这种情况下快时钟域的信号一般要进行信号拓展,拓展为两倍即sig_out = sig_a | sig_a_ff,那么要拓展为多少才不会发生漏采样呢?一般来讲源端的跨异步信号需要维持目的端时钟2个周期,当然这是一个稳妥值,具体还有详细的计算方式我们后面再说。既然需要维持2个时钟周期,那么可见快时钟采慢时钟域信号也会发生漏采样的,比如133M采样100M信号,此时100M时钟域内的信号也需要进行1拍的拓展。  过采样的场景存在于快时钟采样慢时钟域的场景下,典型的如uart中的过采样场景。这种问题就无法避免了,需要跨异步两端进行相关的约束和约定。 那么如果信号顺利的跨过了时钟域,没有误采样、漏采样、过采样的问题,就高枕无忧了么?当然不是了,如果在目的时钟域进行两个跨异步信号的逻辑操作(也称再收敛)或者多比特信号采用打拍跨异步,还是会引发问题,如下图。  问题出在哪里呢?因为你不知道信号在第几拍恢复到正确的值,可能在第一拍也可能在第二拍。那么sig_a和sig_b如果不是在同一拍收敛到正确值上去的,就会出现至少一拍的错误处理结果,这对目的端一般是不可接收的。怎么避免这个问题呢?源端把该算的都算完再传过来,尽量别让我目的端进行什么操作就好了。对于多比特信号呢?要么方案中可以接受,要么采用格雷码一类的跨异步传输,或者采用握手或者异步FIFO之类更加复杂稳妥的传输方式。 |