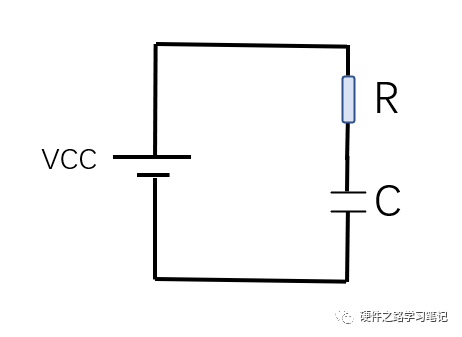

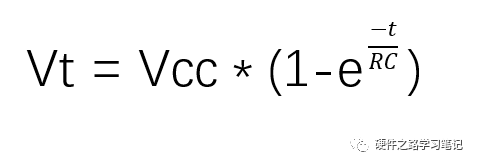

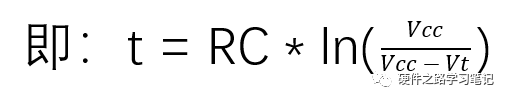

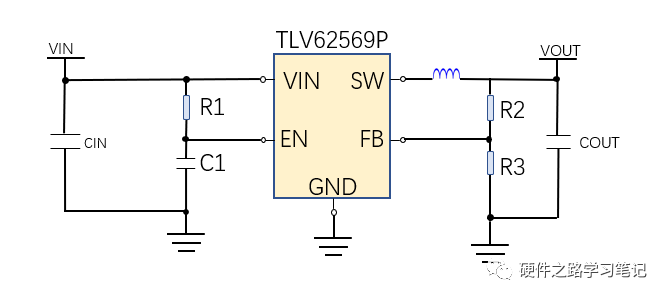

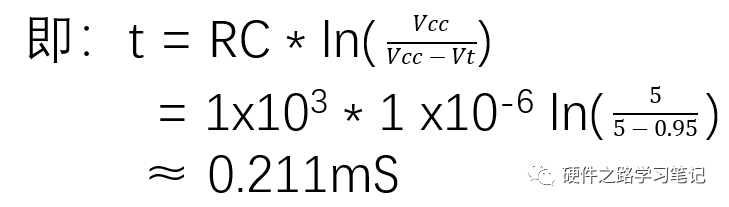

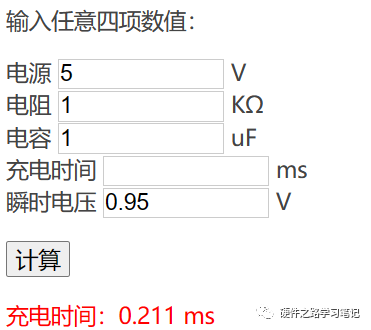

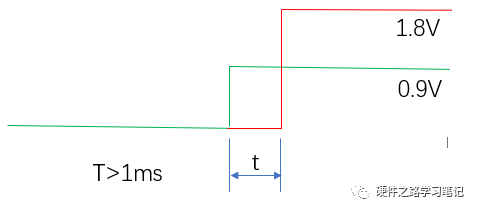

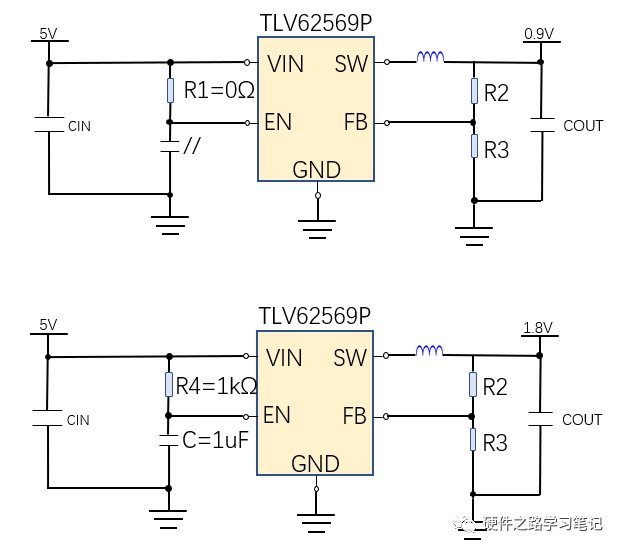

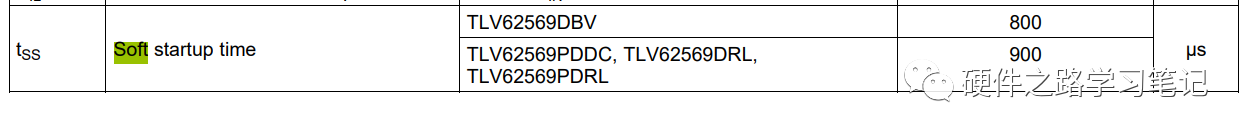

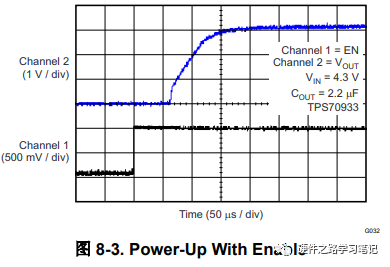

一、RC充电延时电路二、1. 电容充电时间公式  如上图所示,电池以VCC电压通过电阻R给电容C充电。那么 在t时刻,电容两端电压Vt 有:  反推即可得到充电时间的计算公式:  二、DC-DC芯片的延时上电 1. DC-DC芯片的是能引脚 以TI的TLV62569P为例,它的使能引脚EN脚介绍如下:  意思是:逻辑高电平则使能芯片,逻辑低电平则关闭芯片。 2.逻辑高电平与逻辑低电平 如下图所示,TLV62569P的逻辑高低电平电压如下,可以看到其逻辑高电平电压是0.95V。  3.为使能引脚加入RC延时 如下图我们将DC-DC芯片TLV62569P的使能引脚EN脚加入RC延时电路即可实现延时输出电压。  4. 实际延时时间计算 在如上图的延时结构中,假VIN是5V,R1是1K,C1是1uF,那么要使TLV62569P正常输出电压,即Vt等于0.95V。 则延时时间t:  懒得计算的话网上也有很多在线计算:(没研究出来怎么放文章以外的网址,还是回复关键词:RC延时 获取网址吧)  三、IC上电时序举例及其注意事项 1. IC上电时序要求 假设一个IC上电时序要求如下:即0.9V至少比1.8V提前0.1ms上电。  2. 选择两个同款DC-DC或者LDO 我们以DC-DC为例:如下图,0.9V先上电,可以直接令R1=0Ω,其电容不上件,因此0.9V立即输出(由于两个是同样型号的DC-DC,不用考虑软起动)令R4=1kΩ,C=1uF,理论计算得输出1.8V要延时0.21ms才会输出,符合时序要求。  3. 注意事项 上述例子采用的是同款DC-DC,但有些IC需要很多路电源,所以很可能出现不同型号DC-DC与LDO混搭的情况,此时就要注意其自身启动时间了,自身启动时间是指考虑到电路稳定需要时间、以及自身软起动功能导致的输出延时等。 如果出现混搭的情况,可以根据不同电源的数据手册给出的输出时间、软起动时间等做出修改,例如以下参数:   同时可以参照上述电路,每个电源都预留RC延时电路,以便根据实际测试结果去调整时序。 |