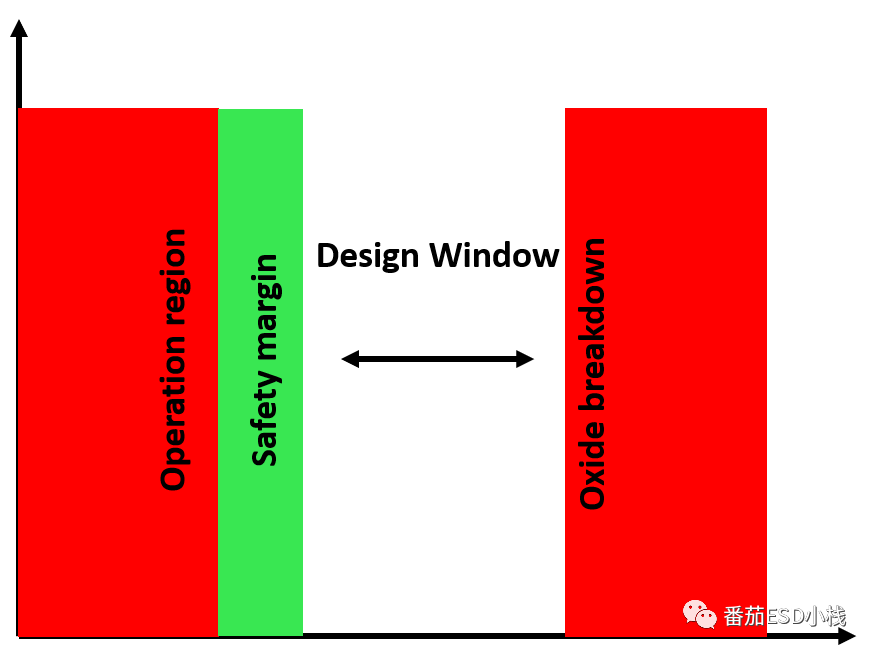

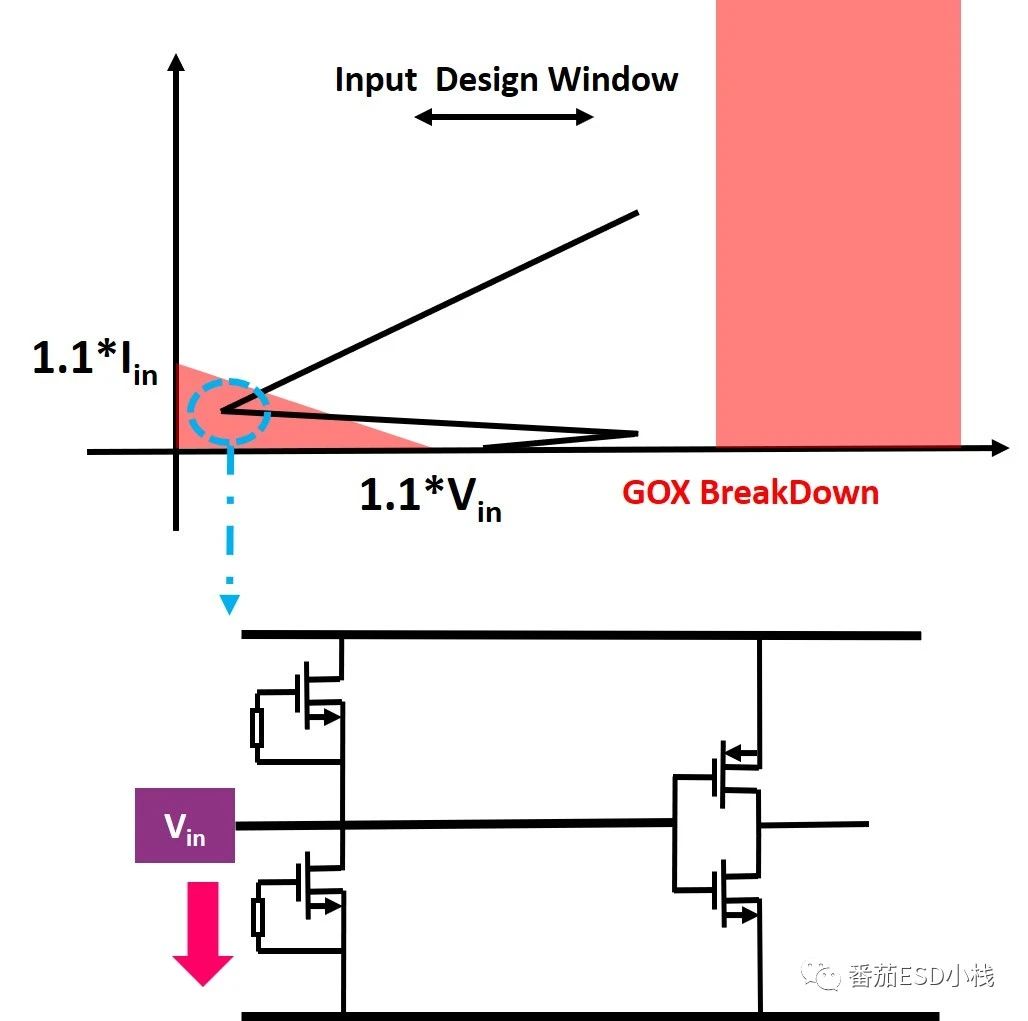

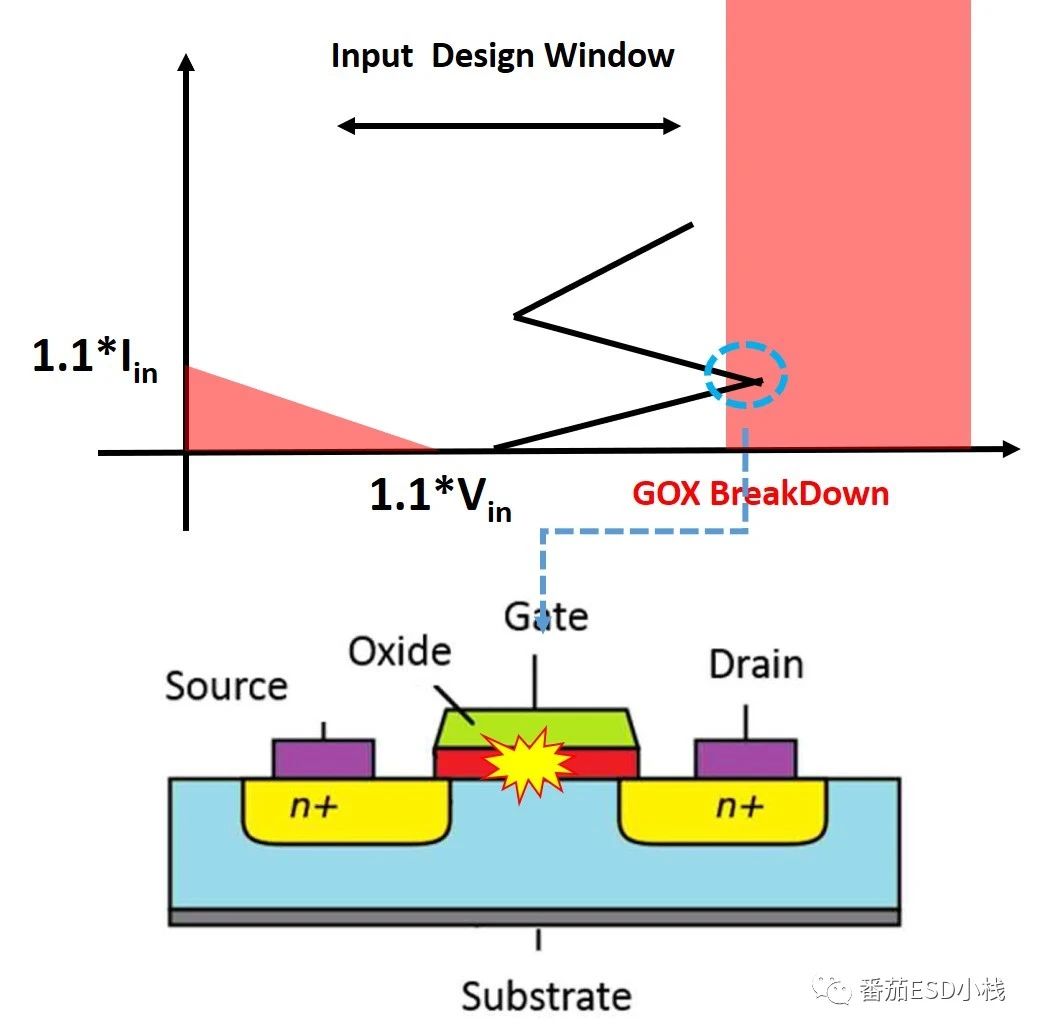

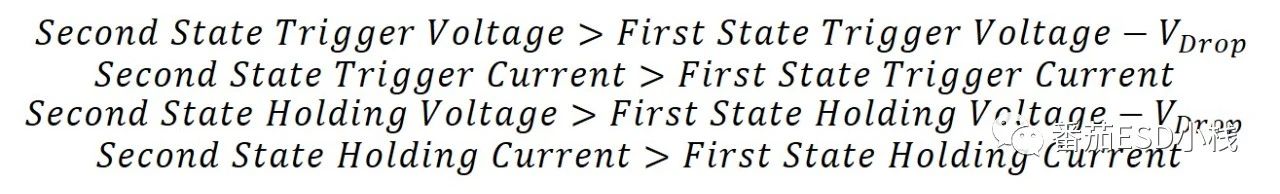

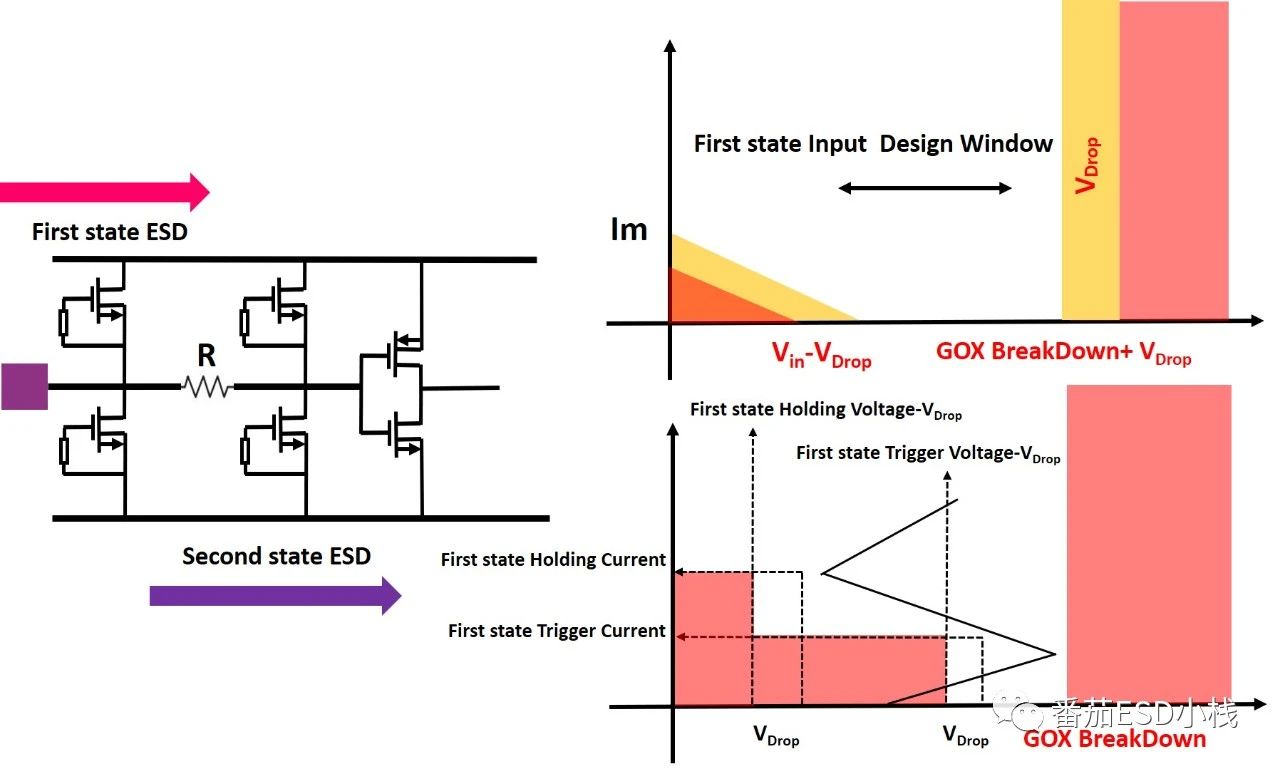

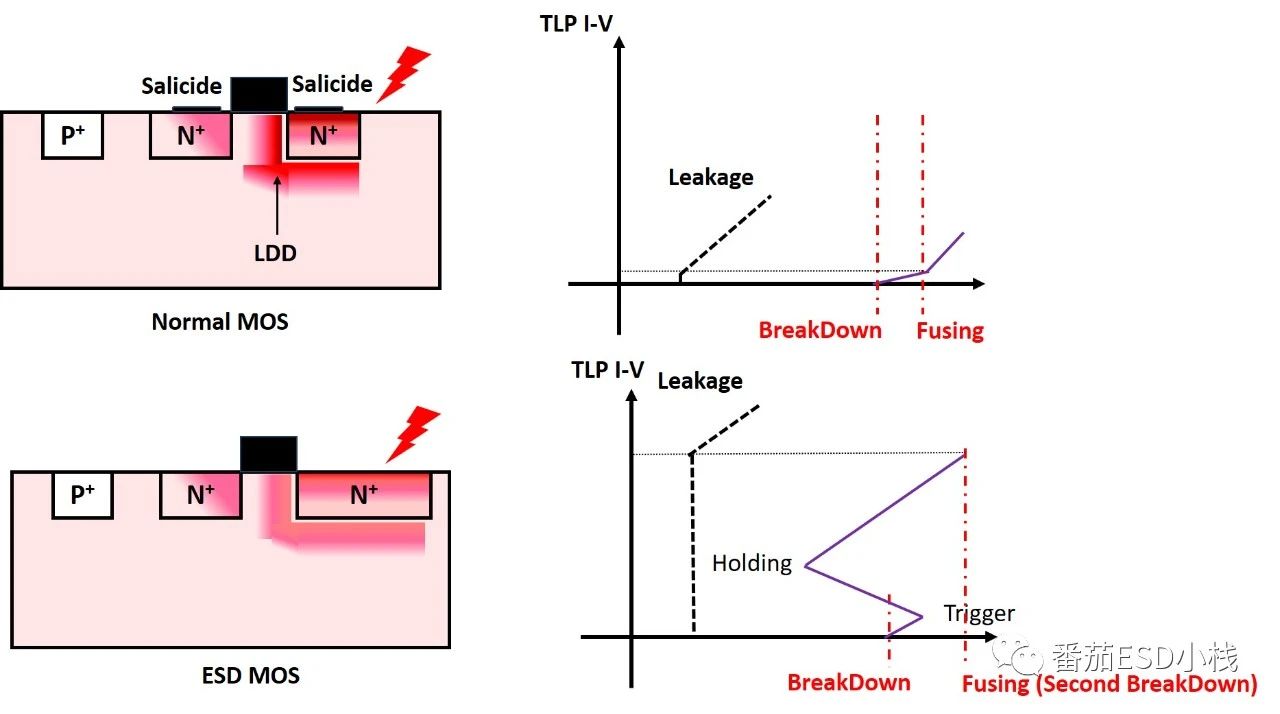

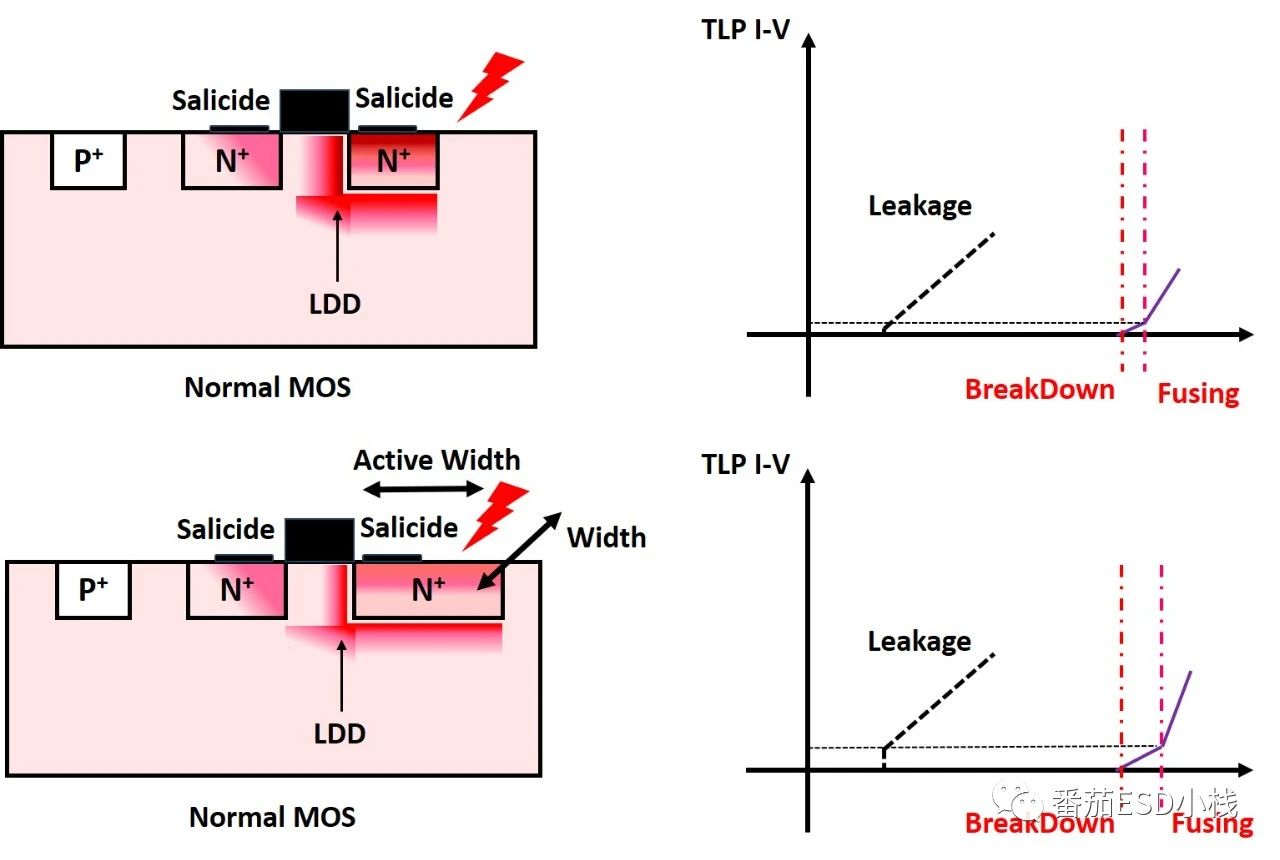

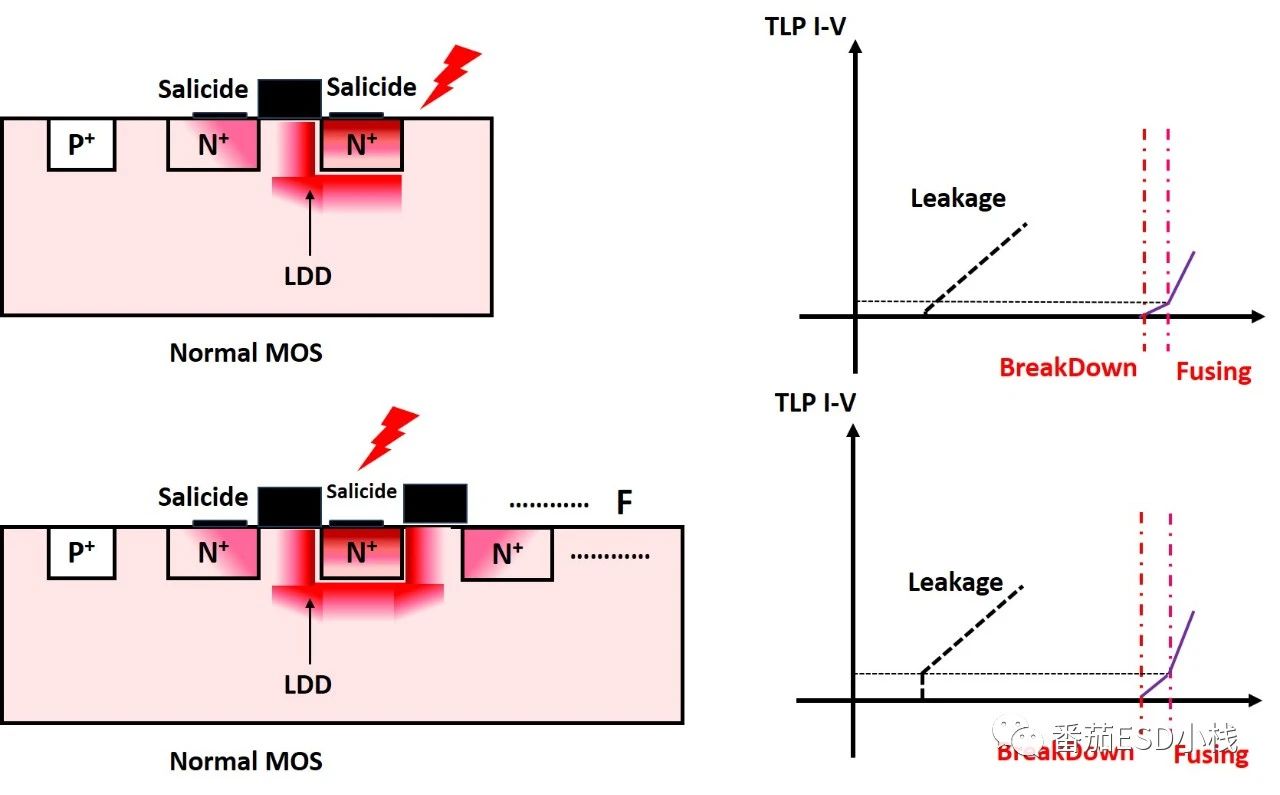

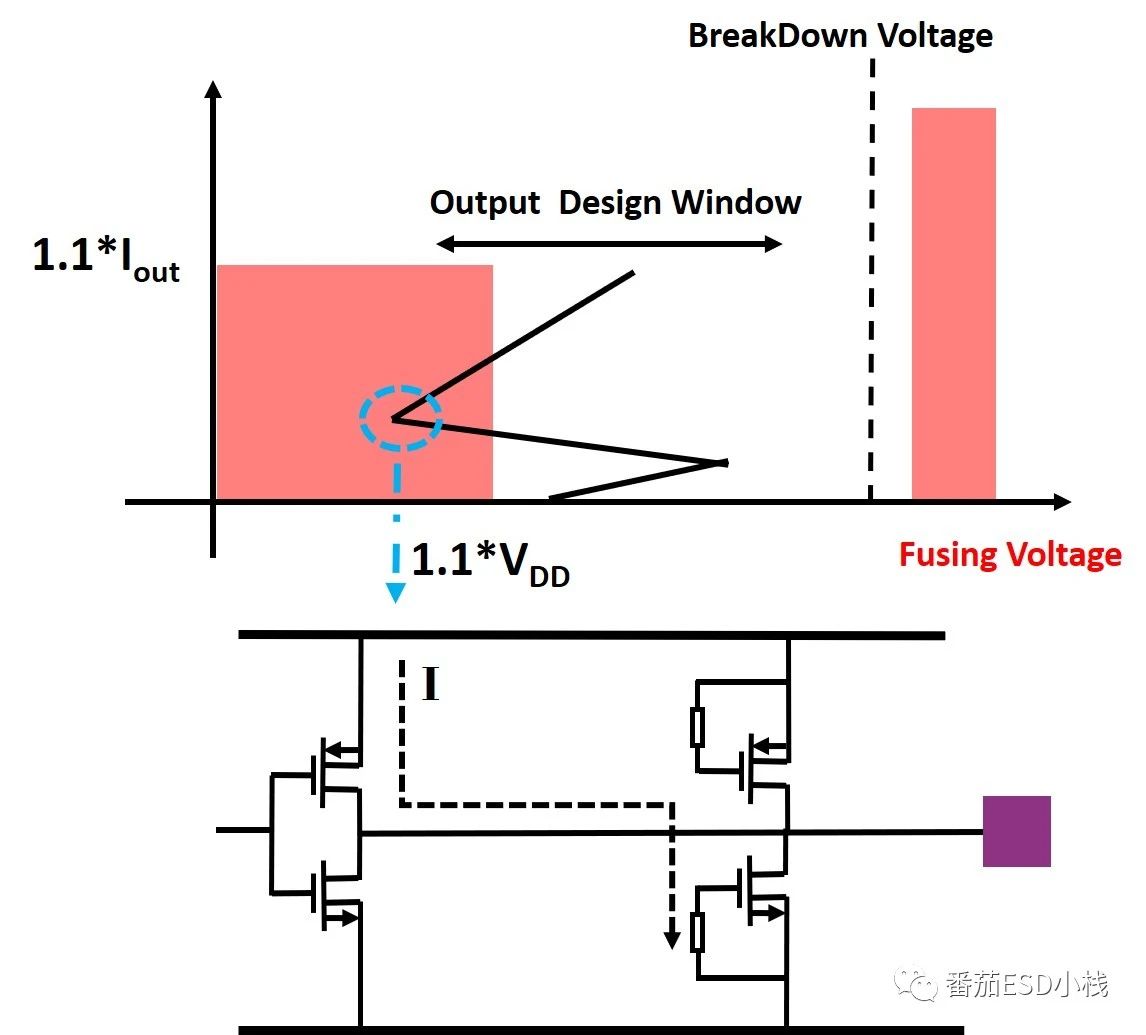

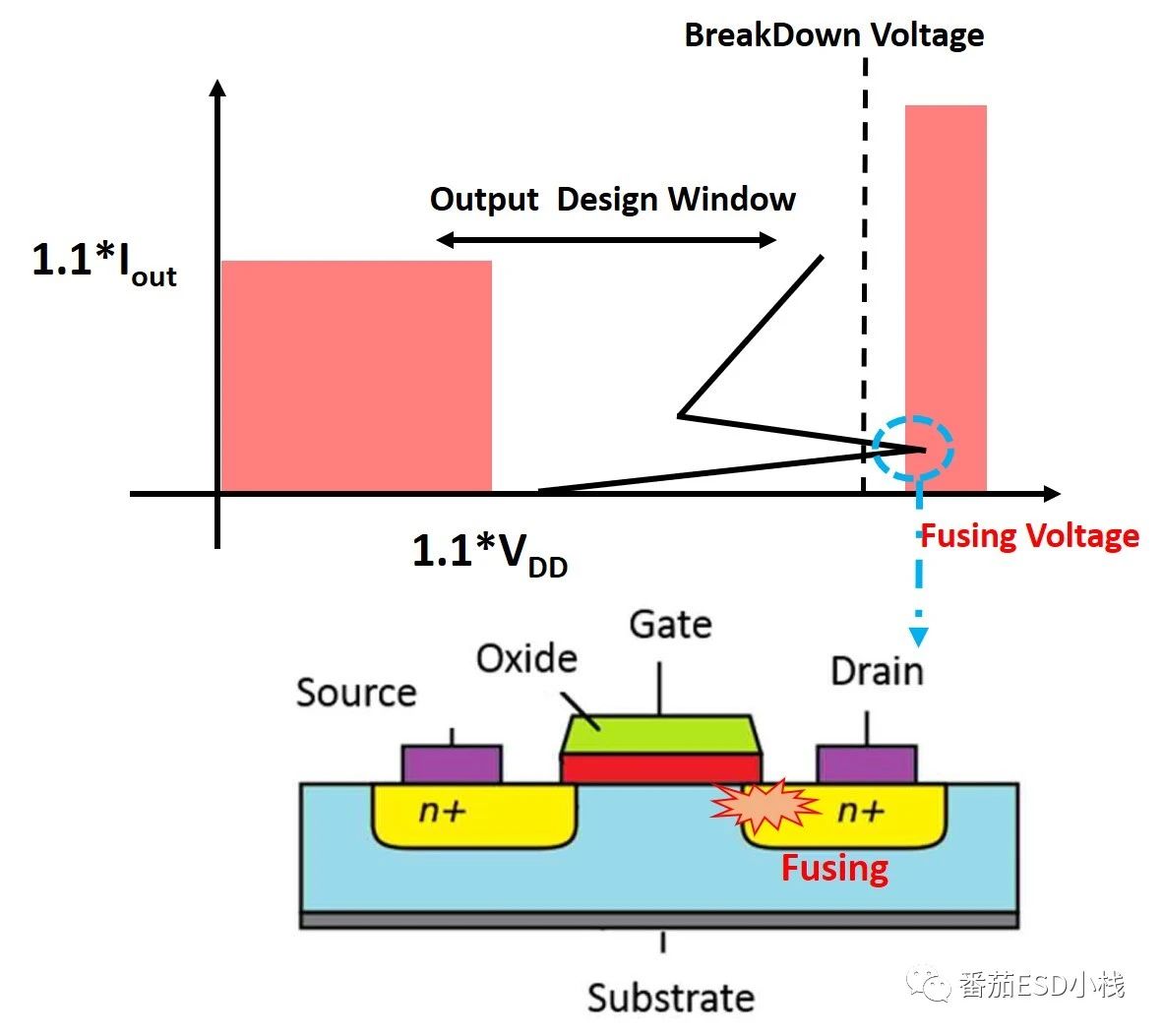

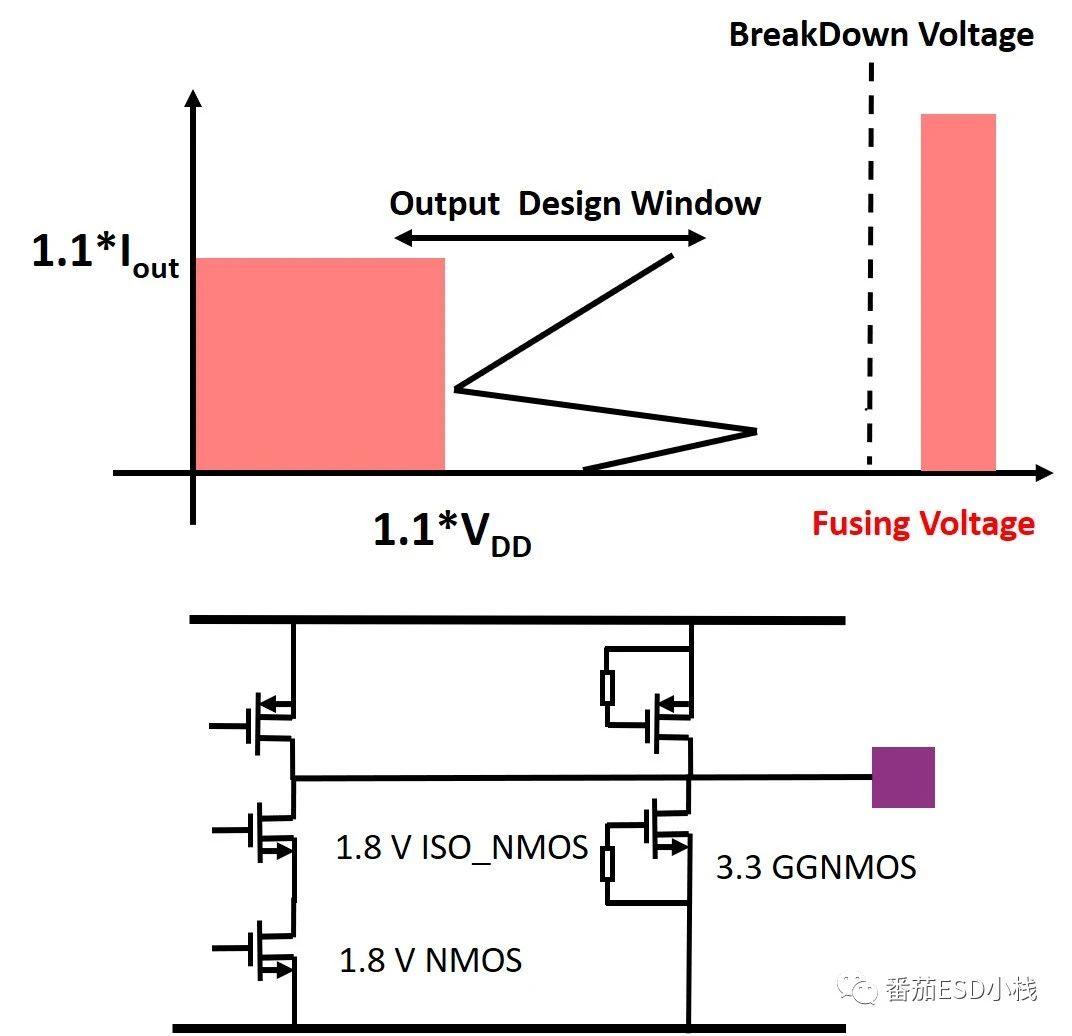

这一期笔者会对Design Window这一概念进行阐述,确立Design Window是进行ESD设计的必要步骤。Design Window并非一成不变,其会随端口类型、器件类型、电路结构而变化。详细的Design Window是ESD设计的基石,设计师在电路设计阶段就需要确立Design Window,使ESD器件与Design Window进行适配。如图一所示,传统Design Window的确立方法忽略了内部电路与端口类型,在一些设计场合下精度不足。 图一.传统Design Window示意图。 Design Window是ESD器件的设计窗口,其目的是保证ESD器件不会影响电路正常功能,又要保护内部器件避免ESD冲击。尤其是Pad Based防护策略,比较依赖Design Window的确立。 一.Input Design Window 以最为常见的输入电路结构为例,输入端口与内部MOS的栅极相连,如图二所示:Input Design Window的下限为栅级负载曲线:如果ESD器件的Snap-back曲线进入该区域内,ESD器件误触发后便会一直维持在导通态,无法从开启状态中改出,对输入电平下拉,影响电路功能。  图二.输入端口Design Window下限。 如图三所示,因为栅化层的绝缘性,所以Design Window的上限为MOS管的栅氧击穿电压(这里是指静电脉冲击穿电压,与TDDB直流击穿电压有一定区别)。  图三.输入端口Design Window上限。 如图四所示而为了提升ESD鲁棒性,很多设计会在端口放置电阻和二级防护单元。第一级ESD防护因为电阻R分压,其Design Window会被拓宽:  而第二级ESD器件面对HBM时不能先于第一级触发,并且触发后Snap-Back不能过低,避免一二级ESD防护器件发生冒险竞争,所以:  所以需要确保一二级ESD防护器件类型一致,相近的Snap-Back曲线才能确保二级防护单元不会与第一级产生冒险竞争。  图四.二级防护输入端口Design Window。 二.Output Design Window 以最为常见的输出电路结构为例,输出端口与内部MOS的漏端相连。如图五所示,MOS管有源区面对ESD时的失效机制主要是由热电效应造成的熔毁(区别于直流击穿)。Normal MOS没经过特殊设计,一旦发生雪崩击穿,很快就会发生熔毁。反观ESD MOS因为采用了Salicide Block,ESD implant,有源区拉宽等工艺处理,在ESD导致的雪崩击穿后,电场分布与热量分布都比较分散,不会集中在器件表面,缓解了热电效应,大幅度提升了器件的极限时,达到二次击穿电压/电流时才会发生熔毁,因此ESD MOS的熔毁电压高于Normal MOS。虽然都存在寄生体三极管,但是Normal MOS发生Snap-Back现象前大概率已经熔毁。  图五.Normal MOS与ESD MOS 的Fusing区别。 缓解Normal MOS雪崩击穿后的热电聚集效应能有效提高器件鲁棒性,如图六所示,增加单个Finger的Width和拉宽Drain端有源区距离能缓解热电聚集,避免在热量集中在一点,从而提高Fusing Voltage。  图六.Normal MOS修改版图参数对Fusing的影响。 如图七所示,增加Finger的数目能提升器件整体的过电流能力,但是并不能改变单个Finger的Fusing Voltage,只能改变其Fusing Current。因为电热效应未得到缓解,Fusing Voltage也不会得到改善,但是触发熔毁需要更高的电流,从另外一种角度提高了器件的ESD鲁棒性。所以最后一级输出级的MOS管最好采用拉宽有源区,增大W,增加Finger数等版图画法,但是不建议采用SAB、ESD implant等改变器件结构的手段。  图七.Normal MOS修改版图参数对Fusing的影响。 Output Design Window,如图八所示其Design Window的下限为PMOS的负载曲线,如果ESD的曲线进入该负载区内,VDD电流就会通过ESD器件流出体系,从而影响输出电压。  图八.输出端口Design Window下限。 如图九所示,Design Window上限是内部MOS的Fusing曲线(一般情况下输出级的PMOS的Width要大于NMOS,所以NMOS更容易发生熔断),MOS器件的熔毁是一个比较复杂的过程,除了器件沟道表面有熔毁风险外,有源区与冶金结接触也会有熔毁风险。  图九.输出端口Design Window上限。 由Output Design Window可知,Output端口要保证ESD MOS在内部MOS熔毁前触发Snap-Back,也就是: Trigger Voltage<Normal Mos Fusing Voltage 虽然GGNMOS/GDPMOS的击穿电压会小于NMOS/PMOS,但Output端口的Design Window也并不充裕。所以需要对输出级的MOS管采用拉宽有源区,增大W,增加Finger数等手段提高Fusing Voltage,拓宽Design Window,同时Drain 端Contact尽量密集,降低冶金结熔毁风险。如果能在输出端添加电阻或利用版图走线增加一定的寄生电阻,也能很有效的拓宽Design Window(与输入端一致)。 如图十所示,采用隔离NMOS的电路结构也能提升Design Window。  图十.隔离NMOS输出级Design Window。 下拉支路的击穿电压为1.8V NMOS和1.8V ISO_NMOS的击穿电压和,熔毁电压也是两个NMOS的和。该输出级NMOS的Design Window上限便是两个NMOS Fusing Voltage的和,其Design Window会比3.3V NMOS要宽。 三.VDD Design Window 如图十一所示为VDD Design Window,其下限是1.1*VDD,因为VDD的驱动能力近似是无穷大的,如果ESD器件的Holding Voltage小于VDD,使用过程中一旦VDD的扰动开启ESD器件,ESD器件的低阻通路会一直开启,直到烧毁。而其上限是VDD上的Weak Point,因为电路中与VDD相连的器件与模块很多,需要根据电路情况排查,取整个电路中的ESD的最低值作为上限。  图十一.电源端口Design Window。 笔者只是从最简单的情况入手,根据端口类型简要分析了不同端口的 Design Window。从本文可以看出,针对整个芯片时,Design Window的确立还是较为复杂,因为电路结构决定了端口的Design Window,所以设计过程中需要因地制宜,根据实际情况对每个端口确立自己的Design Window。 通过这篇文章也回答了两个问题: 1. 为什么MOS管源漏端的TLP损毁电压会高于DC损毁电压? 首先MOS管面对DC的击穿电压要小于TLP的击穿电压。其次这两种条件下MOS管源漏端的损坏机理不一样,DC电压下源漏击穿后很容易由雪崩击穿转化为热击穿,造成器件损坏,而TLP脉冲下器件达到熔毁电压才会损坏。 2. 为什么同样是NMOS,GGNMOS就能实现对普通NMOS的ESD防护? 只要GGNMOS的Trigger Voltage小于NMOS的Fusing Voltage,就能实现对NMOS的防护。 |