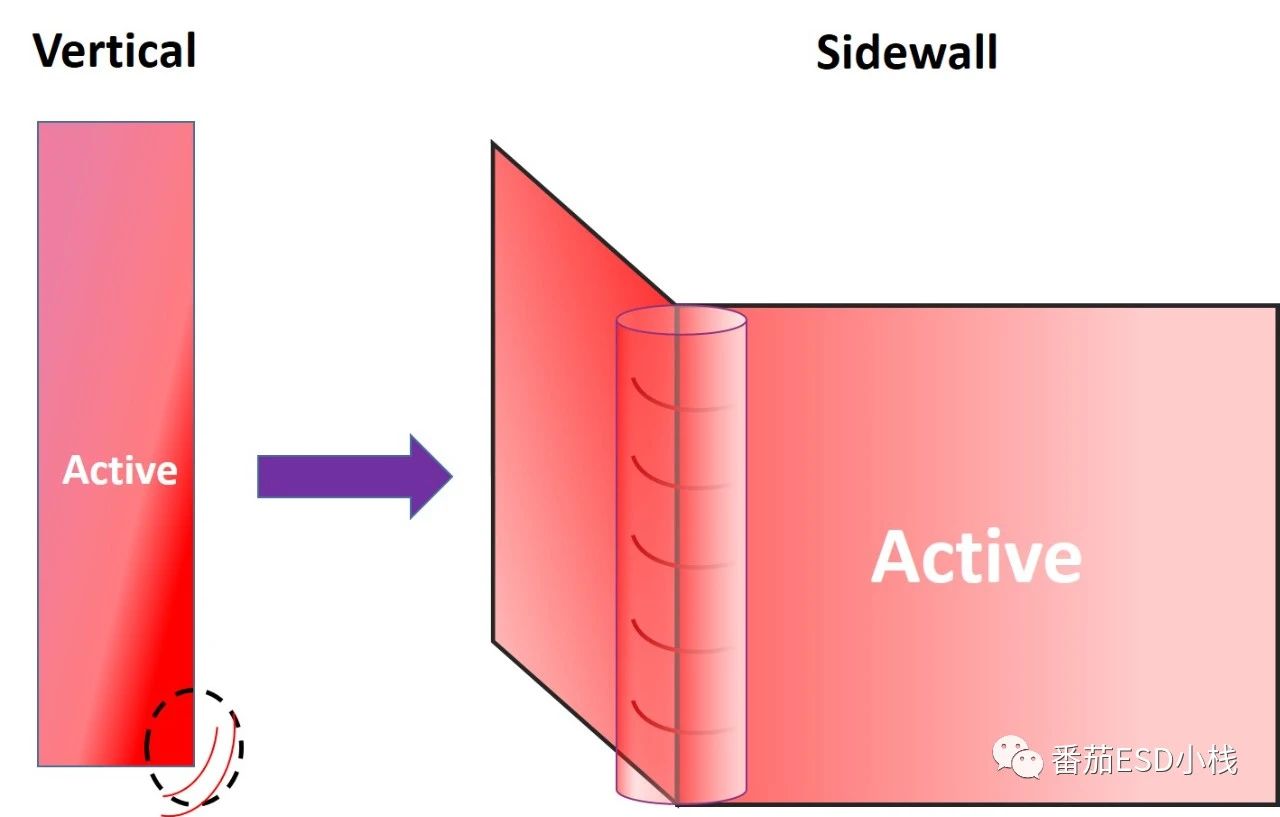

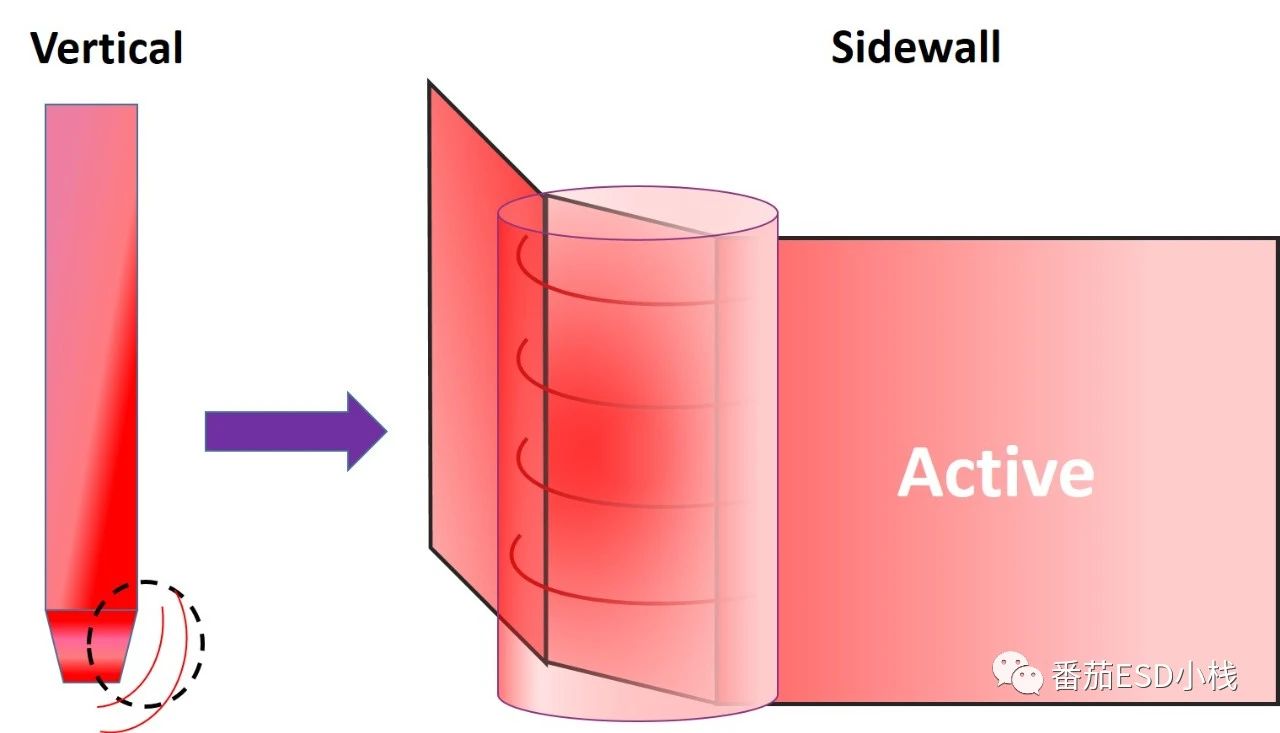

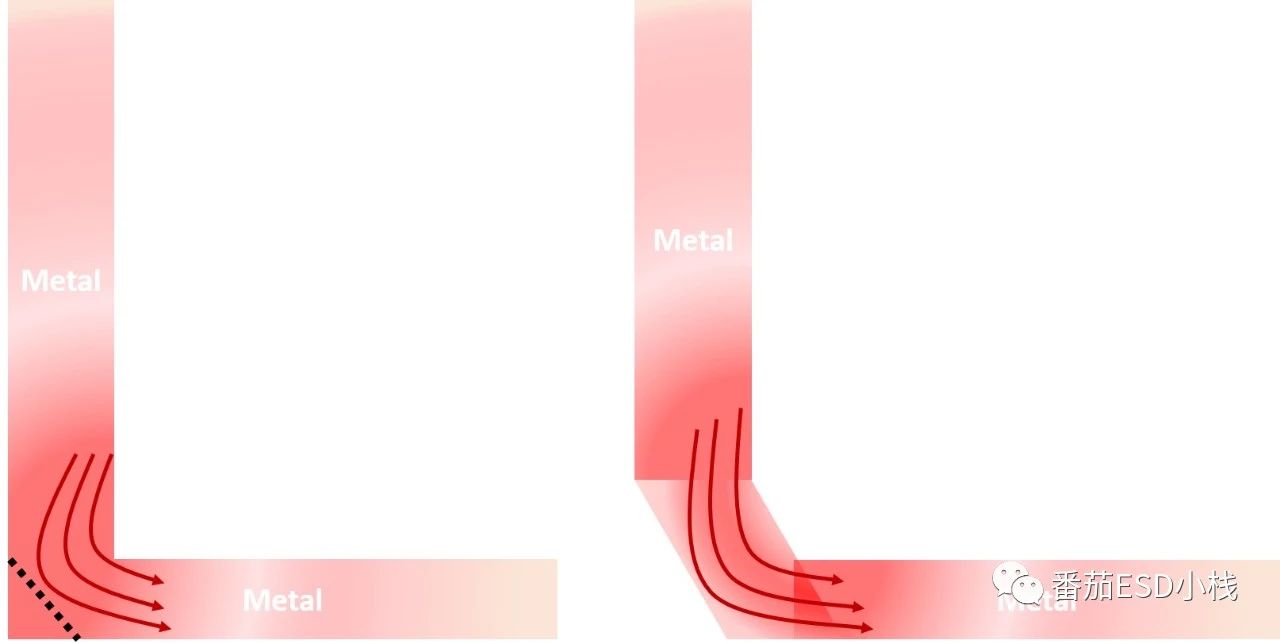

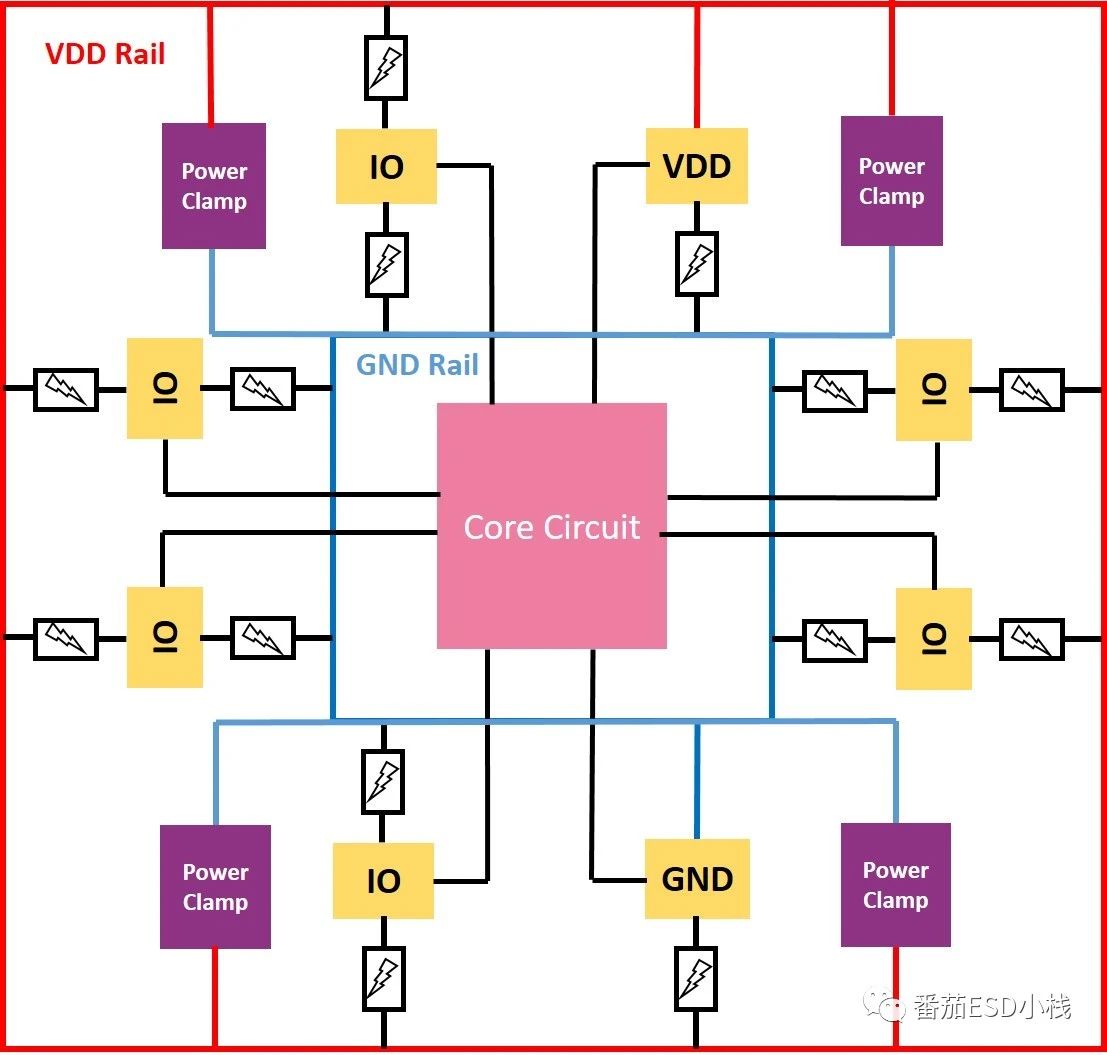

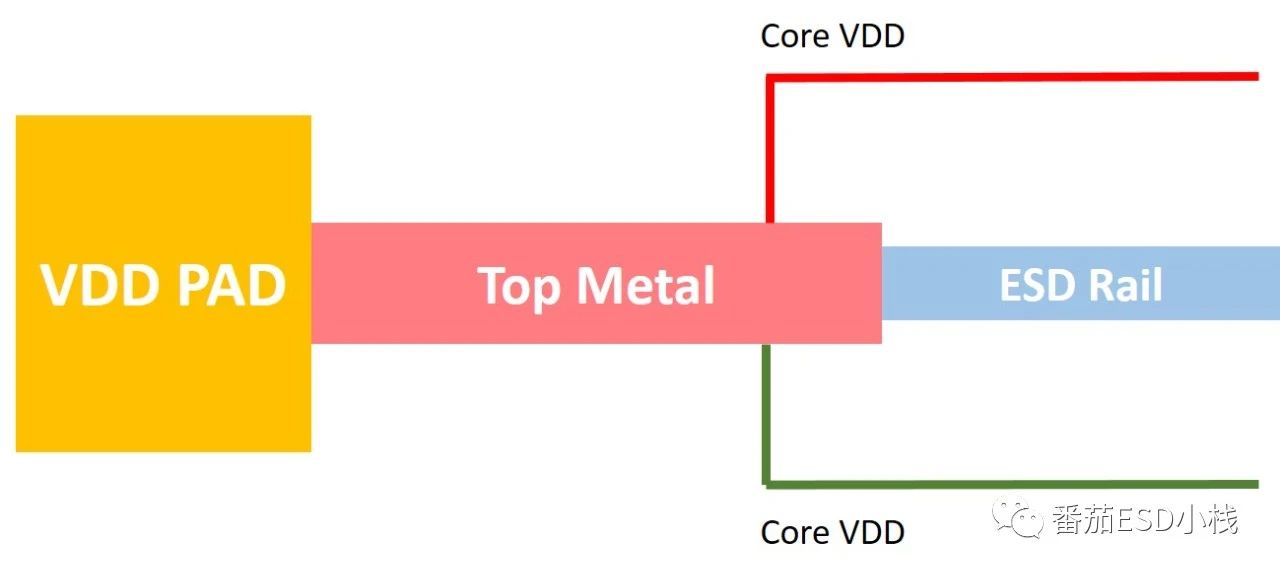

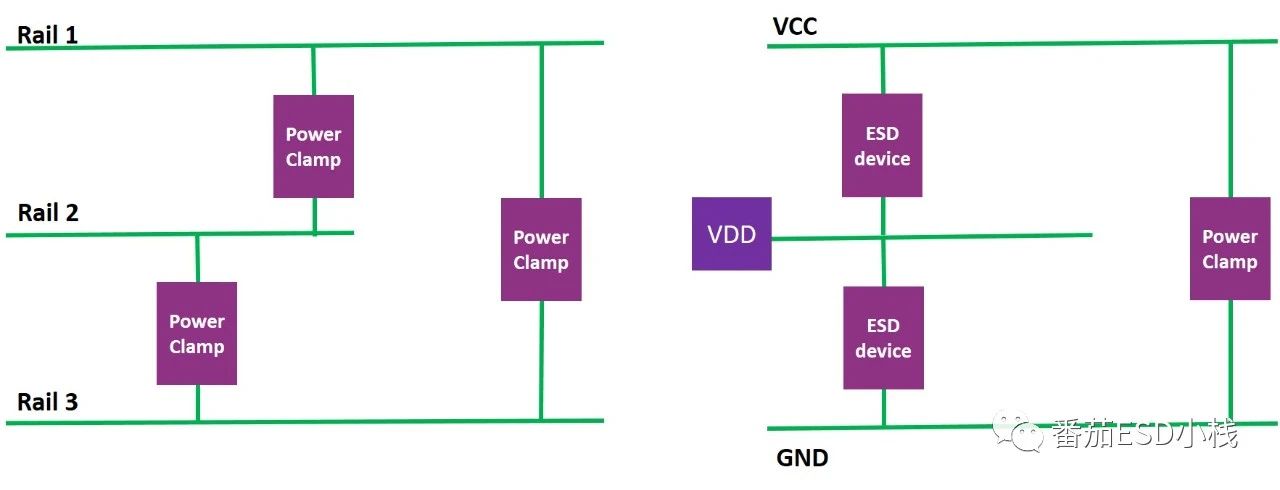

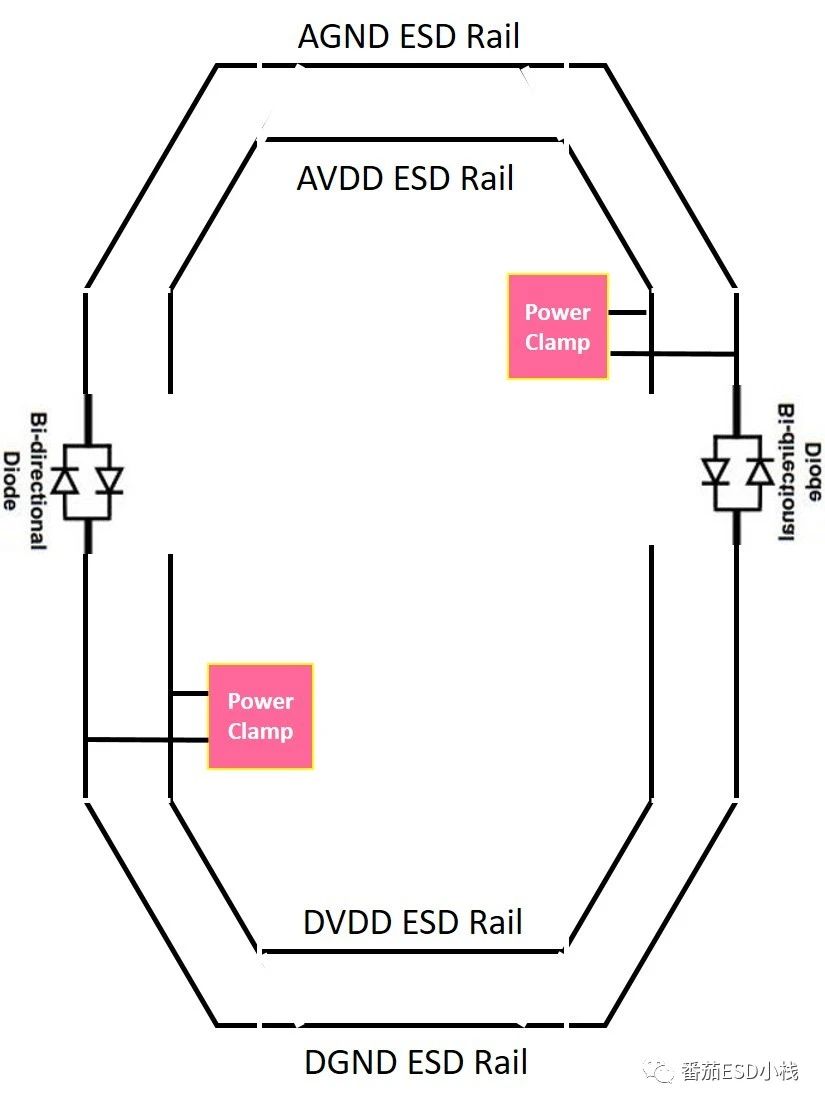

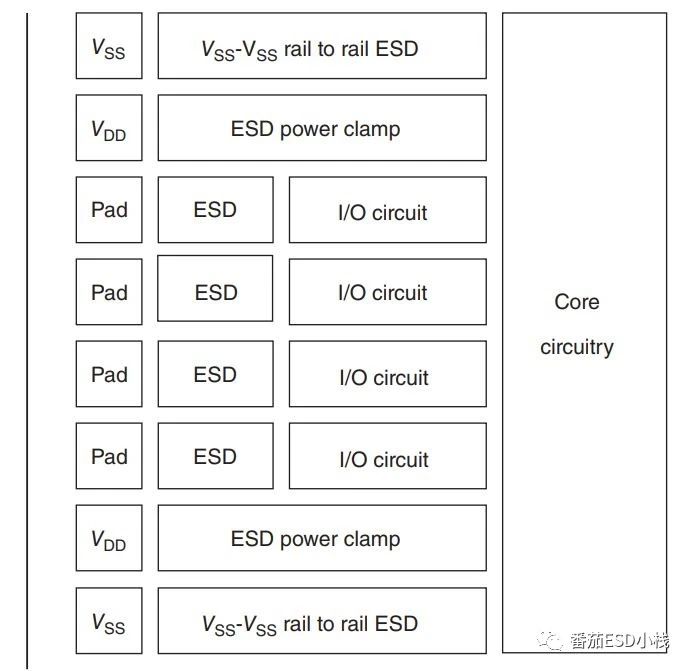

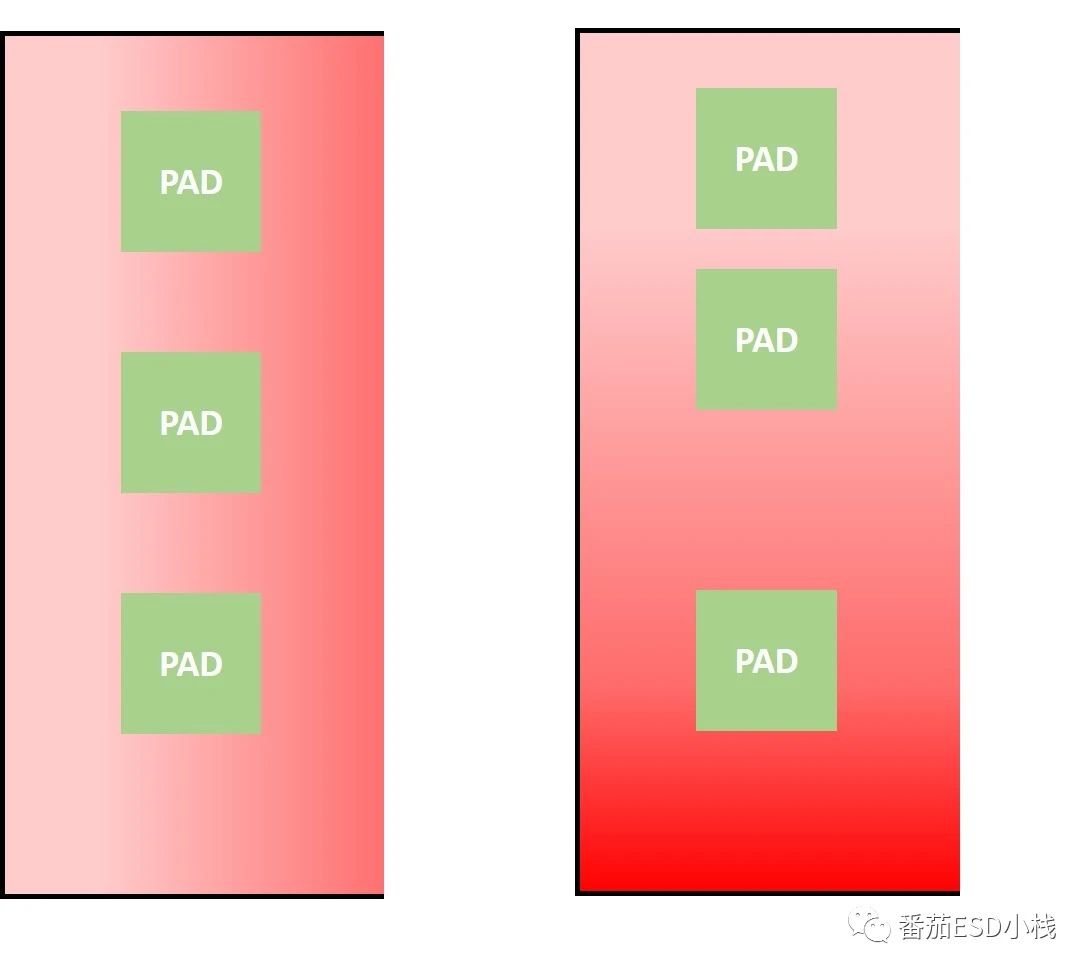

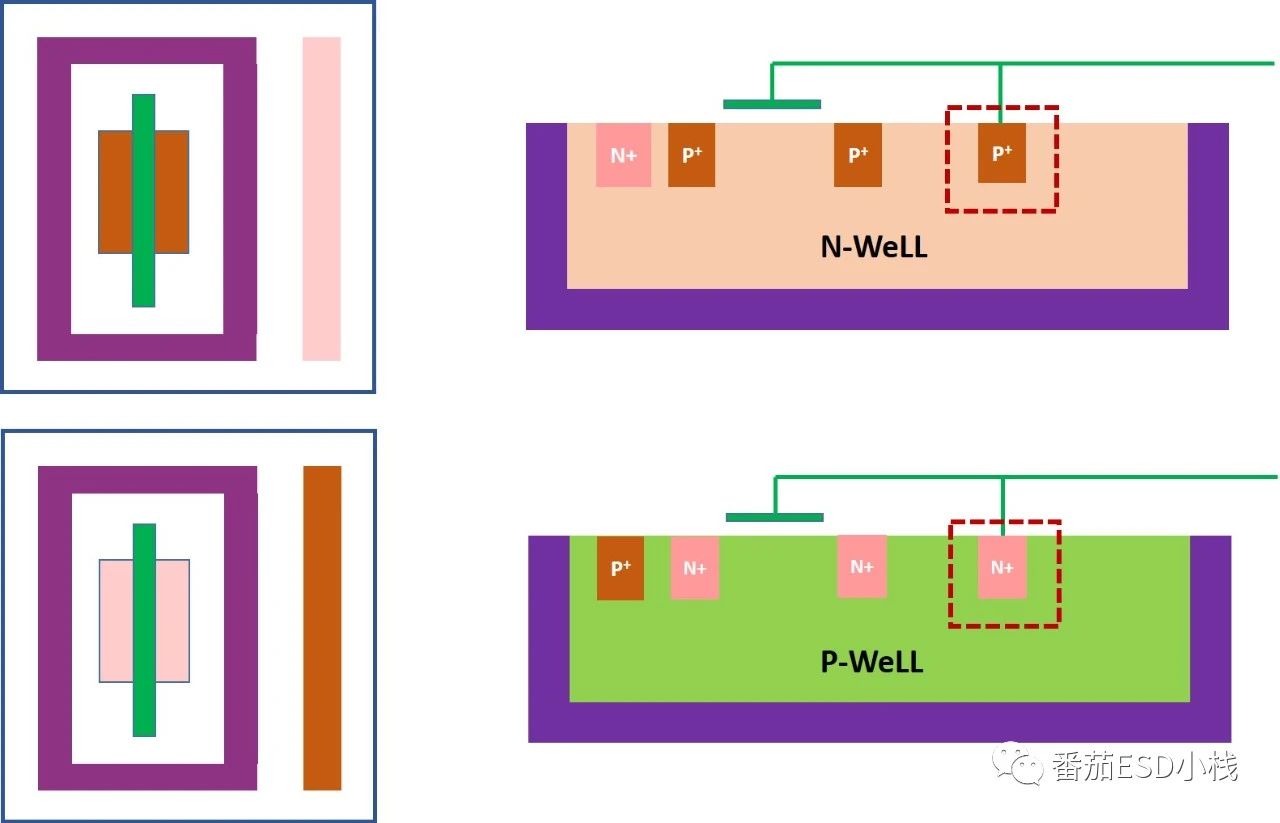

这一期继续探究版图中的可靠性设计。一.倒角 首先补充一下倒角的概念。很多ESD器件无论是有源区还是金属走线都会采用倒角的设计,这是一种很重要的版图设计细节,能提升器件与金属的过电流能力,降低失效风险。  图一.直角有源区电场分布示意图。 有源区边缘采用直角设计其电场分布如图一所示,直角处的电场分布集中,形成较窄的柱形电场分布,器件在该处的鲁棒性较薄弱,热电性能不甚理想。  图二.倒角有源区电场分布示意图。 如果有源区采用倒角设计,其电场分布如图二所示 ,倒角处的电场分布会被拉宽,形成较宽的柱形电场分布(类似球形电场分布),有效缓解热电效应,提升器件鲁棒性。  图三.金属线电场分布示意图。 同样的,过大电流的金属线也需要进行倒角设计。如图三所示,直角金属走线,电流只流经部分金属,电场分布会变窄,在直角处会出现热电集中。而采用倒角设计,电流会流经全部金属,电流经过的金属没有变窄,这种设计能缓解热电效应,降低金属线的失效风险。 二.ESD Rail ESD Rail是芯片ESD防护中最重要的角色之一,ESD Rail是一根/多根环绕全片/模块的金属粗线,其相当于泄放ESD的干流。而IO端口相当于支流,把ESD电流由端口泄放到ESD Rail,然后再流出系统。在电路设计阶段就需要工程师确定ESD Rail的电位,并依此设计IO端口。图四所示为全片ESD防护示意图,ESD Rail串联所有的IO ESD单元。一般情况下是由全片最高电位VCC和全片最低电位VSS作为ESD Rail,某些特殊情况下ESD Rail可以采用浮空电位(Floating ESD Rail,以后会作为案例探讨)。IO端口通过ESD防护器件(GGNMOS,GCNMOS,GDPMOS,Diode,Bipolar,SCR)建立与ESD Rail间的泄放通道,而ESD Rail与ESD Rail之间需要放置Power Clamp,建立轨与轨之间的泄放通道,以此保证ESD泄放通道的完整性。  图四.全片ESD防护示意图。 ESD Rail最好只与ESD器件相连,核心电路的VDD与GND建议不要与ESD Rail有连接关系。VDD和GND需要从PAD上单独抽头以提供核心电路的电位,如果布局布线存在一定难度,可以按照图五的方式抽头,PAD连接一段较宽的顶金后再走ESD Rail,Core Circuit从顶金抽头。  图五.VDD PAD抽头示意图。 在多电压域的设计中,会存在不止一个VDD电位,此时是否设置多条ESD Rail是需要工程师去做取舍的。如图六所示,ESD Rail越多,不同ESD Rail间所需的Power Clamp越多,也可以将VDD看做常规IO进行ESD设计。  图六.Multi ESD Rail与VDD IO。 如图七所示,在多模块的设计中,模拟模块的ESD Rail和数字模块的ESD Rail需要进行隔离以避免噪声干扰,所以在版图中可采用半包轨的设计,模拟模块的ESD Rail 只围住模拟部分,数字模块的ESD Rail 只围住数字部分,两者之间放置隔离器件,避免噪声影响。  图七.多模块ESD Rail 布局示意图。 ESD Rail布线时需要尽可能采用厚金,且宽度尽量要大。ESD Rail的环路阻抗会影响整个芯片的ESD防护能力,ESD Rail的寄生电阻越低越好。如图八所示,对于面积较大,ESD Rail较长的芯片,ESD Rail上需要间隔一端距离均匀摆放Power Clamp,以确保泄放效率。  图八.Power Clamp 摆放示意图。 三.PADPAD的摆放也会对ESD产生影响。PAD的摆放的最基本原则是要满足封装要求,不同的封装形式会对PAD的位置与间距提出基本要求,尤其是引线键合的封装方式。而PAD的布局是由芯片功能及其他设计指标决定,譬如高低压端口分别放置,数字模拟端口分别放置,输入输出端口分别放置等。如图九所示,因为PAD的金属密度很大,散热性与导电性都很优异,所以PAD最好间隔均匀的摆放,避免出现较大的电流和温度梯度。  图九.PAD分布与电流/温度梯度示意图。 四.PID(Antenna) 天线效应及其解决方法 PID(Plasma Induced Damage)等离子损伤是芯片设计中另外一种物理失效风险(又叫Antenna 天线效应),与ESD不同的是,PID失效只会发生在芯片后段的制备过程中,在芯片后段逐步制备金属层的过程中,面积很大的金属层在施加钝化层和绝缘填充物前,如同天线一般会聚集电荷。如果该金属与栅极等脆弱部位连接,就会产生失效风险。应对PID的方法主要有三种:其一是在连接栅极的金属线上放置一个反偏二极管,为了追求最大保护效率,该防护二极管最好是紧挨栅极,且与MOS管位于同一衬底内,所以在MOS管内栅极附近放置一个寄生二极管能最大程度的消除天线效应。当在制备过程中出现等离子累积后,电位提升,等离子会击穿二极管以实现泄放,从而避免栅极被击穿。如图十所示为PID防护二极管的版图,NMOS在P-WeLL内增加一个N+有源区构成一个寄生N-Diode与栅极相连,PMOS在N-WeLL内增加一个P+有源区构成一个寄生P-Diode与栅极相连。剩下的跳线法和增加驱动较为常见,这里也并不赘述了。  图十.PID二极管防护示意图。 五.EOS EOS是模拟版图中一项检查流程,能对芯片的寿命和可靠性进行检查。其工作原理就是确定芯片的工作电压是否在其SOA(Safe Operating Area)内,如果MOS管的工作电压长时间超过SOA可能会影响寿命和良率(很多工艺厂家都有类似工具)。尤其是针对LDMOS,需要重点检查其SOA,因为LDMOS的Vgs、Vgd、Vsd差距很大,电路工程师很容易忽略,且这个问题前仿和后仿都不会暴露。但是并不是所有的工艺都会提供EOS Agent,所以有时需要工程师进行人工检查,尤其是Level Shifter、Charge Pump、LDO等模块。 六.PERC这个工具一般针对先进工艺,主要检查电流密度与ERC问题,能在一定程度上检查出ESD隐患,但是对于泄放通路是否闭环,Design Window是否合理等设计问题就有些无能为力,能过PERC检查并代表ESD设计就能达标。 这一期的内容较为杂乱,讨论了多种影响芯片物理可靠性的因素,笔者也不能尽善尽美,类似PID、EOS、PERC等很多版图工程师远比笔者有经验,笔者这里也就顺带一提。而类似PAD的布局和摆放,更牵扯到芯片的设计,功能,应用场景,封装等多种因素,简单几句话也并不能阐述清楚。 |