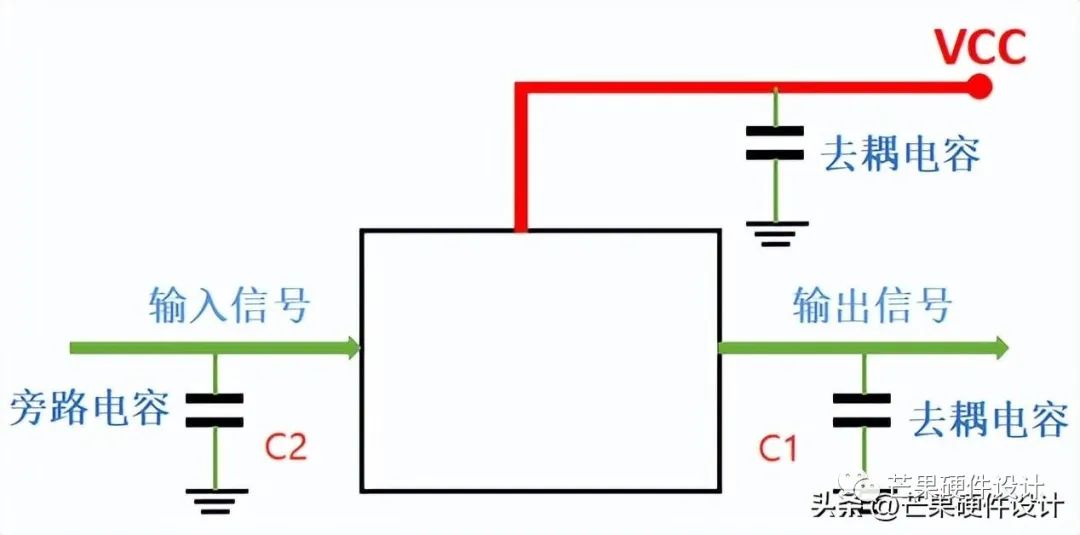

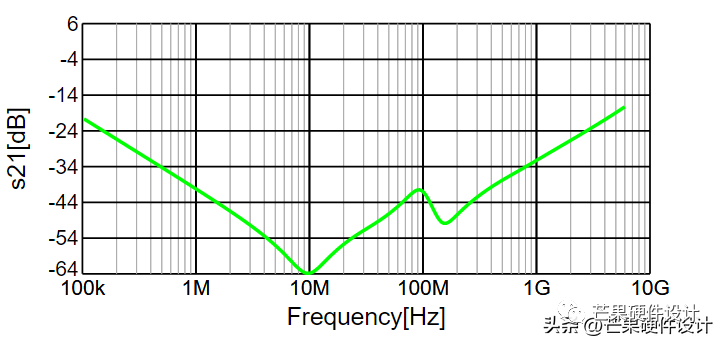

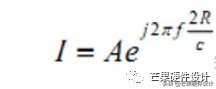

什么是去耦电容,旁路电容:去耦电容:去耦电容(Decoupling Capacitor)。我们知道英文中coupling是耦合的意思,而英文中加前缀的de一般是对后面单词的否定意思,因此Decoupling Capacitor就成为了去耦电容的意思。耦合一般是指A信号引起了B信号的变化。而我们的去耦就是让A信号的变化尽量不要传递到另一个电路中。去耦电容一般放在输出端,一般电路中的去耦电容一般有两个作用,滤波&储能。对于一个电路系统来说,一般有多个负载,这些负载的供电都来自于同一个电源,但是电路板上各个负载的工作都要动态地吸收电流,需要的电流可能会时大时小,比如系统刚上电的时候会有大电流等等,就会造成供电电压的不稳去耦电容相当于电池,储能是避免由于电流的突变而使电压下降,假设芯片突然要拉取大电流,可能会导致供电不足,这时电压可能会下降,这时C1储存的电能会释放,补充供电。 旁路电容:旁路电容(Bypass Capacitor)by pass 从靠近的地方,从旁边通过。在正常的通道旁边建立另外一个对高频噪声成分阻抗比较低的通路,从而将高频噪声成分从有用的信号用滤除。旁路电容一般放在信号的输入端,作用一般是滤除高频噪声信号。 其实个人认为去耦电容和旁路电容在本质上没有太大区别,不必过于纠结名词,本质都是希望输入到下一级的电路有一个稳定的值。 电容的选用: 我们在实际的选用中经常会选用1uF 和一个0.01uF。那么为什么选择这两个值,我认为有两个作用:拓宽了滤波频率范围,并联的另外作用是减小ESL和ESR。下图的S21是射频的一个参数,S21 表示插入损耗或正向传输系数,也就是有多少能量被传输到目的端,这个值越大越好,理想值是1,即0dB,从中我们可以看出在10m和110M之间,拓宽了滤波范围。 另外并联减小ESR和ESL就更好理解了。从电容的实际模型分析可知,电容并联,ESR减小。大部分情况下我们用陶瓷电容搭配一个钽电容,就足以满足系统对电源噪声的去耦效果。  去耦半径: 我们在实际Layout过程中大多数资料中都会提到电容摆放要尽量靠近芯片,那么怎么靠近,靠近距离是多少呢? 我们知道信号在介质中传播需要一定的时间(电信号在真空中的传播速度大约是30万公里每秒,即3×10^8 m/s,约11800 mil/ns.在其他介质中,假设相对介电常数为Er,则传播速度为11800×Er^0.5 mil/ns;;一般PCB板FR4材料的介电常数是4左右,所以,电信号在其中的传播速度大约是11800/(4^0.5) = 5900 mil/ns。简略地记,电信号在PCB中的传播速度是在真空中的一半)。因此从发生局部电压扰动到电容感知到这一扰动之间有一个时间延迟。同样,电容的补偿电流到达扰动区也需要一个延迟。因此必然造成噪声源和电容补偿电流之间的相位上的不一致。特定的电容,对与它自谐振频率相同的噪声补偿效果最好,我们以这个频率来衡这种相位 关系。设自谐振频率为 f,对应波长为λ,补偿电流表达式可写为(A 是电流幅度,R 为需要补偿的区域到电容的距离,C 为信号传播速度。):  因此距离越近,相位差越小,补偿能传递越多,如果距离为 0,则补偿能百分之百传递到扰动区。这就要求噪声源距离电容尽可能的近,要远小于R/4 。实际应用中,这一距离最好控 制在R/40~R/50 之间,这是一个经验数据。 在实际layout布局中,所以一般靠近 IC 摆放。大容值电容去耦路径长,摆放位置相对远一点。所以电源,一般是先经过大电容,再经过小电容,再进入到 IC 芯片。 |