|

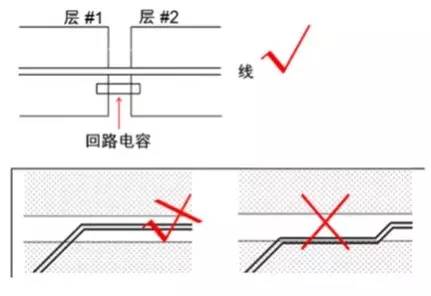

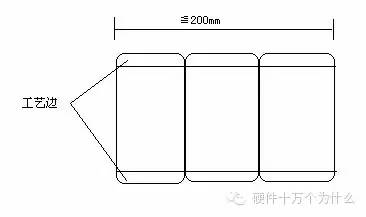

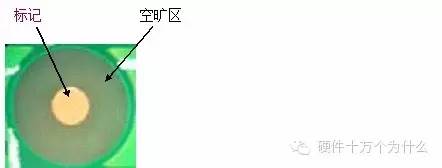

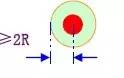

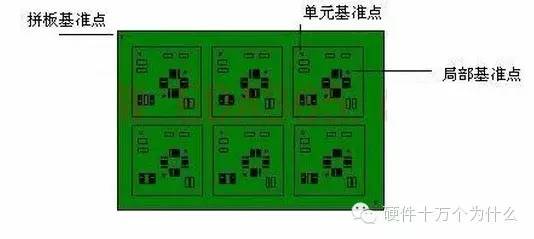

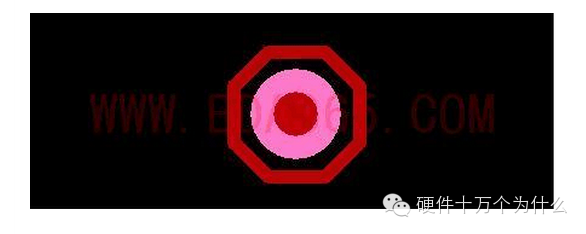

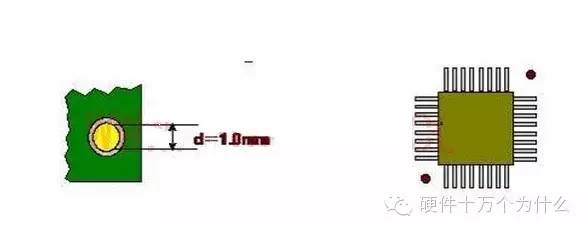

七、PCB EMI设计 在PCB设计中最常见的问题就是信号线跨越分割地或电源而产生EMI问题。为规避这种EMI问题下面就为大家介绍一下PCB设计中EMI设计的规范步骤。 1、IC的电源处理 保证每个IC的电源PIN都有一个0.1μF的去耦电容,对于BGA CHIP,要求在BGA的四角分别有0.1μF、0.01μF的电容共8个。对走线的电源尤其要注意加滤波电容,如VTT等。这不仅对稳定性有影响,对EMI也有很大的影响。一般去耦电容还是需要遵循芯片厂家要求。 2、时钟线的处理 1.建议先走时钟线。 2.频率大于等于66M的时钟线,每条过孔数不要超过2个,平均不得超过1.5个。 3.频率小于66M的时钟线,每条过孔数不要超过3个,平均不得超过2.5个 4.长度超过12inch的时钟线,如果频率大于20M,过孔数不得超过2个。 5.如果时钟线有过孔,在过孔的相邻位置,在第二层(地层)和第三层(电源层)之间加一个旁路电容、如图2.5-1所示,以确保时钟线换层后,参考层(相邻层)的高频电流的回路连续。旁路电容所在的电源层必须是过孔穿过的电源层,并尽可能地靠近过孔,旁路电容与过孔的间距最大不超过300MIL。 6.所有时钟线原则上不可以穿岛(跨越分割)。下面列举了穿岛的四种情形。 时钟、复位、100M以上信号以及一些关键的总线信号不能跨分割,至少有一个完整平面,优选GND平面。 时钟信号、高速信号和敏感信号禁止跨分割; 差分信号必须对地平衡,避免单线跨分割。(尽量垂直跨分割)  所有信号的高频返回途径都直接位于相邻层信号线的正下方。在信号下面设置一个实体层可以显著减少信号完整性和时序问题,这个实体层可以为该信号提供直接回路。当走线与层分割交叉不可避免时,应使用一个 0.01 uF 回路电容。如图所示,当使用回路电容时,应尽可能靠近信号线与层分割的交叉点布置回路电容。 6.1 跨岛出现在电源岛与电源岛之间。此时时钟线在第四层的背面走线,第三层(电源层)有两个电源岛,且第四层的走线必须跨过这两个岛. 6.2 跨岛出现在电源岛与地岛之间。此时时钟线在第四层的背面走线,第三层(电源层)的一个电源岛中间有一块地岛,且第四层的走线必须跨过这两个岛。 6.3 跨岛出现在地岛与地层之间。此时时钟线在第一层走线,第二层(地层)的中间有一块地岛,且第一层的走线必须跨过地岛,相当于地线被中断。 6.4 时钟线下面没有铺铜。若条件限制实在做不到不穿岛,保证频率大于等于66M的时钟线不穿岛,频率小于66M的时钟线若穿岛,必须加一个去耦电容形成镜像通路。以图6.1为例,在两个电源岛之间并靠近跨岛的时钟线,放置一个0.1UF的电容。 7.当面临两个过孔和一次穿岛的取舍时,选一次穿岛。 8.时钟线要远离I/O一侧板边500MIL以上,并且不要和I/O线并行走,若实在做不到,时钟线与I/O口线间距要大于50MIL。 9.时钟线走在第四层时,时钟线的参考层(电源平面)应尽量为时钟供电的那个电源面上,以其他电源面为参考的时钟越少越好,另外,频率大于等于66M的时钟线参考电源面必须为3.3V电源平面。 10.时钟线打线时线间距要大于25MIL。 11.时钟线打线时进去的线和出去的线应该尽量远。尽量避免类似图A和图C所示的打线方式,若时钟线需换层,避免采用图E的打线方式,采用图F的打线方式。 12.时钟线连接BGA等器件时,若时钟线换层,尽量避免采用图G的走线形式,过孔不要在BGA下面走,最好采用图H的走线形式。 13.注意各个时钟信号,不要忽略任何一个时钟,包括AUDIO CODEC的AC_BITCLK,尤其注意的是FS3-FS0,虽然说从名称上看不是时钟,但实际上跑的是时钟,要加以注意。 14.Clock Chip上拉下拉电阻尽量靠近Clock Chip。 3、I/O口的处理 1.各I/O口包括PS/2、USB、LPT、COM、SPEAK OUT、 GAME分成一块地,最左与最右与数字地相连,宽度不小于200MIL或三个过孔,其他地方不要与数字地相连。 2.若COM2口是插针式的,尽可能靠近I/O地。 3.I/O电路EMI器件尽量靠近I/O SHIELD。 4.I/O口处电源层与地层单独划岛,且Bottom和TOP层都要铺地,不许信号穿岛(信号线直接拉出PORT,不在I/O PORT中长距离走线)。 四、几点说明 1.对EMI设计规范,设计工程师要严格遵守,EMI工程师有检查的权力,违背EMI设计规范而导至EMI测试FAIL,责任由设计工程师承担。 2.EMI工程师对设计规范负责,对严格遵守EMI设计规范,但仍然EMI测试FAIL,EMI工程师有责任给出解决方案,并总结到EMI设计规范中来。 3.EMI工程师对每一个外设口的EMI测试负有责任,不可漏测。 4.每个PCB设计工程师有对该设计规范作修改的建议权和质疑的权力。EMI工程师有责任回答质疑,对工程师的建议通过实验后证实后加入设计规范。 5.EMI工程师有责任降低EMI设计的成本,减少磁珠的使用个数。 八、PCB设计的ESD抑止 PCB布线是ESD防护的一个关键要素,合理的PCB设计可以减少故障检查及返工所带来的不必要成本。在PCB设计中,由于采用了瞬态电压抑止器(TVS)二极管来抑止因ESD放电产生的直接电荷注入,因此PCB设计中更重要的是克服放电电流产生的电磁干扰(EMI)电磁场效应。本文将提供可以优化ESD防护的PCB设计准则。 1、电路环路 电流通过感应进入到电路环路,这些环路是封闭的,并具有变化的磁通量。电流的幅度与环的面积成正比。较大的环路包含有较多的磁通量,因而在电路中感应出较强的电流。因此,必须减少环路面积。 最常见的环路由电源和地线所形成。在可能的条件下,可以采用具有电源及接地层的多层PCB设计。多层电路板不仅将电源和接地间的回路面积减到最小,而且也减小了ESD脉冲产生的高频EMI电磁场。 如果不能采用多层电路板,那么用于电源线和接地的线必须连接成网格状。网格连接可以起到电源和接地层的作用,用过孔连接各层的印制线,在每个方向上过孔连接间隔应该在6厘米内。另外,在布线时,将电源和接地印制线尽可能靠近也可以降低环路面积。 减少环路面积及感应电流的另一个方法是减小互连器件间的平行通路。 当必须采用长于30厘米的信号连接线时,可以采用保护线。一个更好的办法是在信号线附近放置地层。信号线应该距保护线或接地线层13毫米以内。 将每个敏感元件的长信号线(>30厘米)或电源线与其接地线进行交叉布置。交叉的连线必须从上到下或从左到右的规则间隔布置。 2、电路连线长度 长的信号线也可成为接收ESD脉冲能量的天线,尽量使用较短信号线可以降低信号线作为接收ESD电磁场天线的效率。 尽量将互连的器件放在相邻位置,以减少互连的印制线长度。 3、地电荷注入 ESD对地线层的直接放电可能损坏敏感电路。在使用TVS二极管的同时还要使用一个或多个高频旁路电容器,这些电容器放置在易损元件的电源和地之间。旁路电容减少了电荷注入,保持了电源与接地端口的电压差。 TVS使感应电流分流,保持TVS钳位电压的电位差。TVS及电容器应放在距被保护的IC尽可能近的位置,要确保TVS到地通路以及电容器管脚长度为最短,以减少寄生电感效应。 九、PCB生产中Mark点设计 1.pcb必须在板长边对角线上有一对应整板定位的Mark点,板上集成电路引脚中心距小于0.65mm的芯片需在集成电路长边对角线上有一对对应芯片定位的Mark点;pcb双面都有贴片件时,则pcb的两面都按此条加Mark点。 2.pcb边需留5mm工艺边(机器夹持PCB最小间距要求),同时应保证集成电路引脚中心距小于0.65mm的芯片要距离板边大于13mm(含工艺边);板四角用Ф5圆弧倒角。pcb应采用拼板方式,从目前pcb翅曲程度考虑,最佳拼接长度约为200mm,(设备加工尺寸:长度最大为330mm;宽度最大为250mm),在宽度方向尽量不拼以防止在生产过程中弯曲。如下图:  3.MARK点作用及类别 Mark点也叫基准点,为装配工艺中的所有步骤提供共同的可测量点,保证了装配使用的每个设备能精确地定位电路图案。因此,Mark点对SMT生产至关重要 4.我部推荐的MARK点设计规范 1) 形状:建议Mark点标记为直径:R=1.0mm实心圆; 2) 组成一个完整的MARK点包括:标记点(或特征点)和空旷区域。  3) 位置:Mark点位于单板或拼板上的对角线相对位置且尽可能地距离分开;最好分布在最长对角线位置(如MARK点位置图)。 4) 为保证贴装精度的要求,SMT要求:每块PCB内必须至少有一对符合设计要求的可供SMT机器识别的MARK点,同时必须有单板MARK(拼板时),拼板MARK或组合MARK只起辅助定位的作用。 5) 拼板时,每一单板的MARK点相对位置必须一样。不能因为任何原因而挪动拼板中任一单板上MARK点的位置,而导致各单板MARK点位置不对称; 6) PCB上所有MARK点只有满足:在同一对角线上且成对出现的两个MARK,方才有效。因此MARK点都必须成对出现,才能使用(MARK点位置图)。 7) MARK点(空旷区边缘)距离PCB边缘必须≥5.0mm(机器夹持PCB最小间距要求)(如MARK点位置图)。  (MARK点位置图) 8) 尺寸 A. Mark点标记最小的直径为1.0mm,最大直径是3.0mm,Mark点标记在同一块印制板上尺寸变化不能超过25 微米; B. 特别强调:同一板号PCB上所有Mark点的大小必须一致(包括不同厂家生产的同一板号的PCB); C. 建议将所有的Mark点标记直径统一设为1.0mm。 9) 空旷区要求 在Mark点标记周围,必须有一块没有其它电路特征或标记的空旷面积。空旷区圆半径 r≥2R , R为MARK点半径,r达到3R时,机器识别效果更好。  10) 材料 Mark点标记可以是裸铜、清澈的防氧化涂层保护的裸铜。如果使用阻焊(soldermask),不应该覆盖Mark点或其空旷区域 11) MARK点的光亮度应保持一致。 12) 平整度:Mark点标记的表面平整度应该在15 微米之内。 13) 对比度 A. 当Mark点标记与印制板的基质材料之间有高对比度时可达到最佳的识别性能 B. 对于所有Mark点的内层背景必须相同 以下在补点他人这方面的经验,作为参考 MARK点分类: 1)Mark点用于锡膏印刷和元件贴片时的光学定位。根据Mark点在PCB上的作用,可分为拼板Mark点、单板Mark点、局部Mark点(也称器件级MARK点), 2)拼板的工艺边上和不需拼板的单板上应至少有三个Mark点,呈L形分布,且对角Mark点关于中心不对称。 3)如果双面都有贴装元器件,则每一面都应该有Mark点。 4)需要拼板的单板上尽量有Mark点,如果没有放置Mark点的位置,在单板上可不放置Mark点。 5)引线中心距≤0.5 mm的QFP以及中心距≤0.8 mm的BGA等器件,应在通过该元件中心点对角线附近的对角设置局部Mark点,以便对其精确定位。 6)如果几个SOP器件比较靠近(≤100mm)形成阵列,可以把它们看作一个整体,在其对角位置设计两个局部Mark点。 设计说明和尺寸要求: 1)Mark点的形状是直径为1mm的实心圆,材料为铜,表面喷锡,需注意平整度,边缘光滑、齐整,颜色与周围的背景色有明显区别;阻焊开窗与Mark点同心,对于拼板和单板直径为3mm,对于局部的Mark点直径为1mm, 2)单板上的Mark点,中心距板边不小于5mm;工艺边上的Mark点,中心距板边不小于3mm。 3)为了保证印刷和贴片的识别效果,Mark点范围内应无焊盘、过孔、测试点、走线及丝印标识等,不能被V-CUT槽所切造成机器无法辨识。 4)为了增加Mark点和基板之间的对比度,可以在Mark点下面敷设铜箔。同一板上的Mark点其内层背景要相同,即Mark点下有无铜箔应一致。 5)对于单板和拼板的Mark点应当作元件来设计,对于局部的Mark点应作为元件封装的一部分设计。便于赋予准确的坐标值进行定位。 PCB设计之光学基准点! 在有贴片元件的PCB板上,为了对PCB整板进行定位,通常需要在PCB板的四个角放置光学定位点,一般放三个即可。常见的基准点主要有三种:拼板基准点,单元基准点,局部基准点。  基准点结构 (1)拼板基准点和单元基准点 形状/大小:直径为40mil 的实心圆。阻焊开窗:和基准点同心的圆形,大小为基准点直径的两倍。在 2mm直径的边缘处要求有一圆形或八边形的铜线作保护圈用。同一板上的光学定位基准符号其内层背景要相同,即三个基准符号下有无铜箔应一致。  (2)局部基准点 间距≤0.4mm的QFP和间距≤0.8mm BGA、CSP、FC等器件需要放置局部基准点。 大小/形状:直径为40mil 的实心圆。 阻焊开窗:大小按普通焊盘处理,外圈铜环可不要。  |