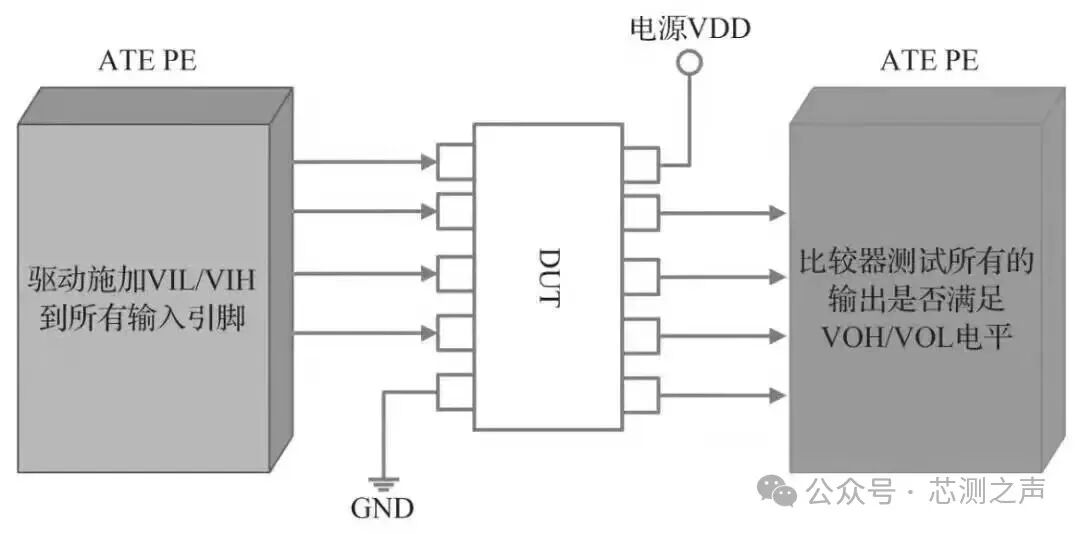

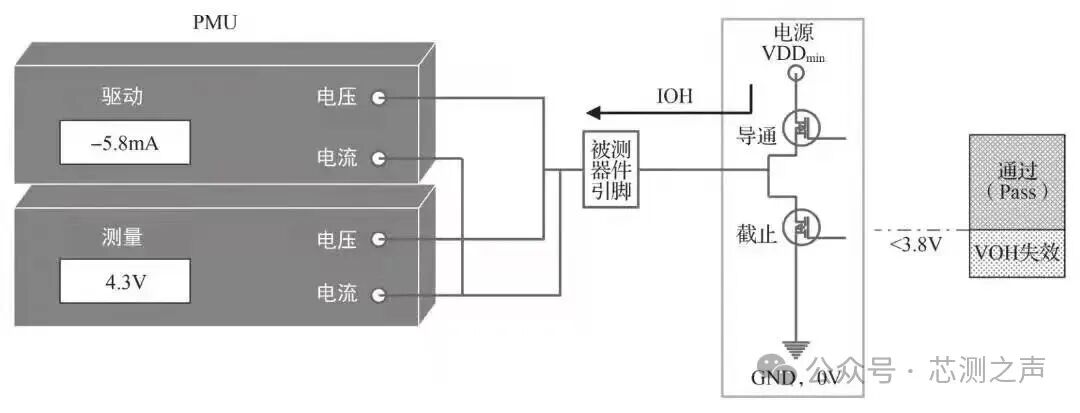

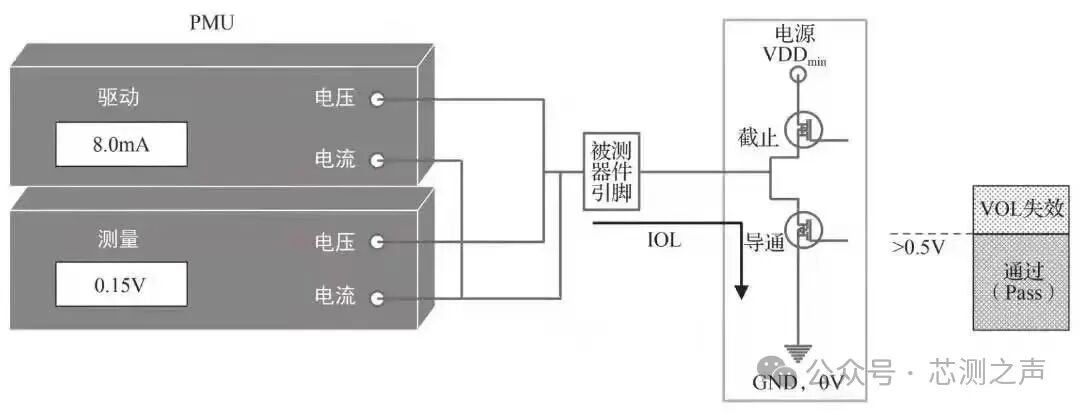

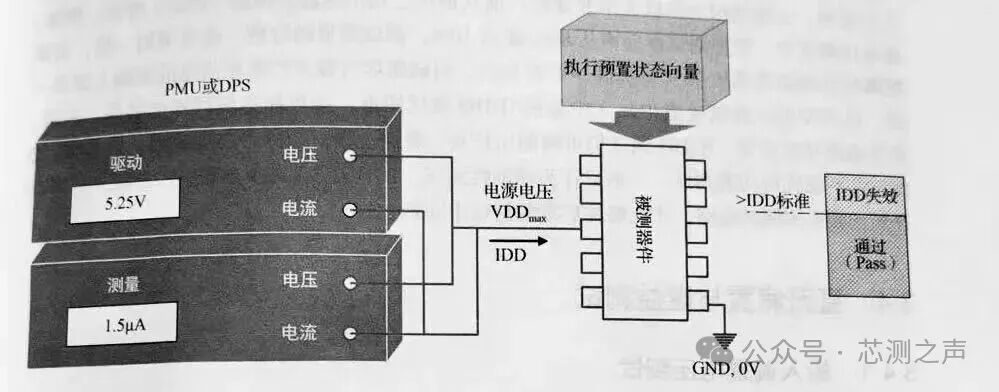

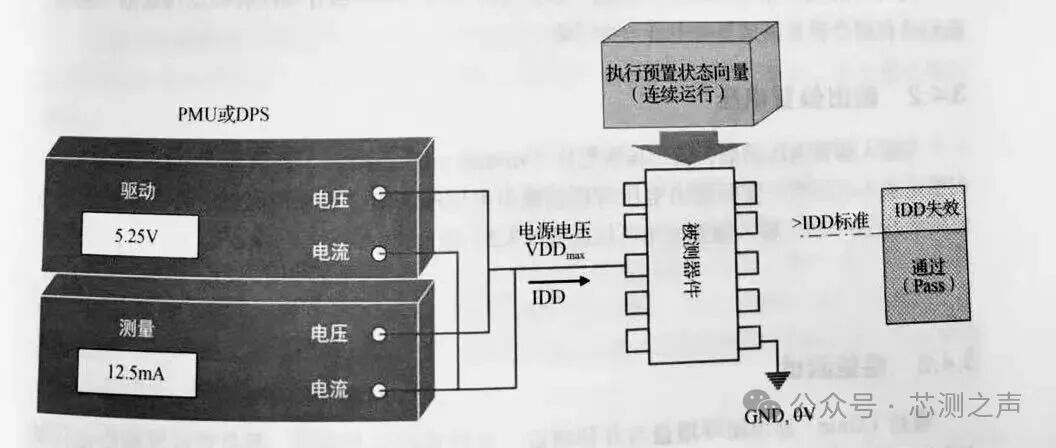

数字芯片DC参数测试详解:VIH/VIL/VOH/VOL/IOS/IDD测试原理与方法打造可靠芯片,从精准测试开始 在数字芯片的设计和制造过程中,DC参数测试是确保芯片质量的关键环节。今天我们将深入探讨数字芯片测试中VIH、VIL、VOH、VOL、IOS和IDD等核心参数的测试原理与方法。 一、DC参数测试概述 DC参数测试主要用于验证芯片在不同状态下的电流、电压和阻抗特性,确保其符合设计规格要求。对大多数DC参数来说,实质上是在测试半导体的电阻特性,而解释这种特性用的是欧姆定律。 通过DC测试,我们可以判断芯片是否存在物理缺陷(如引脚短路、bond wire缺失、静电损坏等),也可以评估芯片的功耗、驱动能力等关键指标。 二、输入电平阈值测试:VIH与VIL 测试目的 VIH(输入高电平)是输入引脚正确识别为逻辑1的最小电压;VIL(输入低电平)是输入引脚正确识别为逻辑0的最大电压。这两个参数确保了芯片能正确识别输入信号。  测试方法(加流测压,FIMV) 测试时,在规定温度下将芯片放入测试平台,将所有IO置为输入状态,分别在VDDmax和VDDmin模式下验证VIL和VIH。 具体操作是:通过测试仪器施加规定的输入电流,然后测量对应的电压值,确保在输入电流下电压值符合逻辑电平识别要求。 示例:对于典型的CMOS器件,VIH通常是0.7×VDD,VIL通常是0.3×VDD。这意味着在5V供电系统中,VIH约为3.5V,VIL约为1.5V。 三、输出驱动能力测试:VOH与VOL 测试目的 VOH(输出高电平)表示引脚输出逻辑1时的最低电压;VOL(输出低电平)表示引脚输出逻辑0时的最高电压。它们共同衡量的是引脚Buffer在输出高电平或低电平时的阻抗。 测试方法 VOH/IOH测试:先将待测引脚设置为高电平输出,向引脚施加恒定的IOH(输出高电平电流),等待1-5毫秒后测量电压值。如果测得电压低于VOH规格,则测试失败。  VOL/IOL测试:先将待测引脚设置为低电平输出,向引脚施加恒定的IOL(输出低电平电流),同样等待稳定后测量电压。如果电压高于VOL规格,则测试失败。  注意事项 测试时需要设置电压钳位,防止电压异常损坏测试设备。同时要注意,IOL是正值(电流从PMU流向DUT),而IOH是负值。 四、短路输出电流测试:IOS 测试目的 IOS(短路输出电流)衡量当引脚输出高电平但被短路至低电压时的输出阻抗,确保在最坏负载条件下输出电流不会过大。这也表示了DUT引脚可提供容性负载充电的最大瞬时电流。 测试方法 先给芯片施加VDDmax电压,通过预处理使引脚输出高电平。然后用PMU将引脚拉低至0V,测量输出电流并与标称值对比。 安全注意事项:IOS测试需要特殊的保护逻辑以避免热切换。测试时间必须极短(通常不超过1秒),且一次只能测试一个输出引脚,防止芯片过热损坏。 典型规格 五、电源电流测试:IDD 测试目的与分类 IDD表示的是CMOS电路中从漏极(D)到漏极(D)的电流(TTL电路中称为ICC)。IDD测试分为三种类型: 1. Gross IDD:粗略测试,用于快速筛选功耗过大的缺陷芯片 2. 静态IDD:测量芯片在非活动状态下的功耗 3. 动态IDD:测量芯片在最大工作频率下的功耗 Gross IDD测试 Gross IDD测试是芯片上电后的第一个测试,目的是判断能否继续测试DUT。如果Gross IDD测试不通过(电流过大),就停止后续测试。 测试方法:通过重置将所有输入引脚设低/高电平(VIL设置为0V、VIH设置为VDD),所有输出引脚空载,然后测量流入VDD引脚的总电流。 静态IDD测试  静态IDD测试测量的是流入VDD引脚的总电流,需要DUT运行在最低功耗模式下。与Gross IDD的区别是,静态IDD测试已有预处理程序,通过预处理后再进行测试。 IDDQ测试:这是静态IDD的一种特殊形式,测量CMOS电路中所有管子都处于静止状态时的电源总电流,用于提升测试覆盖率。 动态IDD测试  动态IDD测试的是DUT在动态执行功能时(通常为最大工频)消耗的电流,确保其不超过标称值。 测试方法:用PMU或DPS在器件在最高工作频率时运行一段连续的测试向量,测量流入VDD引脚的总电流,与规格书对比。 六、测试实例与故障排查 典型测试流程 1. 开短路测试(Open-Short Test) 2. Gross IDD测试 3. 功能测试 4. 其他DC参数测试(VIH/VIL/VOH/VOL等) 5. 静态/动态IDD测试 常见故障排查 当IDD测试出现异常时,建议按以下步骤排查: 1. 先用万用表测量是否有短路,检查Socket上电到地后的电阻 2. 检查电源端电压是否被下拉 3. 检查旁路电容是否适当 4. 确认芯片与测试座的接触良好 重要提示:测试不通过时,应先排除非器件问题。将器件从Socket取走,空跑程序,电流应为0。如果不是,说明测试系统本身存在问题。 DC参数测试是数字芯片测试的基础,直接关系到芯片的性能和可靠性。通过精确测量VIH、VIL、VOH、VOL、IOS和IDD等参数,我们可以全面评估芯片的输入输出特性、驱动能力和功耗性能。 随着芯片工艺的不断进步,DC测试技术也在持续发展,未来将面临更多挑战和机遇。掌握这些基础测试原理和方法,对于芯片设计、测试和应用工程师都至关重要。 这是一个非常专业且切中要害的问题。在芯片测试中,对输入/输出缓冲器(I/O Buffer)进行测试时,特别是测试其驱动强度(通常称为IOS,I/O Short Circuit Current),将VDD设置为最大值(VDDmax)是至关重要的。这背后的原理涉及最坏情况测试、设计余量验证和可靠性保证。 以下是详细的原因分析: 一、核心原因:创造最严苛的测试条件 芯片的规格书(Datasheet)中给出的参数(如IOS)必须保证在所有允许的电源电压范围内都满足要求。因此,测试必须在最坏情况下进行,而VDDmax正是导致IOS最大的条件。 1. 从晶体管电平理解:驱动能力与VDD直接相关 一个输出缓冲器(Output Buffer)本质上是由PMOS和NMOS管组成的最终驱动级。 • 当输出为高电平(逻辑‘1’)时,上拉的PMOS管导通。其导通电阻(Ron)和提供的源电流(Source Current)能力与VDS(即VDD - VOUT)有关。 • 当输出为低电平(逻辑‘0’)时,下拉的NMOS管导通。其导通电阻和吸收电流(Sink Current)能力与VDS(即VOUT - GND)有关。 在进行IOS测试时,我们将输出端强制一个电压(通常为VDD/2),然后测量电流。 此时: • PMOS的Vds = VDD - Vforce_voltage • NMOS的Vds = Vforce_voltage - 0 关键点: VDD越大,加在导通的PMOS或NMOS上的Vds就越大。根据晶体管的饱和电流公式(Ids ∝ Vds² 在饱和区),Vds越大,晶体管能产生的驱动电流(Ids)就越大。 因此,在VDDmax下,当输出被强制到一个中间电压时,PMOS和NMOS都处于深度导通状态,并且有最大的电压差来驱动电流,从而产生可能的最大短路电流。 2. 测试目的:确保在最坏情况下不超标 IOS测试的主要目的之一是验证当输出发生意外短路(例如,两个输出脚碰在一起,一个试图输出高,一个试图输出低)时,电流不会大到足以损坏芯片本身。 • 如果我们在VDDmax下测得的IOS值仍然在安全范围内(即小于设计上限,不会因功耗过大而烧毁输出管),那么在任何更低的VDD电压下,IOS只会更小,因而更加安全。 • 反之,如果只在典型VDD下测试,可能在VDDmax时电流会超出安全限值,导致芯片在电压上限工作时面临可靠性风险甚至永久损坏。 二、其他重要原因 1. 验证设计余量(Design Margin) 芯片设计必须留有足够的余量以应对工艺波动、电压波动和温度变化(即PVT变化)。在VDDmax下测试IOS,是直接验证电压(V)这个维度上的设计余量。这确保了芯片在标称的“最大允许电压”下,其性能(这里是驱动电流)和可靠性仍然符合规范。 2. 与规范保持一致 芯片的数据手册(Datasheet)中,IOS的规范值通常是在规定的VDD范围上限下测得的。为了证明芯片符合自己发布的规格,测试必须在相同的条件下进行。客户也会期望芯片在最大工作电压下仍能满足所有电气参数。 测试场景示例:IOS测量 以测量输出高电平时的短路源电流(I_OH)为例: 1. 设置条件: 将器件的VDD电源设置为最大值(VDDmax)。配置逻辑输入使输出试图驱动为高电平(‘1’)。 2. 施加负载: 使用精密测量单元(PMU)或类似设备,在输出引脚上强制一个电压,通常为VDD/2(这是模拟一个“短路”到中间电平的最坏情况)。 3. 测量电流: 测量从芯片输出引脚流出的电流。这个测量到的电流值就是I_OH(或更广义的IOS)。 4. 判断: 将测得的电流值与数据手册中规定的最大值和最小值进行比较。它必须在范围内,既不能太小(驱动能力不足),也不能太大(有烧毁风险)。 在芯片测试中,对IOS测试使用VDDmax,根本原因在于风险管理和质量保证: • 电气角度: VDDmax创造了产生最大驱动电流的条件,这是最严苛的应力测试。 • 可靠性角度: 它确保了芯片在允许的最高工作电压下,输出级也不会因过流而损坏。 • 合规性角度: 它保证了测试条件与数据手册规格定义的条件一致,验证了芯片在整个工作电压范围内的性能。 简而言之,在VDDmax下测试IOS,就是为了验证“即使在最坏的电压条件下,芯片仍然是安全且符合规范的” |