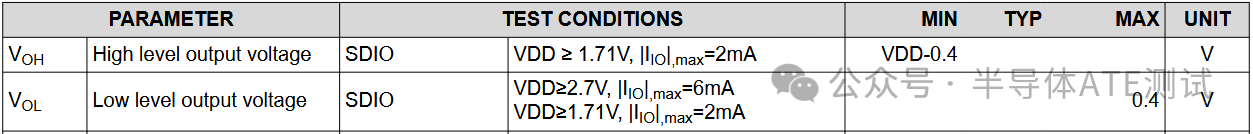

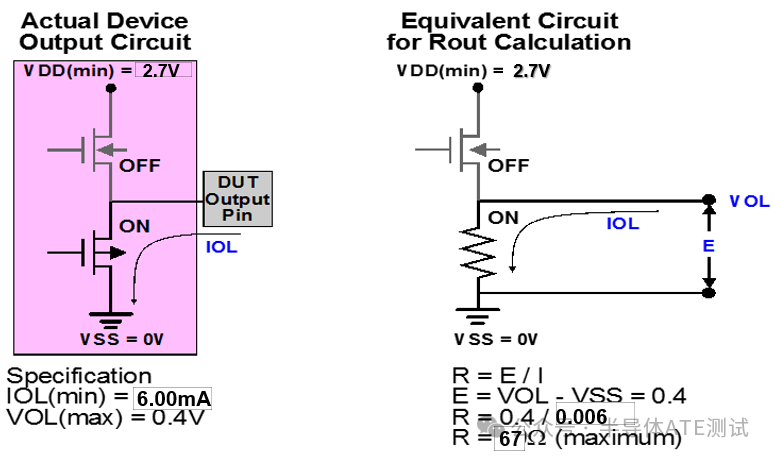

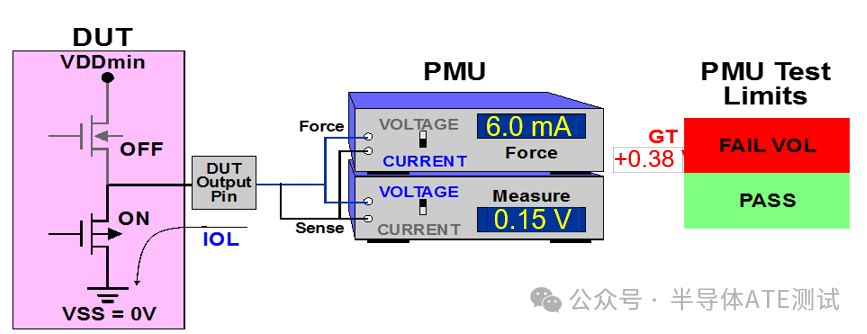

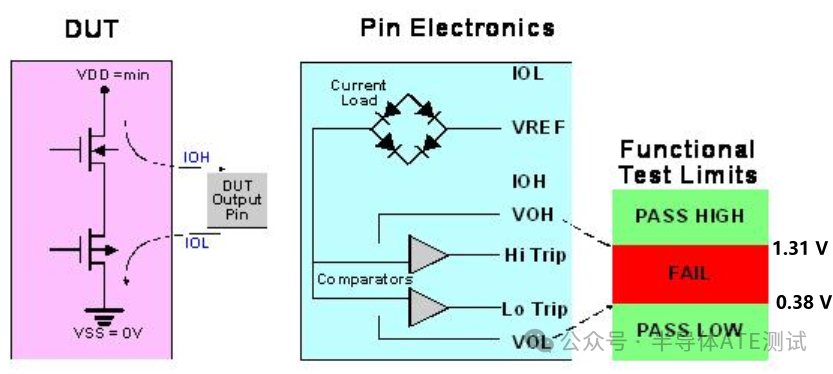

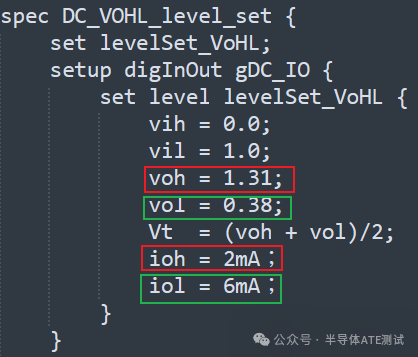

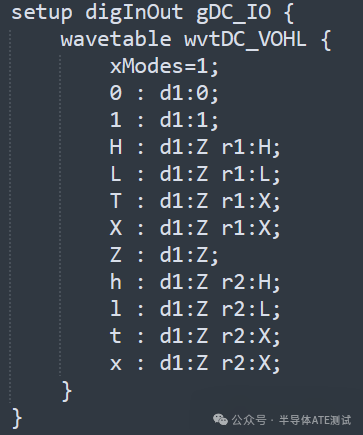

书接上文,咱们继续来了解DUT数字PIN脚输出带载能力的测试,此项也是ATE DC 测试的常见测试项:VOL/IOL。一、参数定义 VOL:DUT 输出逻辑0时,输出管脚上所能承受的最高电压即输出电平的最大值。 IOL:DUT 正确输出逻辑0时,输出管脚上的负载电流(此时电流方向:流入DUT)。 举个栗子,如下是TI 的MSPM0C1104 芯片 DC spec中关于VOL/IOL 参数信息:  · 当供电电源: VDD = 2.7V 时,该芯片I/O channel 在输出逻辑 0 时,能承受的最大负载电流为6mA,此时DUT 所能正确识别输出逻辑0 的最大电压值为0.4V。 · 当供电电源: VDD = 1.7V 时,该芯片I/O channel 在输出逻辑 0 时,能承受的最大负载电流为2mA,此时DUT 所能正确识别输出逻辑0 的最大电压值为0.4V。 * 不用电源电压下,I/O channel的带载能力是不同的,相同输出模式(输出逻辑0或逻辑1)下,电源电压越大,I/O 的带载能力越强,如本例,同为SDIO(标准I/O channel), Vdd 2.7V模式,I/O channal 在输出逻辑0 时带载能力是Vdd 1.7V模式,I/O channel 在输出逻辑0时带载能力的3倍(6mA/2mA)。 二. 测试目的  VOL/IOL 测试实际上测量的是输出管脚在输出逻辑电平0时的输出电阻,此测试的目的是确保输出阻抗满足设计要求,保证输出管脚在输出逻辑0时,在严格的VOL 条件下,输出管脚可以吸收Spec 中所定义的IOL 电流。换句话说,在输出逻辑0时,DUT 的输出管脚必须能够吃进DataSheet 中定义的最大电流而保证正确的逻辑状态。 因为VOH/IOH, VOL/IOL 测试的本质是测量IC I/O channel 在不同输出逻辑电平时的输出阻抗,故对于VOH/IOH & VOL/IOL 的测量我们可以有两种方式: 1.按照Spec 提供Power电压,Pre-condition后, force voltage(VOH/VOL) , measure Current(IOH/IOL) 2. 按照Spec 提供Power电压,Pre-condition后, force current(IOH/IOL) , measure voltage(VOH/VOL) 实际规划测试方案时,根据所选机台进行电压/电流 测试的测试精度,测试时间,Range 区间等参数来选择合适测试方案。 *一般测试机台有Per Pin 的电流负载(active load),无Per Pin 的电流测量meter,故针I/O 在不同逻辑电平状态下,输出阻抗的参数的测量大多选取 Force/Load current Measure Voltage 的方式进行 三. 测试方法 与VOH/IOH 测试相同,VOL/IOL 的测试也有静态测试和动态测试两种方式。 静态测试:  Step1. 提供 VDDmin = 2.7V 给Power Pin(worse case) Step2. 设置Pass/Fail Limit:<0.4 V (考虑gand band 可将Limit 设置为0.38V (0.4V±5%)) Step3.设置Voltage measurement Clamp 0.5V(Clamp ≥ Max(Measure Range, Limit)) Step4. Run Pre-condition pattern 将DUT 置于输出逻辑0 的状态 Step5. 等待1~5ms 后测量输出电压值 Step6. 若输出电压值在Limit 范围内则Pass,反之Fail.High Light: *需设置VDD min 作为此测试最差情形 *IOL 此时为正电流,电流方向为:灌入DUT。 * 测试时需要设置Clamp 电压,Calmp Voltage ≥ Max(measure range, Limit) Trouble Shooting: 1.Pre-condition pattern Pass & VOL 电压正常-->不用debug爽歪歪~~ 2. Pre-condition pattern Pass,VOL电压实测值高于Limit,测试Fail. § 此时的VOL 测试电压应该处于Limit 与Clamp 电压之间,输出阻抗略大,可能原因:测试接触阻抗叠加,器件制造缺陷 § 交换Site进行测试排除测试硬件引起的Fail § 交换芯片进行测试,排除DUT 间差异 § 利用万用表测试当前状态下DUT 输出阻抗,排除测试程序问题 § 利用EVB board 实测相同芯片的输出阻抗,排除接触阻抗叠加导致的测试Fail(若能确认是因为接触阻抗叠加导致的测试Fail,可与研发商讨确认适当的Relex 测试Limit) 3.Pre-condition pattern Fail, VOL实测电压值等于程序中设置的Clamp 电压,远高于Limit,测试fail。 *此种情况就彰显了测试Clamp 设置的必要性!!! 动态测试:  Step1. Level / program 中设定电源电压为 VDDmin = 2.7V, Step2. Level 同VOH/IOH 测试项 tep3. 断开待测Pin 脚的 PPMU relay,闭合AC relay Step4. Run Pre-condition pattern 将待测Pin 脚置于输出逻辑0的状态 Step5. Run VOL/IOL test pattern(在Step4 的pre-condition Pattern 后针对待测I/O Pin 脚增加'X'-> 等待 和’L‘->比较VOL) Step6. 读取Pattern Pass Fail 结果 至此我们可以把DUT I/O channel 输出DC 参数测试的Level 和 wavetable combine 在一起,减少程序Level set 和wavetabel set 数目: DC_VoHL_Level:  DC_VoHL_Wavetable:  |