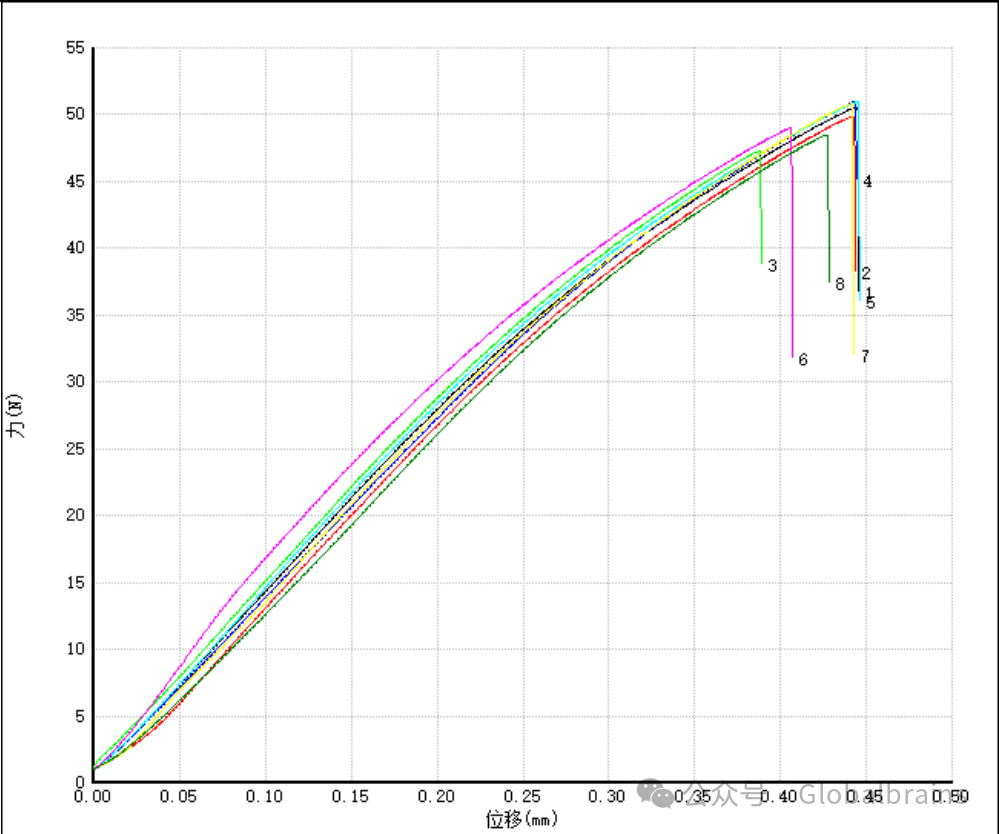

随着电子产品的不断发展和升级,半导体芯片的应用越来越广泛,而半导体芯片的可靠性也受到越来越多的关注。芯片三点弯折测试是对半导体芯片的机械性能进行评估的重要方法之一。该测试方法能够模拟出半导体芯片在使用过程中所可能遭受的各种弯曲应力,从而对芯片的机械可靠性进行有效的评估和判断。一、基本定义与原理三点弯折测试(Three-Point Bending Test, 3PB Test)是一种通过施加集中载荷评估材料或结构件弯曲性能的标准化方法。测试时,样品被置于两个支撑点上,并在中点施加垂直载荷,通过测量变形与载荷关系分析材料的抗弯强度、刚度和断裂韧性。· 核心原理:通过三点加载形成对称弯矩,使材料在中点处承受最大弯曲应力,模拟实际工况下的动态弯曲应力 适用对象:金属、陶瓷、复合材料、BGA封装基板等脆性或低塑性材料。  压力与位移曲线-图2 二、测试步骤与参数 1,样品制备 § 根据标准(如GB/T 232-2010、YB/T 5349-2006)加工试样,通常为矩形或圆柱形,确保表面无缺陷。 § 存储类BGA产品需重点关注基板厚度、焊点间距等参数 2,设备设置 § 支撑跨距(Span):调整支撑点间距,跨距越小则局部应力越大,需根据材料类型(如陶瓷基板) § 优化:调整支撑点间距,跨距越小则局部应力越大,需根据材料类型(如陶瓷基板)优化。 加载速率:模拟实际工况(如接口插拔速度),影响断裂模式与数据精度。 3,加载与数据记录 § 施加垂直载荷至中点,实时记录载荷-位移曲线,直至试样断裂或达到预设变形量。 § 关键数据:弯曲强度(最大弯曲应力)、弯曲模量(弹性阶段应力-应变比)、断裂韧性(裂纹扩展阻力)。 三、存储类BGA产品测试要点1,测试目标 § BGA焊点可靠性:评估焊点在动态弯曲应力下的抗断裂能力,防止电气连接失效。 § 基板抗裂性:验证陶瓷基板或有机基板在弯曲载荷下的抗碎裂性能。 2,典型失效模式 · 焊点断裂:因反复弯曲应力导致裂纹从焊点界面扩展,引发电气开路。 · 基板分层/碎裂:脆性基板(如陶瓷)在最大应力区域发生断裂,导致封装结构失效。 3,参数优化建议 · 跨距选择:根据基板厚度调整支撑间距,避免因跨距过小导致局部应力集中。 · 加载速率:模拟实际振动或插拔场景,高速加载可加速疲劳失效的暴露。 四、与其他弯曲测试的对比

五、总结三点弯折测试通过集中载荷模拟动态弯曲应力,是评估存储类BGA产品中焊点与基板机械可靠性的核心方法。其核心价值在于量化材料的抗弯强度、刚度及断裂韧性,为封装设计与工艺优化提供数据支撑。测试中需重点关注跨距、加载速率等参数的匹配性,以准确反映实际工况下的失效风险。 |