|

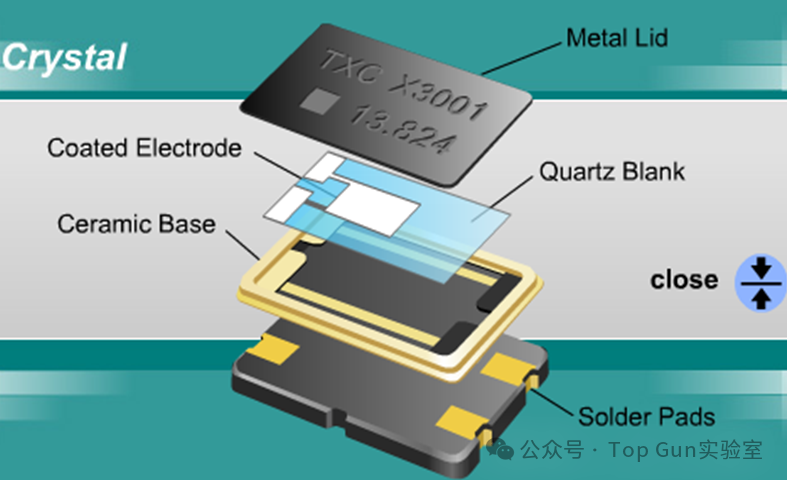

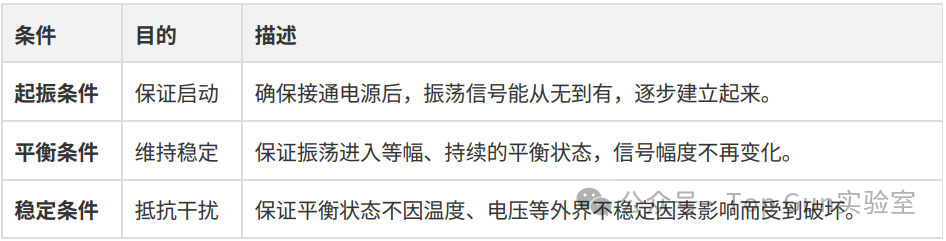

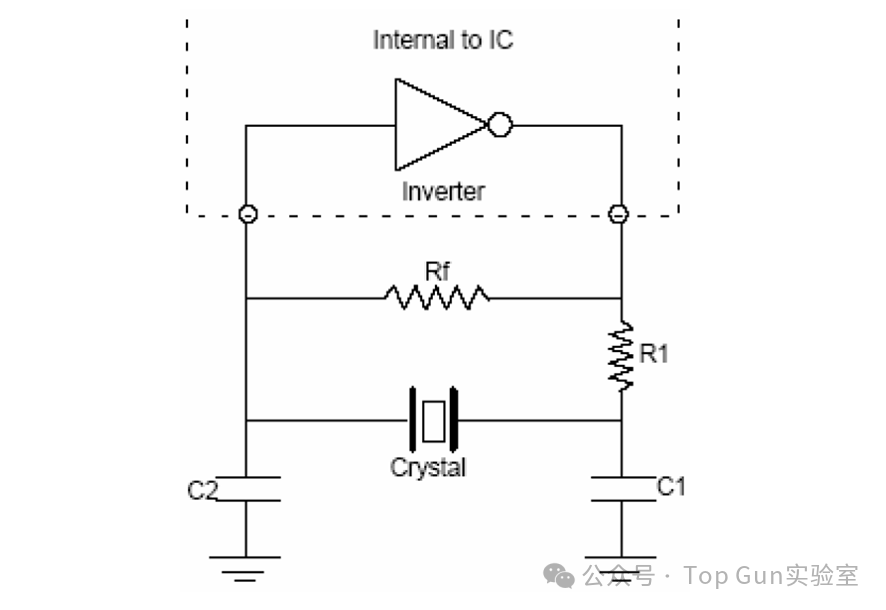

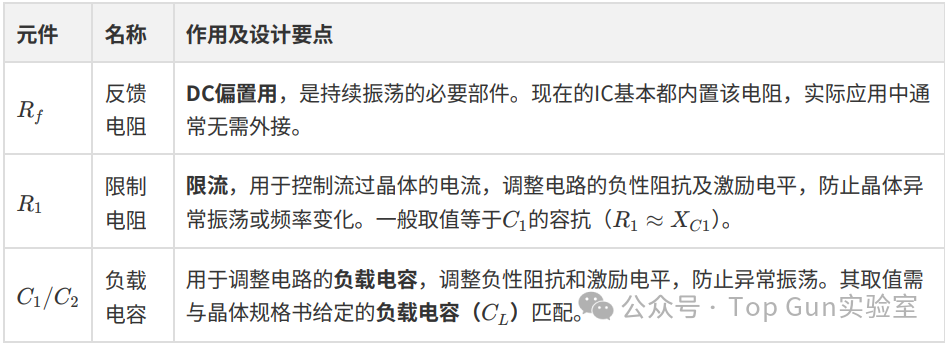

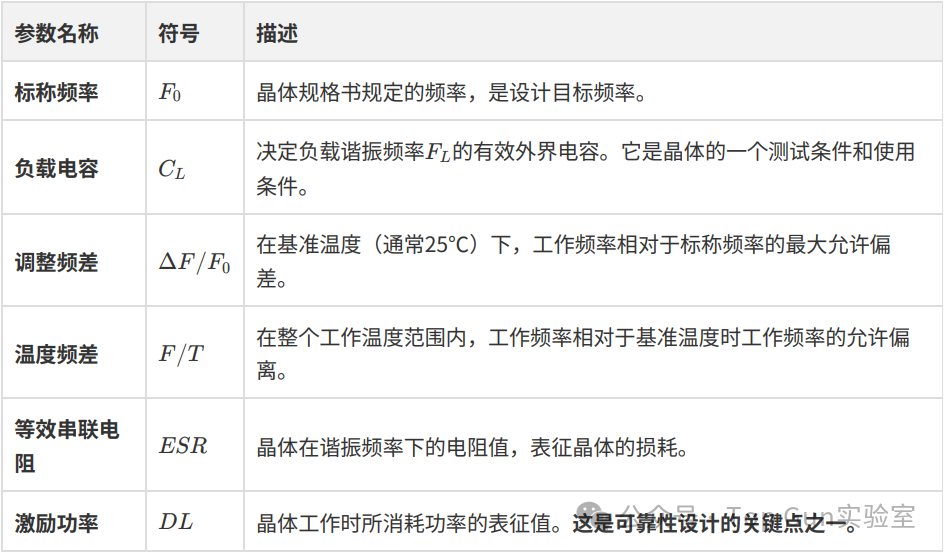

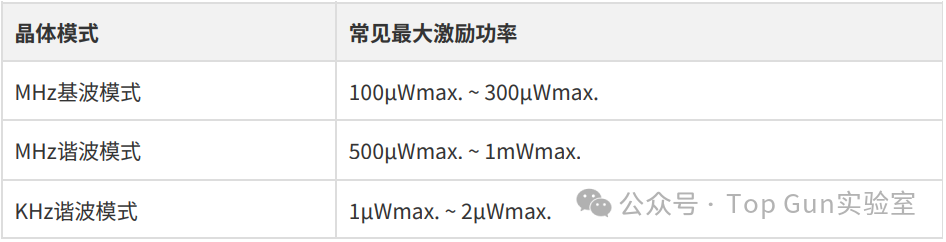

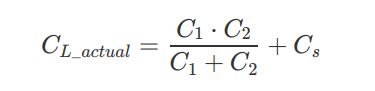

在电子设备中,晶体谐振器(简称晶体)如同数字电路的“心脏”,提供稳定、精确的时钟信号。然而,要让这颗“心脏”可靠地跳动,并非简单地将晶体接入电路即可。它需要精妙的振荡电路配合,并关注一系列关键参数。本文将深入浅出地解析晶体的工作原理、核心参数,以及工程师在可靠性应用中必须关注的设计要点。  一、晶振是如何“跳动”的?——典型工作原理 晶体谐振器本身是一个无源器件,它需要配合外部的振荡电路才能产生持续的电信号。这与晶体振荡器(有源器件,内部已集成振荡电路)是本质区别。 1. 振荡的三大条件 要实现可靠的持续振荡,电路设计必须满足以下三个核心条件:  2. 典型外围电路解析 振荡电路通常由放大电路、正反馈网络、选频网络(即晶体)和稳幅电路组成。在现代设计中,放大电路和正反馈网络通常已集成在主IC内部。因此,晶体外围电路的设计重点在于稳幅电路,以确保安全振荡和频率偏差符合要求。   二、掌握核心指标——晶体谐振器主要参数解析 理解晶体的核心参数是进行电路设计的基础。以下是几个最重要的参数:  激励功率(DL):不可忽视的“能量” 激励功率是维持晶体正常起振和稳定振荡所需的能量。设计时必须严格控制: o 激励功率过小:可能导致晶体无法起振,或信号杂音比变小,影响短期稳定度。 o 激励功率过大:会导致石英晶片因机械形变超过弹性限度而引起永久性的频率变化,甚至可能导致晶片碎裂而停振。 规格书通常记载的是最大激励功率。不同模式的晶体最大激励功率参考值如下:  使用者可通过调节限制电阻R1和负载电容C1/C2的值来调节实际的激励功率。 三、可靠性设计的“生命线”——负性阻抗(-R) 负性阻抗(-R)不是晶体的规格参数,却是振荡电路设计中最重要的性能指标之一。 1. 负性阻抗的概念 晶体的等效电路中存在一个振动摩擦损耗电阻R(即ESR),它会消耗振荡电路的能量。如果能量耗尽,晶体就会停止振荡。负性阻抗(-R)来源于振荡电路中的放大电路,它是一个能量源。当这个能量源(-R)大于振荡电路的损耗(ESR)时,回路才能维持稳定振荡。 2. 核心要求:-R必须足够大 为了确保晶体电路能够安全起振和稳定振荡,负性阻抗必须满足以下条件: -R≥3~10倍的ESR •低于3倍:可能导致晶体不起振、振荡不稳定或启动时间延长。 •5倍以上:是业界普遍推荐的安全设计裕量,通常消费类≥3倍,工控类≥5倍,汽车电子≥10倍。 注意:当线路负载电容值增大或频率往高频方向偏时,负性阻抗会变小,因此在设计时需要留足裕量。 四、工程师必看——负载电容(CL)的精细化设计 负载电容的匹配性直接决定了晶体电路的频率精度。只有当电路的负载电容与晶体规格书指定的CL一致时,时钟信号的频率才能与标称值一致。 1. 负载电容的计算 电路中的实际负载电容CL_actual由外接电容C1、C2和寄生电容Cs共同决定:  其中: •Cs:包含IC内部杂散容值、PCB布线间的电容量、板层间的寄生电容等。一般典型值取 5pF。 •C1/C2:用于调整电路的负载电容。 2. CL选择的三个关键点 在实际应用中,负载电容的选用需要注意以下三点: 电容要求:C1和C2的值一般要求相等,且要求使用温度特性好的电容(如NPO材质),以保证频率稳定。 精度要求:C1和C2的取值精度要求在10%以内。 调试标准:C1和C2的调试取值,应以已知频偏的晶体部品为参考,而非晶体规格书中的标称频率。换言之,取值判断标准是以所得频率靠近已知频偏为佳,而非靠近规格值的0ppm为佳。 3. 频率偏差与CL的关系 当 CL_actual大于规格书的CL值时,晶体频率小于标称频率。 o 当 CL_actual 小于规格书的CL值时,晶体频率大于标称频率。 因此,即使标称频率相同的晶体,如果它们的负载电容CL不同,也不能贸然互换,否则会导致时钟频率偏差过大。 总结 晶体谐振器的可靠性设计是一个系统工程,它要求工程师不仅要关注晶体本身的参数,更要关注外部振荡电路的性能。通过精确控制负载电容来保证频率精度,通过确保负性阻抗的裕量来保证起振稳定性,并通过调节激励功率来保证晶体的长期可靠性。 |