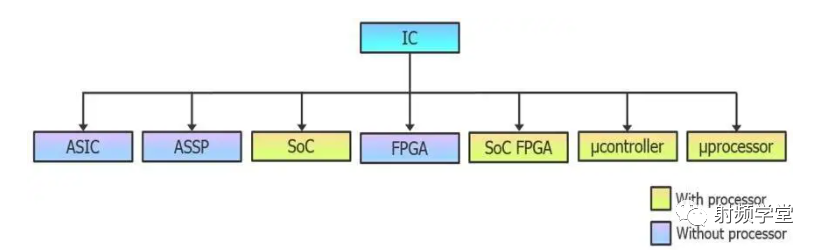

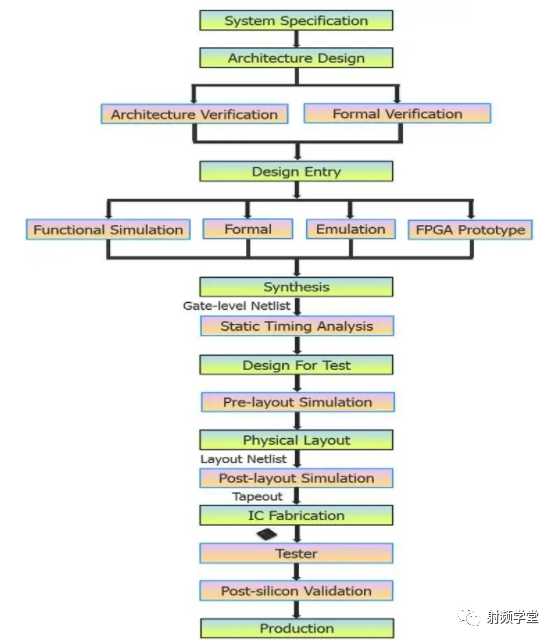

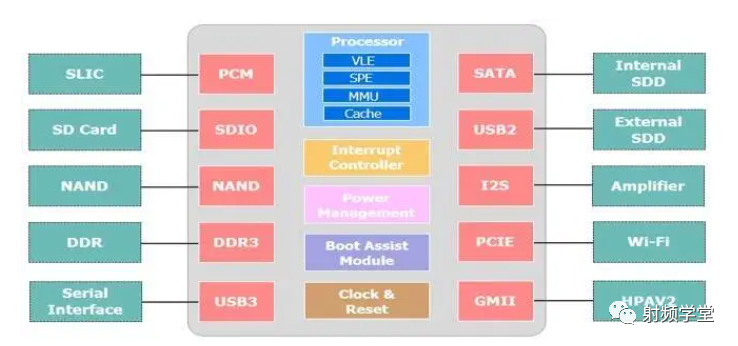

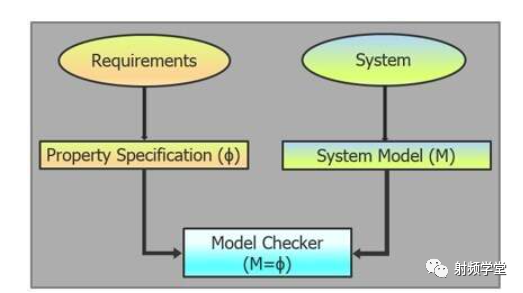

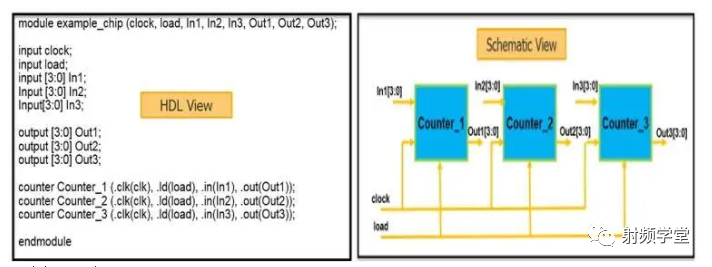

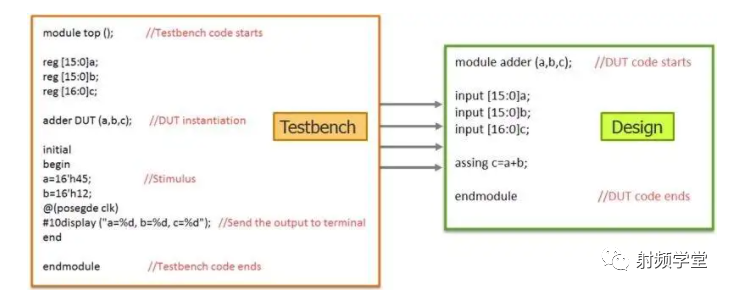

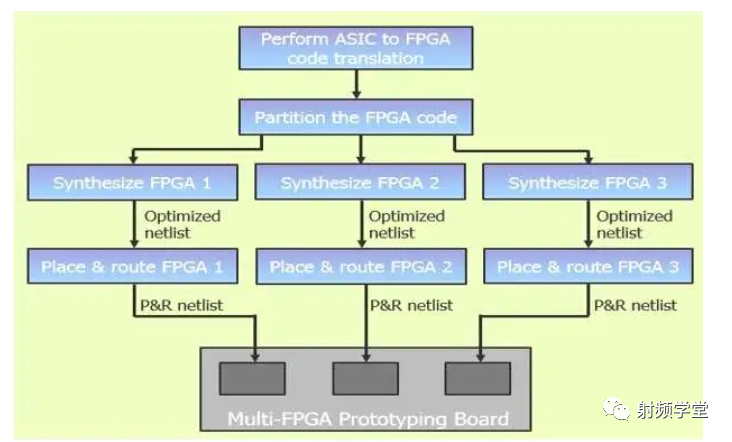

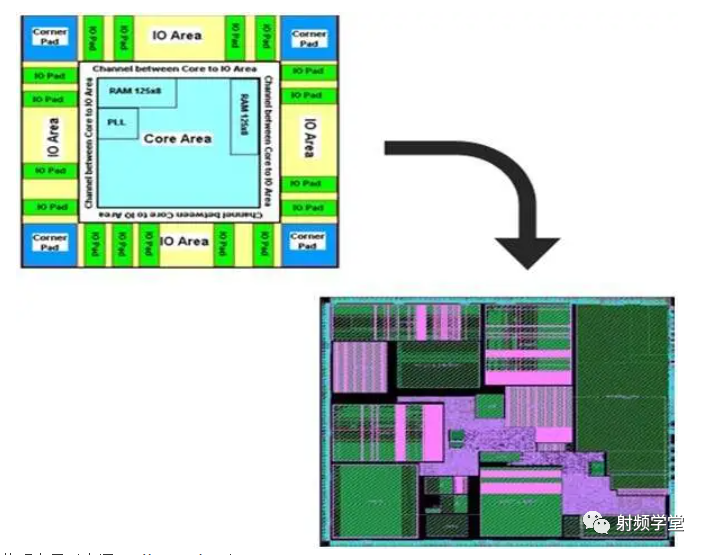

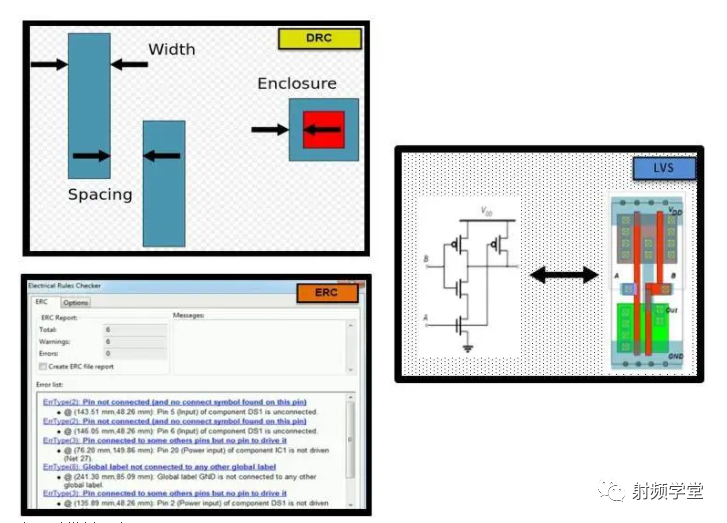

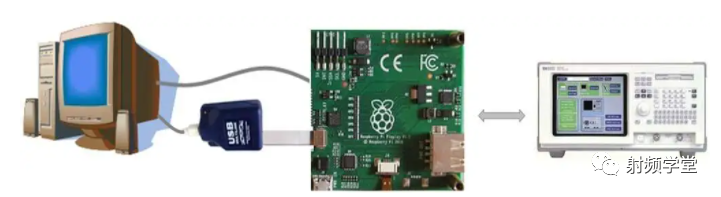

芯片是我们这个时代最最最伟大的发明之一,如果没有芯片的出现,我们很难想象如今的电子时代会是个什么样子?每个人操作着一台房子般大小的“电脑”,背着巨大的“手机”在和远方的朋友通话,而且声音极差。正是因为芯片的发明,才让所有的功能都集中在小小的指甲盖大小的芯片里面,我们普通老百姓也才能真正享受这个无线时代带来的便捷。但是,时至今日,芯片依然是卡脖子的一环。所以今天我们一起来学习一下关于芯片相关的知识。什么是芯片? 芯片,也就是集成电路,或者说是超大规模集成电路,是由数千,数百万,甚至数十亿个晶体管,电阻,电容组成的电子电路。它执行与使用分立(单独封装)组件构建的较大电路相同的功能,但 IC 是一种极其紧凑的设备,在一小块半导体材料上构建为单个单元。制造IC的主要原材料是硅;因此,IC 通常被称为“硅芯片”。也可以使用其他原材料,如锗和砷化镓,但由于以下原因,硅是主要选择: .硅是一种半导体,这意味着它可以在称为掺杂的过程中控制的某些条件下充当导体和绝缘体。掺杂是指添加杂质以改变元素的电气特性。 .硅在地球上很丰富,这使得它非常实惠。 芯片专为某种目的而设计,可用于各种行业,例如航空航天、汽车、电信、计算机等。一个或多个 IC 以及其他组件和连接器安装在印刷电路板 (PCB) 上,并与细铜带连接以满足应用需求。PCB 的一个非常常见的用途是作为计算机的主板。  芯片的分类 下图给出了常见芯片的分类,包括ASIC,ASSP,SoC,FPGA,SoC FPGA, ucontroller, uprocessor 等等。  ASIC是专用集成电路Application Specific Integrated Circuit的首字母缩写,是指为特定应用而设计的 IC 称为 ASIC,主要用于路由器、交换机、调制解调器等电子设备中。 ASIC的主要特点如下: · 在其整个生命周期内执行相同的功能 · 没有处理器 · 设计周期费时费钱 · 大批量生产 · 高速低功耗 · 可以是数字的、模拟的或两者兼而有之 ASSP是特定标准应用器件Application Specific Standard Part的首字母缩写,专为特定应用而设计,但不是为系统或客户定制的IC。ASSP 是一种特殊的 ASIC,可以被多家公司使用。ASSP 的特性类似于 ASIC。主要用在以太网控制器、PCIE控制器、USB接口等。 SoC(片上系统):集成了完整系统的IC称为SoC。它包含处理器、存储器和外围设备以及软件。SoC的处理器可以是微处理器(μP或MPU)、微控制器(μC或MCU)、数字信号处理器(DSP)或图形处理器。带有处理器的 ASIC 或 ASSP 是 SoC,因此 SoC 的特性类似于 ASIC 或 ASSP 的特性。主要用于语音、视频和图像信号处理、无线通信、汽车等。 FPGA(现场可编程门阵列):FPGA 是一种可编程 IC。它具有可配置的逻辑块、可配置的输入-输出块和可编程互连。主要应用在原型 ASICS 或 SoC、设备控制器、信号处理系统、图像处理系统等。FPGA的主要特点如下: ·适用于需要频繁定制的设计 .没有处理器 .设计周期不耗时且成本低廉 .适用于小体积设计 .更低的速度和低功耗 可编程SoC或SoC FPGA:集成了处理器和FPGA架构的IC称为可编程SoC或SoC FPGA。这还包括外设、片上存储器、FPGA 式逻辑阵列和高速收发器。主要用在网络、航空航天、国防等。可编程SoC/SoC FPGA的主要特点如下: .适用于需要频繁定制且具有处理能力的设计 .较小的尺寸 .处理器和 FPGA 之间的更高带宽通信 .设计周期不耗时且成本低廉 .风险低,因为它是可重新编程的 .更低的速度和低功耗 微处理器(μP 或 MPU):仅包含处理器的 IC 称为微处理器。它不包含内存(RAM、ROM 等)或任何其他外围设备。以下是微处理器的主要特性: .昂贵的 .更高的速度和更高的功耗 .适用于更大的设计 .执行复杂的任务 .应用:台式电脑、笔记本电脑、记事本、汽车、火车等。 微控制器(μC 或 MCU):包含处理器以及存储器(RAM、ROM 等)和其他外围设备的 IC 称为微控制器。这是一个通用设备,需要针对应用程序进行编程。微控制器可用于各种工业产品。微控制器是 SoC 的缩小版本。以下是微控制器的主要特性: .紧凑,因为所有外围设备都在 IC 中 .有处理器 .比微处理器便宜 .更低的速度和低功耗 .适用于较小的设计,因为它很紧凑 .执行不太复杂的任务 .应用:微波炉、洗衣机、DVD播放器、手机等。 芯片是怎么设计的? 下图反映了 IC 设计周期(以下部分对每个步骤进行了解释):  系统规格 IC 供应商会见潜在客户,以确定他们正在寻找的功能并准备一份功能要求列表。系统规范是指定系统(IC)的功能规范(或要求)并定义其外部接口的过程。  架构设计 一旦确定了系统规范,就开始了系统架构的设计过程。这包括创建或购买知识产权 (IP) 块,以及定义软件接口、时序、性能、面积和功率限制。标准工业 IP 模块可从 IP 供应商处获得。  架构验证 架构验证是构建硬件系统的软件版本的过程。这是使用高级语言(如 C、C++ 或 SystemC)从函数模型创建的。使用软件调试器评估整个系统的架构、性能和功率。  形式验证/属性检查 形式验证是使用数学方法静态验证设计正确性的过程,不使用任何激励或时序检查。 一种称为属性检查的形式验证方法用于证明实现的系统模型满足设计要求(或规范)。在属性检查中,使用属性规范语言(如 PSL 和 SVA)定义系统需求,并创建已实现系统的数学模型。使用模型检查器比较系统要求和数学模型,以确认系统满足要求。  设计输入 在系统的架构设计和验证之后,下一步就是设计输入。这是使用硬件设计语言 (HDL)(例如 VHDL 和 Verilog)和/或原理图捕获来捕获完整系统设计的过程。该设计包含 I2C 输入和输出引脚、IP 块实例、设计连接、时钟和复位策略等的详细信息。  功能仿真 功能仿真是使用软件仿真器验证设计的功能行为的过程。这不考虑设计元素的时序延迟。它验证IC级连通性、IC级环境中的IP块(一般IP块是预先验证过的)、端到端的功能路径、焊盘连通性、模块间交互、外部模块交互等。 测试平台是一组代码,用于检查 RTL 实现是否(或不)满足设计规范。它包含有效和预期条件以及无效和意外条件,以检查设计是否按预期运行。  形式验证 - 等效性检查 正如我们之前提到的,形式验证是使用数学方法静态验证设计正确性的过程,而不使用任何激励或时序检查。 一种称为等效性检查的形式验证方法用于通过将设计与黄金设计进行比较来找到设计的功能等效性。下图描述了 IC 设计周期各个阶段的等效性检查:  硅前验证 硅前验证是在将设计发送到制造之前在硬件中验证设计的过程。它可以验证高风险或新开发的 IP,并节省重新旋转 IC 的成本。可以使用仿真器或 FPGA 执行硅前验证。 好处: .与模拟环境相比非常快 .可以探测一组有限的内部信号以进行调试 .可以在流片之前验证软件和应用级场景 限制: .硬件很贵 .无法验证模拟 IP 块 .与真实芯片相比,系统时钟速度较慢 .需要多个硬件设置,尤其是在验证和软件团队分布在多个地理位置的情况下 仿真 仿真是在称为仿真器的硬件设备上验证系统功能的过程。仿真器可以比模拟更快地运行非常大的 IC 设计,并且可以以不同的时钟速度同时运行许多 IC 设计。下图显示了最先进的模拟器:  基于 FPGA 的原型设计 基于 FPGA 的原型设计是使用一个或多个 FPGA 验证系统功能的过程。FPGA 原型设计遵循以下步骤: 1.ASIC RTL(寄存器传输级)代码转换为 FPGA RTL 代码。它包括使用不同的存储器、移除模拟块、重写时钟方案等。 2.如果完整的 FPGA RTL 代码不适合单个 FPGA,则代码会被划分到多个 FPGA 中。 3.FPGA 工具用于综合和布局布线。 位文件被下载到 FPGA 中并验证设计。  合成 综合是在给定技术库和设计约束的情况下将设计的 RTL 代码转换为优化的门级表示的过程。在合成中进行以下步骤: 1.翻译:设计 RTL 代码被翻译成与技术无关的布尔方程。 2.优化:优化布尔方程,去除冗余逻辑。 3.技术映射:借助设计约束和技术库,将技术无关的布尔方程映射到技术相关的逻辑门。  静态时序分析 (STA) 静态时序分析 (STA) 是在不提供任何激励的情况下验证设计时序特性的过程。STA 快速且详尽,但它不会检查设计的功能。电子设备由时钟信号驱动;因此,必须验证设计是否在指定的时钟频率下工作。STA 在 IC 设计周期的各个阶段执行。 测试设计 (DFT) 制造 IC 的过程并非 100% 没有错误。因此,必须在设计中插入称为测试设计 (DFT) 逻辑的额外逻辑,以帮助 IC 的后期生产测试以识别制造缺陷。制造 IC 时,首先会在 DFT 逻辑的帮助下检查是否存在任何制造缺陷。如果没有制造缺陷,则检查 IC 的功能正确性。 预布局模拟 在发送门级网表进行物理布局之前,软件应用程序会对其功能和时序行为进行验证。这称为布局前模拟。 物理布局 物理布局是从 IC 的逻辑视图到物理视图的过渡。物理布局过程的输出是图形数据库系统 (GDSII) 文件,该文件是一种二进制文件格式,表示平面几何形状、文本标签和其他与物理布局相关的信息。物理布局中执行的步骤如下: .布局规划:确定主要设计块,并分配空间以满足时序、面积和性能标准。IP 结构、纵横比和路由可能性也在这里决定。 .分区:将 IC 分成功能块,使布局和布线更容易。 .布局布线:放置和连接设计块,以便不违反设计规则。 .时钟树综合:时钟均匀分布到设计中的所有时序元素。  布局后模拟 布局后仿真是在设计的物理布局建立后验证设计的过程。在布局后模拟中执行的检查如下: .设计规则检查 (DRC):布局满足制造所需的一组规则 .电气规则检查 (ERC):布局满足一组电气设计规则 .版图与原理图 (LVS):版图在功能上与设计的网表相同  集成电路制造 在布局后仿真之后,GDSII 文件形式的布局网表被提供给 IC 制造商(代工厂)。向代工厂提供 GDSII 文件的过程称为带出。IC制造过程如下图所示:  IC测试仪 IC 制造并非 100% 可靠,导致许多样品存在制造缺陷。一旦从代工厂收到 IC,就会使用测试仪来过滤有缺陷的 IC。测试仪向 IC 提供输入激励并验证输出。它还验证 IC 的电气和热特性并找到理想的工作条件 。  硅后验证 通过测试仪的样品在真实环境中进行验证。这称为硅后验证。在硅后验证中,使用计算机上的软件工具配置 IC,并将测试代码下载到 IC 中。预期的输出受到监控,IC 的所有功能都得到验证。下图描述了验证后设置:  概括 IC种类繁多,每种IC都有一定的特点:可编程或不可编程,有无处理器,高速或低速,紧凑或笨重。设计、制造和测试 IC 的过程是复杂而详尽的。主要贡献者是设计和验证团队、IP 供应商和 IC 制造商。高级 EDA 工具在减少与 IC 设计周期相关的时间和精力方面发挥着至关重要的作用。 |