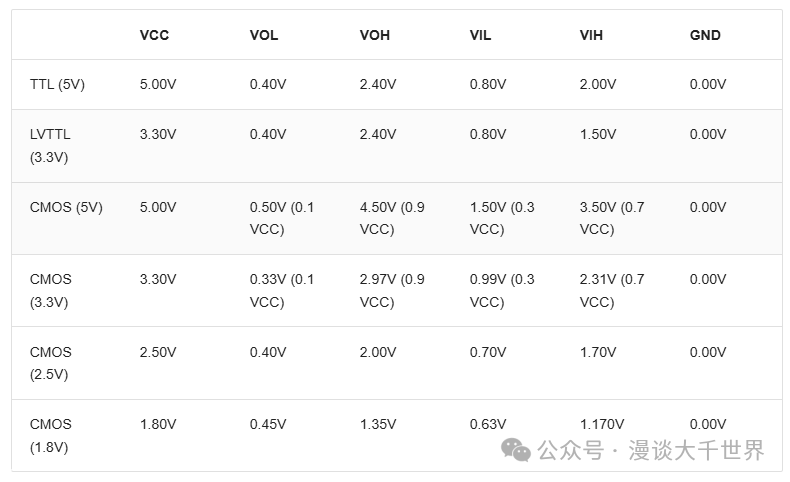

逻辑电平是数字电路中用来表示二进制逻辑状态(“1”和“0”)的电压或电流水平。它是数字电路设计和通信的基础,不同的逻辑电平标准对应着不同的电压范围和特性。1. 逻辑电平的应用· 数字电路设计 :在设计数字电路时,需要根据所使用的逻辑器件选择合适的逻辑电平标准。例如,在设计一个基于FPGA的数字系统时,通常会选择LVCMOS电平,因为FPGA内部大多采用CMOS工艺,LVCMOS电平与FPGA的输入输出接口兼容性好。 · 接口通信 :在不同设备之间进行通信时,逻辑电平的匹配至关重要。例如,当一个3.3V的微控制器与一个5V的传感器通信时,需要进行电平转换,以确保信号的正确传输。可以使用专门的电平转换器芯片,如TXB0104等,来实现不同电平之间的转换。  · 信号完整性 :在高速数字电路中,逻辑电平的稳定性和完整性对系统的性能影响很大。需要考虑信号线的布线、电源的稳定性、去耦电容的配置等因素,以减少信号的反射、串扰和噪声干扰,保证逻辑电平的准确性和可靠性。

|