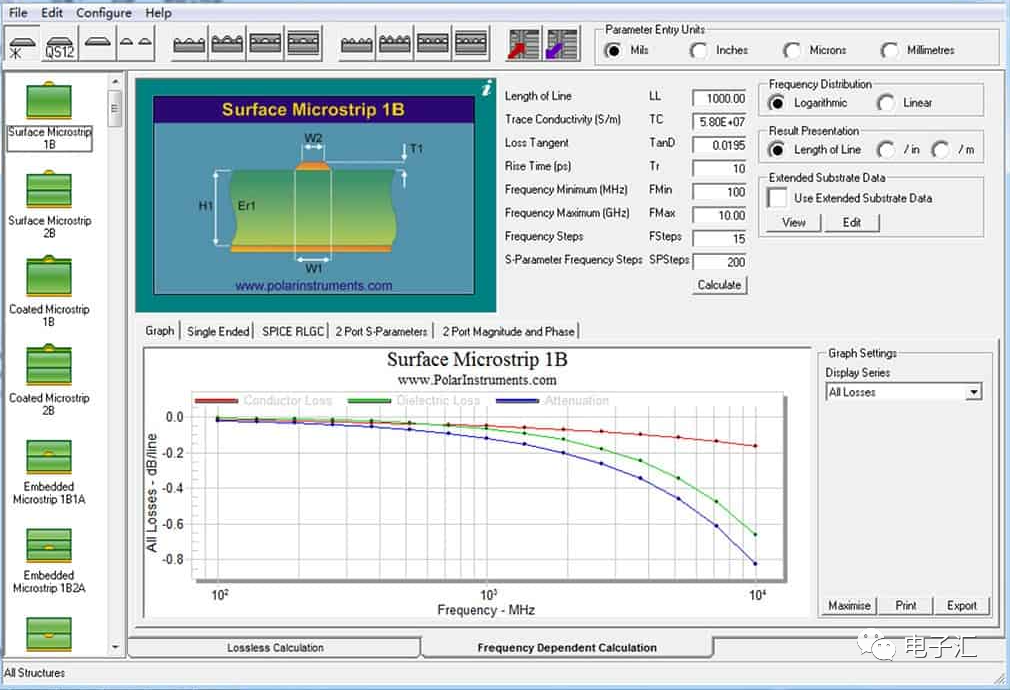

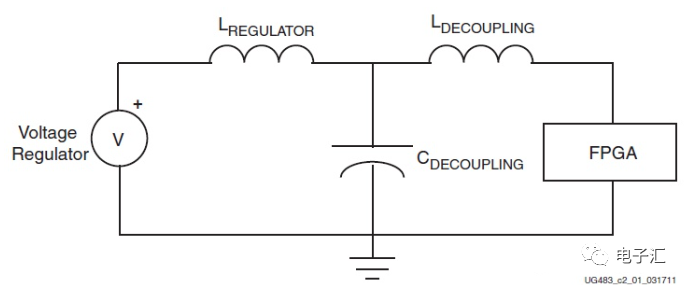

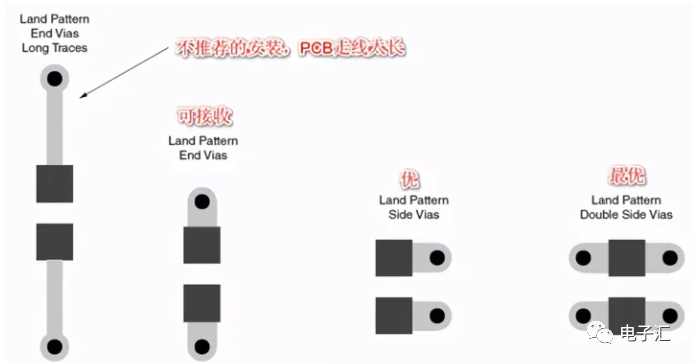

一、FPGA的高速电路板设计PCB板的设计规模增大,IO传输问题也就出现。为了兼容其他高速模块,必须对PCB的设计进行优化。  1️⃣电源滤波,降低系统噪声2️⃣匹配信号线3️⃣降低并行走线的噪扰4️⃣减小反弹效应5️⃣进行阻抗匹配 为了实现上述要求,可以采用的方法有: (1)选择合适的材料 一般选用介电常数越小的材料,传输阻抗越小,传输损耗越小。Altera中给出了FR-4的高速报告,说明FR-4可以跑高速设计。但是,一般还是需要了解厂家的材料的信息,用于整个设计的阻抗计算。 (2)PCB上传输走线 有微带传输线布局(单一参考面)和带状传输线布局(双参考平面)两种,可以支持基本的设计。 (3)阻抗计算 在PCB板设计之初就做好阻抗的控制,保证后期有足够的时序余量。  (4)降低串扰和维持信号完整性的布线方法 1️⃣在允许范围内,提高线距 2️⃣临近地线,可以去耦合 3️⃣差分布线,可以提高信号完整性 4️⃣存在明显耦合,可以在不同层之间布设相互垂直的单端信号(这个目前不清楚咋做) 5️⃣减小并线长度,减少长耦合走线 二、FPGA的电源供电(1)供电要求  1️⃣单调性:带电源爬升过程中单调非负斜率(下降则为非正),能够减小噪声。 2️⃣软启动:FPGA启动时需要特定的电流,不能爬升的太快,每一级的电源达到预定状态需要时间。 3️⃣最大最小爬升时间:最大爬升时间是保证不会久留于阈值电压附近,尽快达到逻辑电平。最小爬升时间保证不会出现浪涌电流状况。 4️⃣敏感模拟元件:需要稳定的电压,不能有太大的电压波动存在。FPGA上的PLL就需要单独的线性电压源供电。 (2)Altera的供电策略 1️⃣电源层尽量靠近FPGA,可以减少BGA过孔电感 2️⃣将Transceiver作为布局最高优先级(高速收发器含有内部调制器、电流足够低、必须分配收发器关键轨道最高优先级这三种情况除外) 3️⃣大电流电源轨道考虑:无高速收发器则大电流最高级,有则置于次优先级(核心电压则可以放于最远处) 4️⃣PLL电源及其他电源:PLL作为第三级考虑,其他电源按需分配。 三、退耦电容(1)退耦电容的作用 利用电容的谐振频率的极小范围实现滤波,将噪声去除。  (2)计算电容值 实际电容的计算比较复杂,可以使用软件自动计算。 (3)电容的摆放 退耦电容最好的摆放就是尽可能的靠近电源或者地,保证最小的阻值和最小的感抗。 |