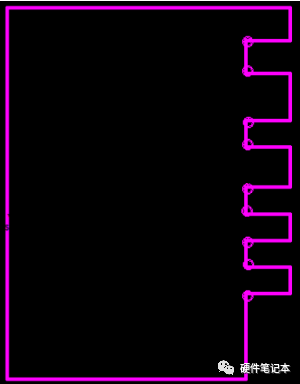

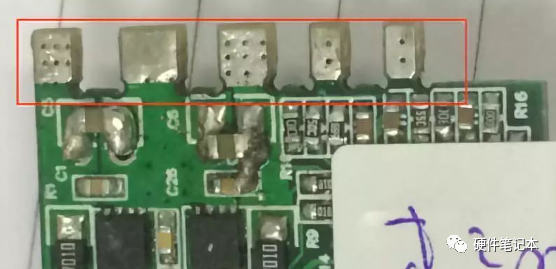

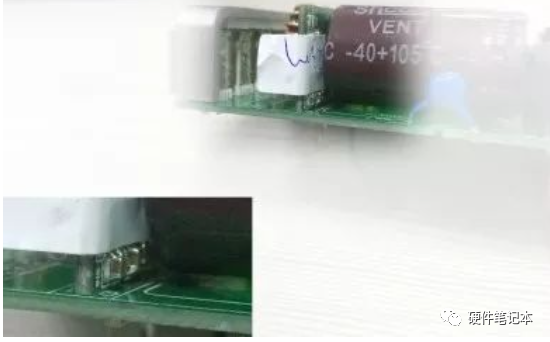

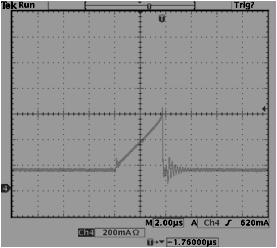

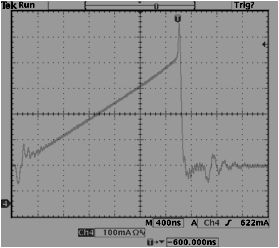

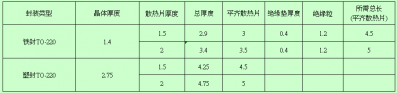

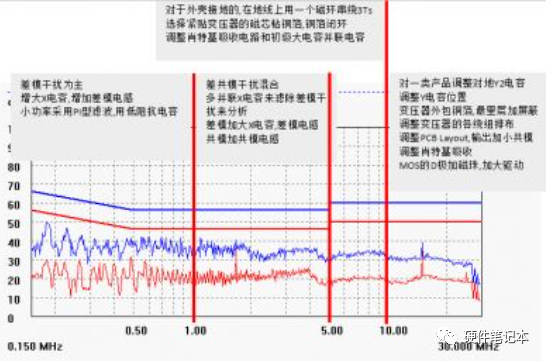

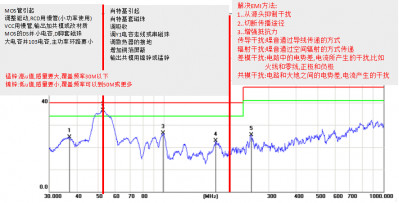

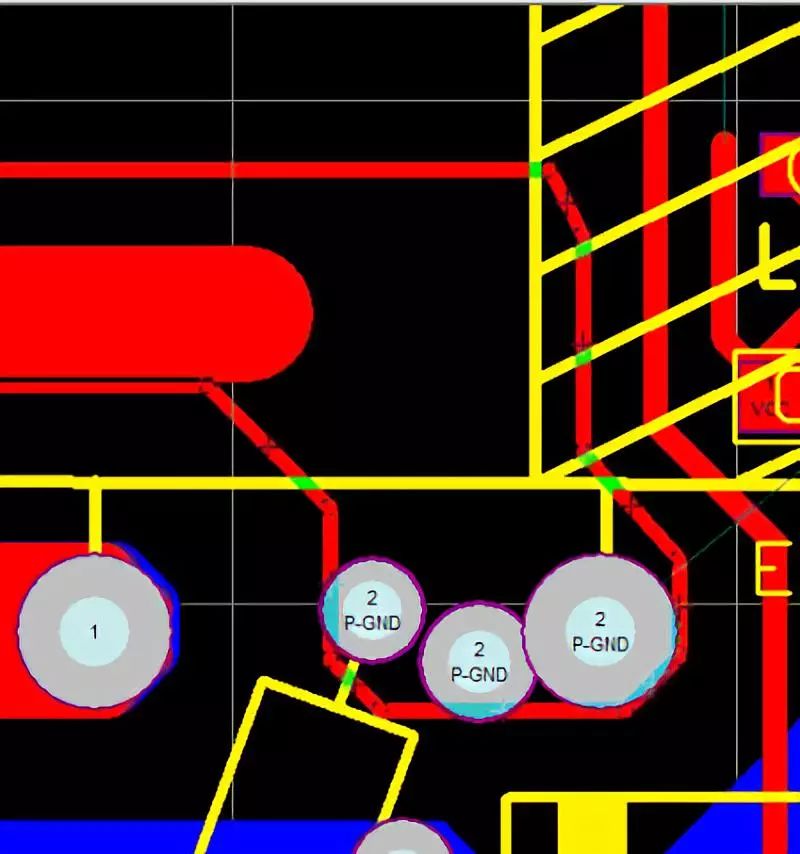

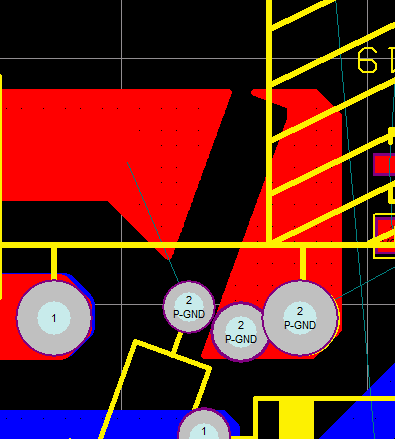

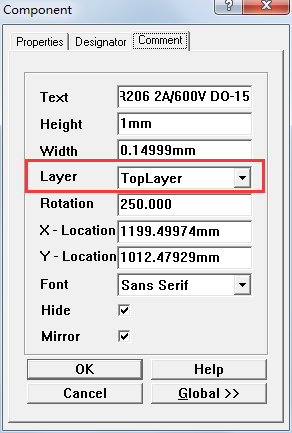

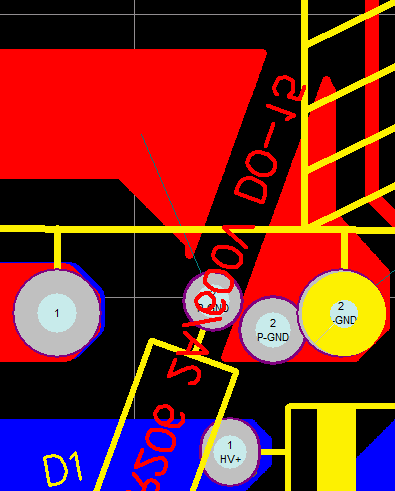

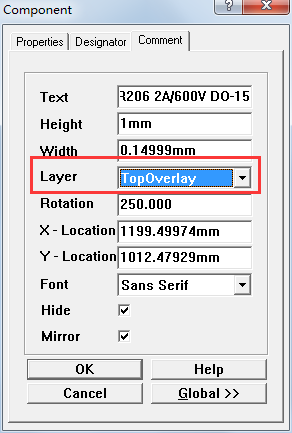

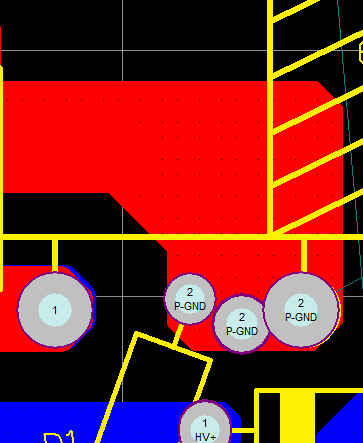

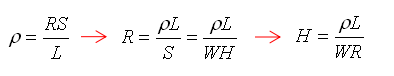

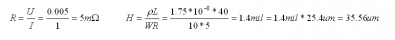

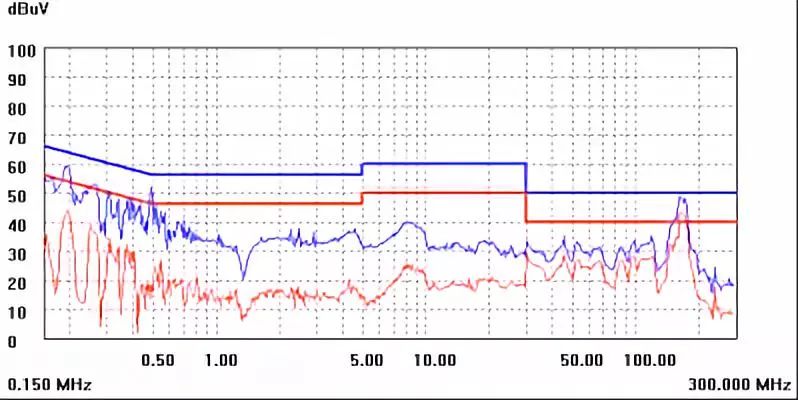

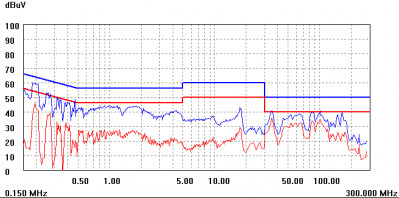

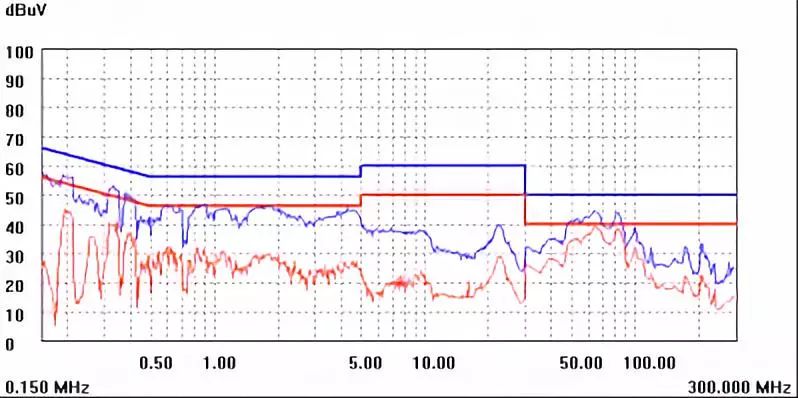

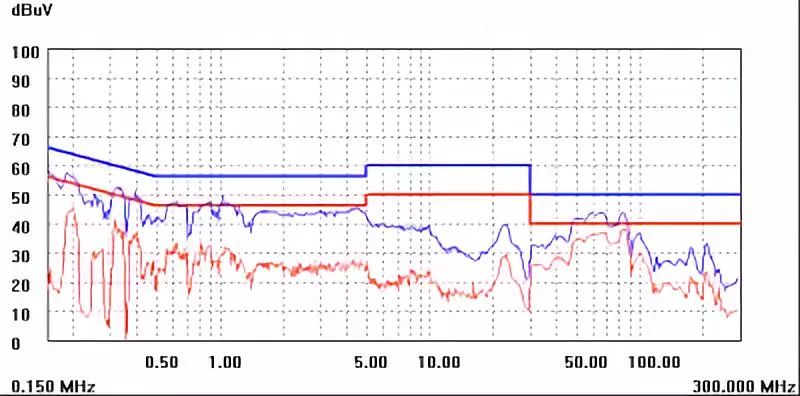

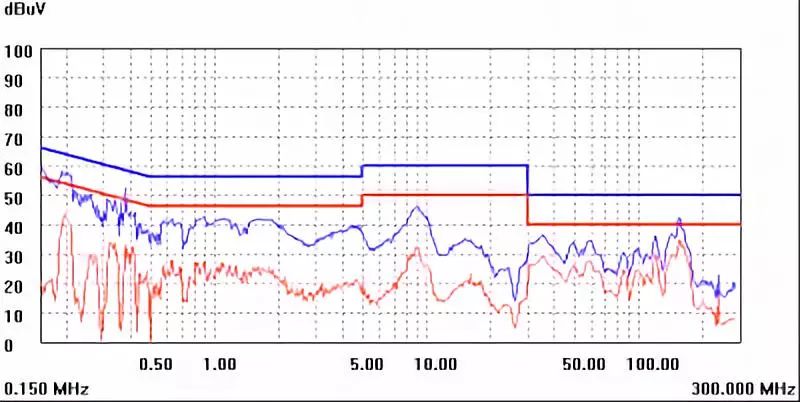

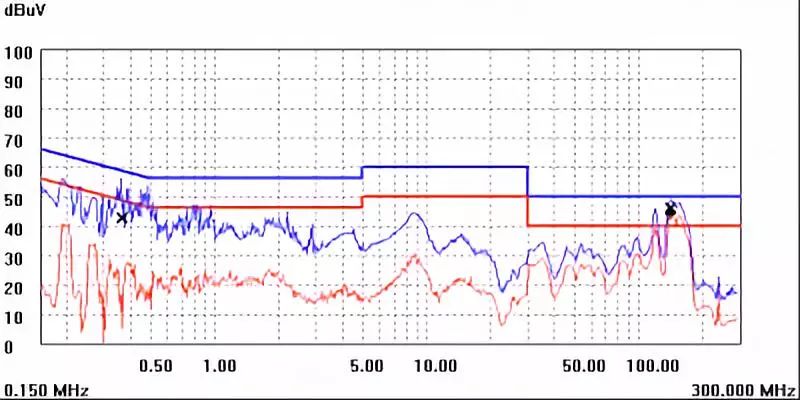

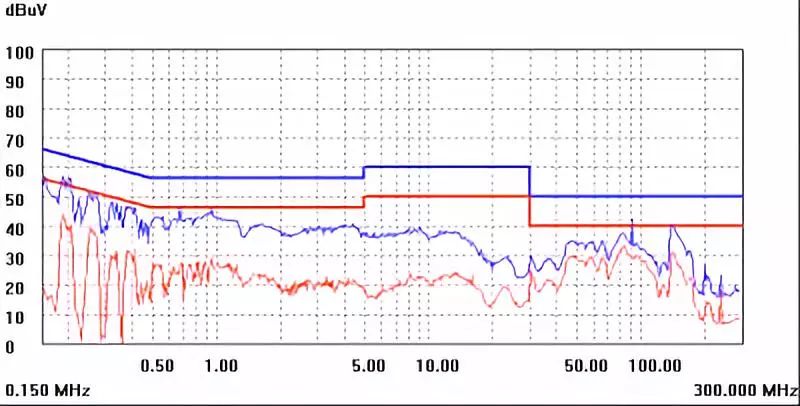

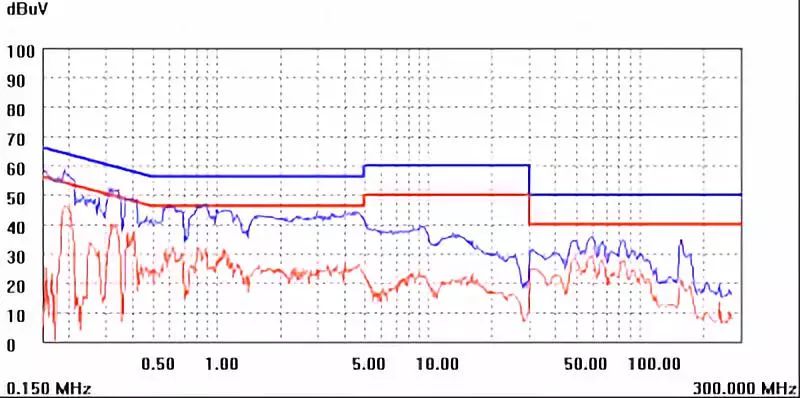

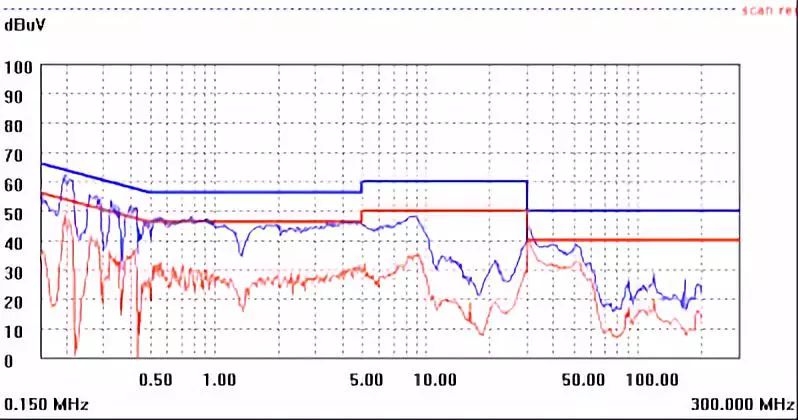

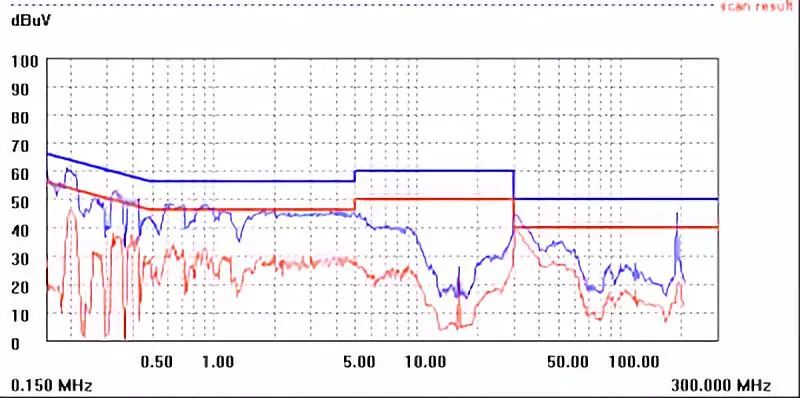

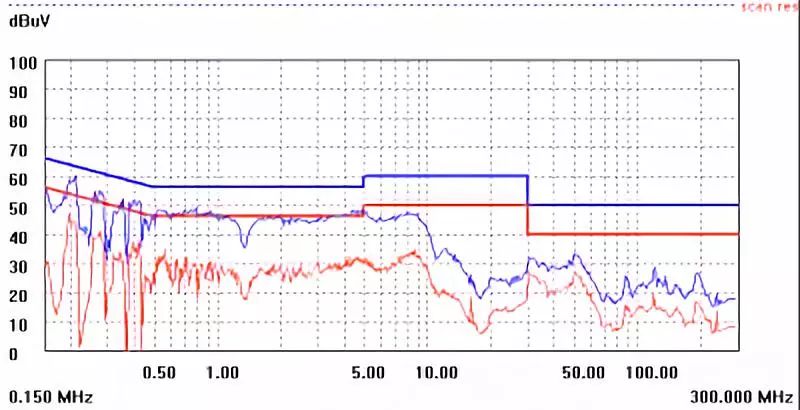

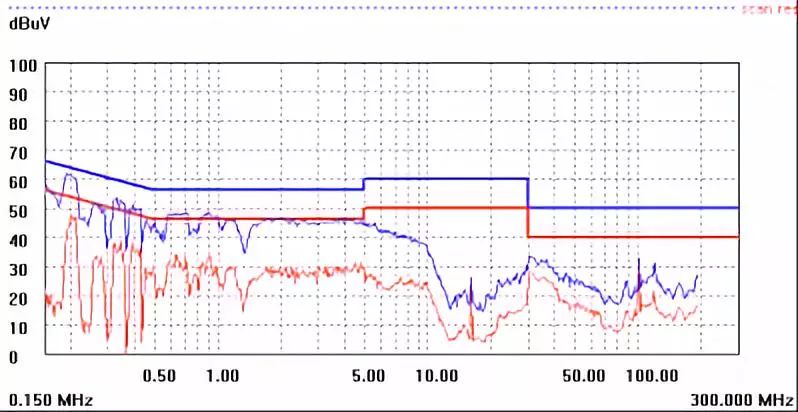

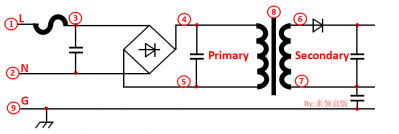

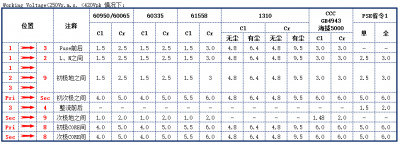

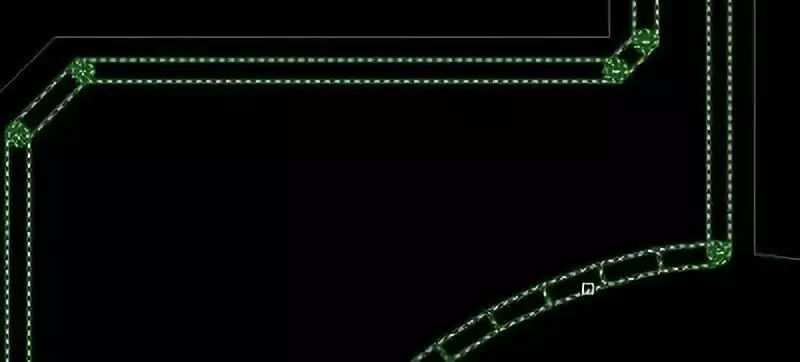

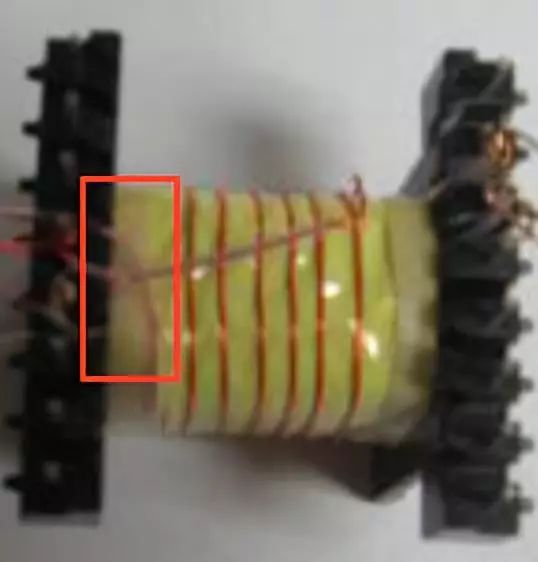

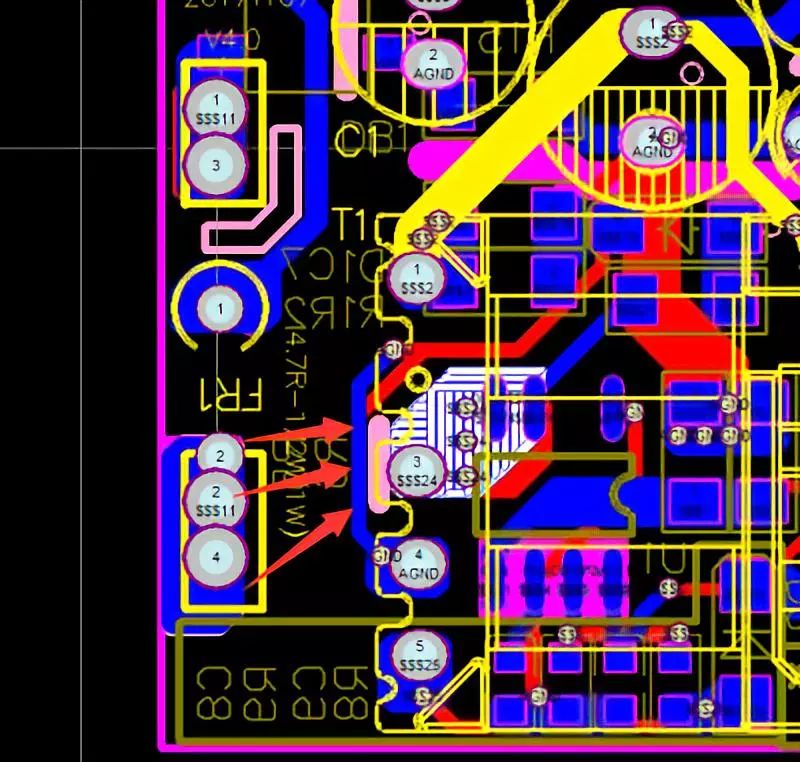

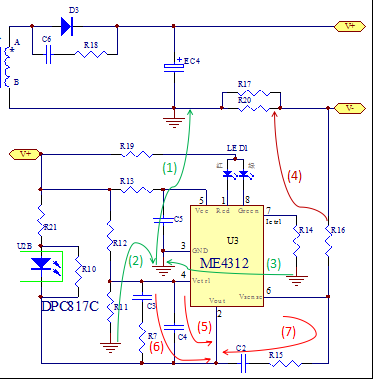

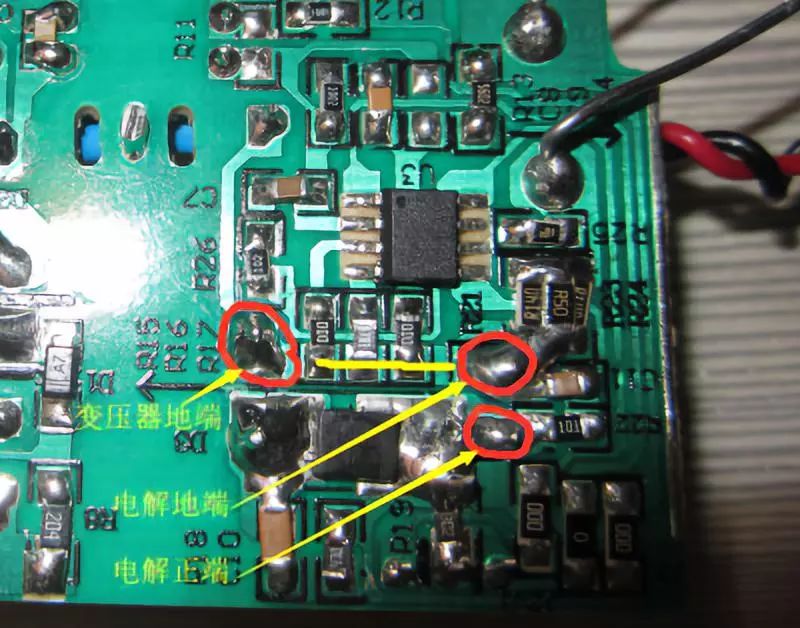

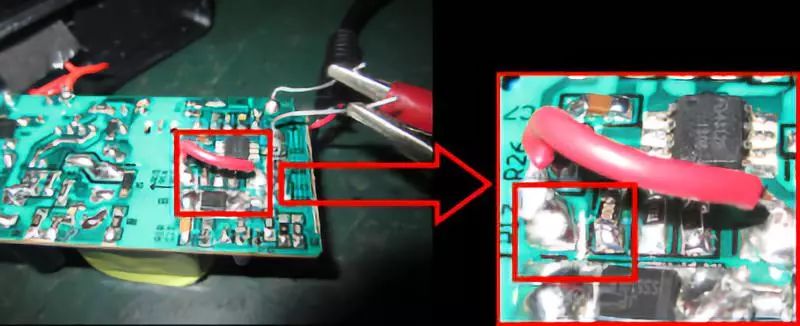

1. 变压器图纸、PCB、原理图这三者的变压器飞线位号需一致。理由:安规认证要求 这是很多工程师在申请安规认证提交资料时会犯的一个毛病。 2.X电容的泄放电阻需放两组。 理由:UL62368、CCC认证要求断开一组电阻再测试X电容的残留电压。 很多新手会犯的一个错误,修正的办法只能重新改PCB Layout,浪费自己和采购打样的时间。 3.变压器飞线的PCB孔径需考虑到最大飞线直径,必要是预留两组一大一小的PCB孔。 理由:避免组装困难或过炉空焊问题 因为安规申请认证通常会有一个系列,比如说24W申请一个系列,其中包含4.2V-36V电压段,输出低压4.2V大电流和高压36V小电流的飞线线径是不一样的。 多根飞线直径计算参考如下表格:  4.输出的DC线材的PCB孔径需考虑到最大线材直径。 理由:避免组装困难 因为你的PCB可能会用在不同电流段上,比如5V/8A,和20V/2A,两者使用的线材是不一样的 参考如下表格:  5.电路调试,OCP限流电阻多个并联的阻值要设计成一样。 理由:阻值越大的那颗电阻承受的功率越大 6.电路设计,散热片引脚的孔做成长方形椭圆形(经验值:2*1mm)。 理由:避免组装困难 椭圆形的孔方便散热器有个移动的空间,这对组装和过炉是非常有利的。 7.电路调试,异常测试时,输出电压或OVP设计要小于60Vac(Vpk)/42.4Vdc(Vrms)。 理由:安规要求 这个新手比较容易忽略,所以申请认证的产品一定要做OVP测试,抓输出瞬间波形。 8.电路设计,电解电容的防爆孔距离大于2mm,卧式弯脚留1.5mm。 理由:品质提升 一般正规公司都有这个要求,防爆孔的问题日本比较重视,特殊情况除外。 9.电路调试,输出有LC滤波的电路需要老化确认纹波,如果纹波异常请调整环路。 理由:验证产品稳定性 这个很重要,我之前经常碰到这个问题,产线老化后测试纹波会变高,现象是环路震荡。 10.电路调试,二极管并联时,应该测试一颗二极管故障开路时, 产生的异常(包括TO-220 里的两颗二极管)。 理由:品质提升 小公司一般都不会做这个动作的,一款优秀的产品是要经得起任何考验的。 11.电路设计,如果PCB空间充裕,请设计成通杀所有安规标准。 理由:减少PCB修改次数。 如果你某一产品是符合UL60335标准,哪天客户希望满足UL1310,这时你又得改PCB Layout拿去安规报备了,如果你画的板符合各类标准,后面的工作会轻松很多。 12.电路设计,关于ESD请设计成接触±8KV/空气±15KV标准。 理由:减少后续整改次数。 像飞利浦这样的客户都要求ESD非常严的,听说富士康的还需要达到±20KV,哪天有这种客户要求,你又得忙一段时间了。 13.电路设计,设计变压器时,VCC电压在轻载电压要大于IC的欠压关断电压值。 判断空载VCC电压需大于芯片关断电压的5V左右,同时确认满载时不能大于芯片过压保护值 14.电路设计,设计共用变压器需考虑到使用最大输出电压时的VCC电压,低温时VCC有稍微NOSIE会碰触OVP动作。 如果你的产品9V-15V是共用一个变压器,请确认VCC电压,和功率管耐压 15.电路调试,Rcs与Ccs值不能过大,否则会造成VDS超过最大耐压炸机。 LEB前沿消隐时间设短了,比尖峰脉冲的时间还短,那就没有效果了还是会误判;如果设长了,真正的过流来了起不到保护的作用。 Rcs与Ccs的RC值不可超过1NS的Delay,否则输出短路时,Vds会比满载时还高,超过MOSFET最大耐压就可能造成炸机。 经验值1nS的Delay约等于1K对100PF,也等于100R对102PF 16.画小板时,在小板引脚的90度拐角处增加一个圆形钻孔。 理由:方便组装 如图:  实物如图:  实际组装如图:  这样做可以使小板与PCB大板之间紧密贴合,不会有浮高现象 17.电路设计,肖特基的散热片可以接到输出正极线路,这样铁封的肖特基就不用绝缘垫和绝缘粒 18.电路调试,15W以上功率的RCD吸收不要用1N4007,因为1N4007速度慢300uS,压降也大1.3V,老化过程中温度很高,容易失效造成炸机 19.电路调试,输出滤波电容的耐压致少需符合1.2倍余量,避勉量产有损坏现象。 之前是犯了这个很低级的错误,14.5V输出用16V耐压电容,量产有1%的电容失效不良。 20.电路设计,大电容或其它电容做成卧式时,底部如有跳线需放在负极电位,这样跳线可以不用穿套管。 这个可以节省成本。 21.整流桥堆、二极管或肖特基,晶元大小元件承认书或在BOM表要有描述,如67mil。 理由:管控供应商送货一至性,避免供应商偷工减料,影响产品效率 另人烦脑的就是供应商做手脚,导致一整批试产的产品过不了六级能效,原因就是肖特基内部晶元用小导致。 22.电路设计,Snubber 电容,因为有异音问题,优先使用Mylar电容 。 处理异音的方法之一 23.浸漆的TDK RF电感与未浸漆的鼓状差模电感,浸漆磁芯产生的噪音要小12dB 处理异音的方法之二 24.变压器生产时真空浸漆,可以使其工作在较低的磁通密度,使用环氧树脂黑胶填充三个中柱上的缝隙 处理异音的方法之三 25.电路设计,启动电阻如果使用在整流前时,要加串一颗几百K的电阻。 理由:电阻短路时,不会造成IC和MOSFET损坏。 26.电路设计,高压大电容并一颗103P瓷片电容位置。 理由:对幅射30-60MHz都有一定的作用。 空间允许的话PCB Layout留一个位置吧,方便EMI整改 27.在进行EMS项目测试时,需测试出产品的最大程序,直到产品损坏为止。 例如ESD 雷击等,一定要打到产品损坏为止,并做好相关记录,看产品余量有多少,做到心中有数 28.电路设计,异常测试时,短路开路某个元件如果还有输出电压则要进行LPS测试,过流点不能超过8A。 超过8A是不能申请LPS的 29.安规开壳样机,所有可选插件元件要装上供拍照用,L、N线和DC线与PCB要点白胶固定。 这个是经常犯的一个毛病,经常一股劲的把样品送到第三方机构,后面来来回回改来改去的 30.电路调试,冷机时PSR需1.15倍电流能开机,SSR需1.3倍电流能开机,避免老化后启动不良 PSR现在很多芯片都可以实现“零恢复”OCP电流,比如ME8327N,具有“零恢复”OCP电流功能 31.电路设计,请注意使用的Y电容总容量,不能超过222P, 因为有漏电流的影响 针对不同安规,漏电流要求也不一样,在设计时需特别留意 32.反激拓补结构,变压器B值需小于3500高斯,如果变压器饱和一切动作将会失控,如下,上图为正常,下图为饱和。   变压器的磁饱和一定要确认,重重之重,这是首条安全性能保障,包括过流点的磁饱和、开机瞬间的磁饱和、输出短路的磁饱和、高温下的磁饱和、高低压的磁饱和。 33.结构设计,散热片使用螺丝固定参考以下表格设计,实际应用中应增加0.5-1mm余量,参考如下表格:  BOM表上写的螺丝规格一定要对,不然量产时会让你难受 34.结构设计,AC PIN焊线材的需使用勾焊,如果不是则要点白胶固定。 理由:安规要求 经常被第三方机构退回样品,整改 35.传导整改,分段处理经验,如下图,这只是处理的一种方法,有些情况并不是能直接套用  36.辐射整改,分段处理经验,如下图,适合一些新手工程师,提供一个参考的方向,有些情况并不是能直接套用,最主要的还是要搞清楚EMI产生的机理。  37.关于PCB碰到的问题,如图,为什么99SE画板覆铜填充的时候填不满这个位置?像是有死铜一样   D1这个元件有个文字描述的属性放在了顶层铜箔,如图   把它放到顶层丝印后,完美解决。   38.变压器铜箔屏蔽主要针对传导,线屏蔽主要针对辐射,当传导非常好的时候,有可能你的辐射会差,这个时候把变压器的铜箔屏蔽改成线屏蔽,尽量压低30M下降的位置,这样整改辐射会快很多。 EMI整改技巧之一 39.测试辐射的时候,多带点不同品牌的MOS、肖特基。有的时候只差2、3dB的时候换一个不同品牌会有惊喜。 EMI整改技巧之二 40.VCC上的整流二极管,这个对辐射影响也是很大的。 一个惨痛案例,一款过了EMI的产品,余量都有4dB以上,量产很多次了,其中有一次量产抽检EMI发现辐射超1dB左右,不良率有50%,经过层层排查、一个个元件对换。最终发现是VCC上的整流二极管引发的问题,更换之前的管子(留低样品),余量有4dB。对不良管子分析,发现管子内部供应商做了镜像处理。 41.一个冷知识,如何测量PCB的铜箔厚度? 方法:在PCB板上找一条光滑且长的线条,测量其长度L,再测宽度W,再用DC源加1A电流在其两端测得压降U 依据电阻率公式得出以下公式:  例:取一段PCB铜箔,长度L为40mm,宽度为10mm,其通过1A电流两端压降为0.005V,求该段铜箔厚度为多少um?  42.一款36W适配器的EMI整改案例,输出12V/3A,多图对比,整改花费时间3周。 变压器绕法一:Np1→VCC→Ns1→Ns2→铜屏蔽0.9Ts→Np2 PCB关键布局:Y电容地→大电容地,变压器地→Vcc电容→大电容地 注:变压器所有出线没有交叉  图一(115Vac) 图一所示可以看到,130-200M处情况并不乐观; 130-200M主要原因在于PCB布局问题和二次侧的肖特基回路,改其它地方作用不大,肖特基套磁珠可以完全压下来,图忘记保存了。 为了节约成本,公司并不让我这样做,因为套磁珠影响了成本,当即NG掉此PCB布局,采用图一a方式PCB关键布局走线。 变压器绕法不变:Np1→VCC→Ns1→Ns2→铜屏蔽0.9Ts→Np2 PCB关键布局:Y电容地→变压器地→大电容地 注:变压器内部的初级出线及次级出线有交叉  图一a (115Vac) 图一a可以看出,改变PCB布局后130M-200M已经完全被衰减,但是30-130M没有图一效果好,可能变压器出线无交叉好一些。仔细观察,此IC具有抖频功能,传导部分频段削掉了一些尖峰;  图一b(230Vac) 图一b可以看到,输入电压在230Vac测试时,65M和83M位置有点顶线(红色线)  图一b-1(230Vac) 原边吸收电容由471P加大到102P,65M位置压下来一点,后面还是有点高,如图一b-1所示;  图一b-2(230Vac) 变压器屏蔽改成线屏蔽(0.2*1*30Ts),后面完全衰减,如图一b-2;  图一b-3(115Vac) 115Vac输入测试,后面150M又超了,发克!高压好了低压又不行,恼火啊!看来这招不行;  图一b-4(115Vac) 变压器屏蔽还是换成铜箔屏蔽(圈数由0.9Ts改成1.3Ts),效果不错,如图一b-4所示。  图一b-5(230Vac) 115Vac输入测试,测试通过。 结论: 一:变压器出线需做到不交叉; 二:Y电容回路走线越短越好先经过变压器地再回到大电容地,不与其它信号线交叉; 43.一款48W(36V/1.33A)整改EMI案例,仅仅是调整了肖特基吸收就把30-40M压下来。  115Vac低压30M红色顶线  230Vac高压30M红色也顶线 调整肖特基吸收后:  115Vac低压,走势图非常漂亮  230Vac高压,走势图非常漂亮 44.安规距离一览表。   45.刚入门使用CAD、PADS上容易遇到的问题。 a..PADS画好的PCB导出为DXF文件,CAD打开后是由双线组成的空心线段,如图:  刚开始不会时,是用L命令一根一根的描,狂汗 。。 使用多次后,解决方法是使用X命令就可以变成单根线 b..CAD图档线框转PADS做PCB外框图方法: step1.在CAD里面刪掉沒有的线,只剩下板框,其它线也可以不删。 step2.在键盘上敲PE,回车,鼠标点中其中一边,再敲Y,回车,再敲J,回车,拖动鼠标把整个板框选中,回车,按Esc键退出此模式。 step3.比例调整,SC 按空格,选取整个板框,按空格,任意地方单击鼠标一下, 比例: 39.37 ,按空格。 46.在画PCB定义变压器脚位时,要考虑到变压器的进线和出线是否会交叉,因为各绕组之间的绕线在边界处存在有45-90度的交叉,需在交叉出线处加一个套管到pin脚。  47.PCB的热点区域一定要远离输入、输出端子,防止噪声源串到线上导致EMI变差,在不得已而为之时,可增加地线或其它屏蔽方式进行隔离,如下图增加了一条地线进行有效隔离。  需注意这条地线的安全距离。 48.驱动电阻尽量靠近MOS、电流采样的电阻尽量靠近芯片,避免产生其它看不到的后果。 PCB布局铁律 49.分享一个辐射整改案例,一个长条形散热片有2个脚,2只脚都接地,辐射硬是整不过,后来把其中一只脚悬空,辐射频段变好。后面分析原因是2只脚接地会产生磁场回路。 这个整改花了很多钱 50.配有风扇的电源,PCB布局要考虑风路。 一定要让风跑出去 51.棒型电感两条腿之间,切记,切记,切记,禁止走弱信号走线,否则发生的意外你都找不到原因。 切记,以前在这上面吃了大亏 52.变压器磁芯形状选用小结 a..EE,EI,EF,EEL类,常用来制作中小功率的变压器,成本低,工艺简单 b..EFD,EPC类,常用来制作对高度有限制的产品,适合做中小功率类 c..EER,ERL,ETD类,常用来制作大中型功率的变压器,特别适合用来制作多路输出的大功率主变压器,且变压器漏感较小,比较容易符合安规 d..PQ,EQ,LP类,该磁芯的中间柱较一般的磁芯要大,产品漏感较小,适合做小体积大功率的变压器,输出组数不能过多 e..RM,POT类,常用来制作通讯类或中小功率高频变压器,本身的磁屏蔽很好,容易满足EMC特性 f..EDR类,一般常用于LED驱动,产品厚度要求薄,变压器制做工艺复杂 53.某些元器件或导线之间可能有较高电位差,应加大它们之间的距离,以免放电引出意外短路。 如反激一次侧的高压MOS的D、S之间距离,依据公式500V对应0.85mm,DS电压在700V以下是0.9mm,考虑到污染和潮湿,一般取1.2mm 54.如果TO220封装的MOS的D脚串了磁珠,需要考虑T脚增加安全距离。 之前碰到过炸机现象,增加安全距离后解决了,因为磁珠容易沾上残留物 55.发一个验证VCC的土方法,把产品放低温环境(冰箱)几分钟,测试VCC波形电压有没有触发到芯片欠压保护点。 小公司设备没那么全,有兴趣的可以做个对比,看看VCC差异有多大 关于VCC圈数的设计需要考虑很多因素 56.在变压器底部PCB加通风孔,有利于散热,小板也一样,要考虑风路。 在安规认证,变压器温度超了2度左右时,可以用这个方法 57.跳线旁边有高压元件时,应要保持安全距离,特别是容易活动或歪斜的元件。 保证产品量产时的稳定性 58.输出大电解底部不得已要走跳线时,跳线应是低压或是地线,为防止过波峰焊烫伤电容,一般加套管。 设计的时候尽量避免电容底部走跳线,因为增加成本和隐患 59.高频开关管平贴PCB时,PCB另一面不要放芯片等敏感器件。 理由:开关管工作时容易干扰到背部的芯片,造成系统不稳定,其它高频器件同理 60.输出的DC线在PCB设计时,要设计成长短一至,焊盘孔间隔要小。 理由:SR的尾部留长是一样长的,当两个焊盘孔间隔太远时,会造成不方便生产焊接 61.MOS管、变压器远离AC端,改善EMI传导。 理由:高频信号会通过AC端耦合出去,从而噪声源被EMI设备检测到引起EMI问题 62.驱动电阻应靠近MOS管。 理由:增加抗干扰能力,提升系统稳定性 63.一个恒压恒流带转灯的PCB设计走线方法和一个失败案例。 PCB设计走线方法请看图:  (a) 地线的Layout原则 如(1)(2)(3)绿线所示,R11的地和R14的地连接到芯片的地,再连接到EC4电解电容的地。注意不可连到变压器的地,因为变压器次级A->D3->EC4->次级B形成功率环,如果ME4312芯片的地接到次级B线到EC4电容之间,受到较强的di/dt干扰会导致系统的不稳定等因素。 失败案例:  造成的问题:转灯时红灯绿灯一起亮,并且红灯绿交替闪烁。 整改措施: 通过断开PCB铜箔使用一根导线连到输出电容地,隔开ME4312B芯片地,如下图:  通过以上处理,灯闪问题已经解决,测试结果如下: CV15V 1.043A CV14V 1.043A CV13V 1.043A CV12V 1.043A CV11V 1.043A CV10V 1.043A CV9V 1.043A CV8.5V 1.043A CV8V VCC欠压保护 0-94mA转绿灯 96mA以上转红灯 转灯比例 94/1043=9%,转灯比例可以控制在3-12% 64.一个最近贴片电容涨价的应对小技巧,贴片电容都预留一个插件位置,或104都改为224P,这样相对便宜很多。 |