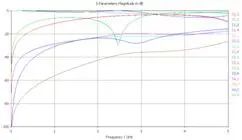

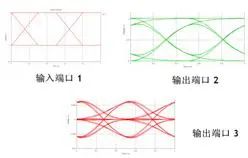

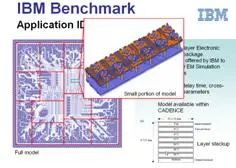

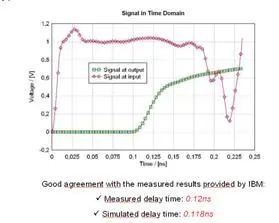

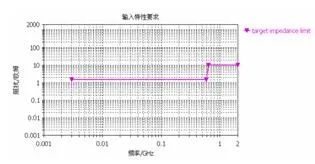

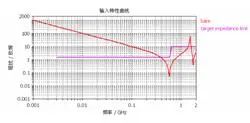

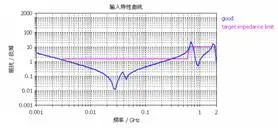

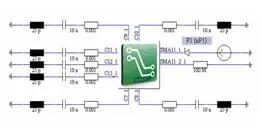

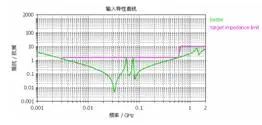

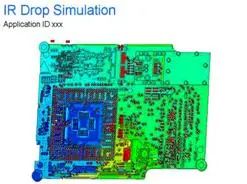

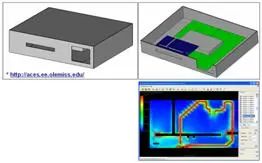

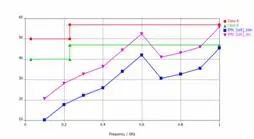

印制电路板(PCB:PrintedCircuitBoard)目前已广泛应用于电子产品中。随着电子技术的飞速发展,芯片的频率越来越高,PCB,特别是高速PCB面临着各种电磁兼容问题。传统的基于路的分析方法已经不能准确地描述PCB上各走线的传输特性,因此需要采用基于电磁场的分析方法充分考虑PCB上各分布式参数来分析PCB的电磁兼容问题。CST是目前全球最大的纯电磁场仿真软件公司。其产品广泛应用于通信、国防、自动化、电子和医疗设备等领域。2007年CST收购并绝对控股了德国Simlab公司,将其下整个团队和软件全面纳入CST的管理和软件开发计划之中,同时在原有PCBMod软件基础上开发全新算法和功能,并更名为CST印制板工作室(CSTPCBSTUDIOTM)。通过把EMC仿真工作集成到整个产品的开发流程中去,可以帮助设计者大幅降低所设计产品通不过EMC测试的风险。这样既可以帮助设计者提升对电磁现象的理解同时还可以帮助设计者有效的判断哪种电磁设计可以提升产品的性能水平。 CST印制板工作室相比业内其他软件最大的优势就是,它不只能解决印制板自身的电磁兼容问题,如过孔导线器件之间EMC,基于CST设计环境(CSTDESIGNENVIRONMENT)其他工作室的协同仿真,CST印制板工作室还能解决印制板对外的电磁辐射和加载外部器件情况下的电磁兼容问题,如与CST微波工作室(CSTMICROWAVESTUDIO?)协同仿真印制板加载在机箱中对周围器件和外部的电磁辐射,加载外部设备和上层建筑后的电磁兼容问题等等,工作室之间完全无缝连接,统一在CST设计环境下协同仿真,实现了印制板内外系统的电磁仿真。 目前PCB的电磁兼容性问题大致可以分为三类:信号完整性(SI)、电源完整性(PI)和电磁辐射(EMI)。 印制板信号完整性SI 对于印制板整板或某些网络走线间的网络传递函数是描述印制板上信号线信号完整性以及信号线间串扰度的定量表征。CST印制板工作室采用2D边界元法(BEM)和2.5D部分元等效电路(PEEC)提取PCBLayout的分布式参数,并采用基于SPICE模型的仿真器对印制板进行信号完整性仿真。图1所示的是一印制电路板上的两条走线。这两条走线物理上没有相连,当走线上传输信号频率比较低时,可以用基尔霍夫定律进行分析,即这两条走线是互不相关的。但是左边走线的2号端口与右边走线的3号端口间距比较近,当这两条走线上的信号频率不断上升时,它们之间分布式电容会导致原本不相连走线上的高频信号串扰到另一条走线上。  图1PCB模型 CST印制板工作室采用的部分元等效电路是基于积分形式的Maxwell方程,对PCB结构网格化成很小的电气单元,用等效电路分别计算各单元间的耦合关系,从而生成等效电路矩阵,使电磁场的求解转化成相应的等值电路方程的求解,是一种有效的电路参数建模和参数提取方法。如图2所示的PEEC网格中,红色部分表示电阻和自感,蓝色部分表示的电容和互感。  图2PCB网格 提取完模型参数后即可利用CST印制板工作室的S参量仿真器进行广义S参量的仿真。如图3所示:  图3S参量结果 采用CST印制板工作室的时域瞬态仿真器,并结合软件自带的眼图输入信号,即可进行眼图的仿真。仿真得到走线另一端的接收信号以及邻近走线上的串扰信号。如图4所示:  图4眼图输入、输出及串扰信号 除了CST印制板工作室,CST微波工作室也可以进行印制板的信号完整性分析。CST微波工作室是通用的高频无源仿真软件,集时域和频域算法为一体包含七种全波算法:时域有限积分、频域有限积分、频域有限元、模式降阶法、矩量法、多层快速多极子和本征模法。图5给出了CST仿真IBM复杂PCB并进行信号完整性分析的考题,仿真得到的电压延时与实测只差0.002ns。[page]  图5IBM考题实物模型  图6仿真结果 印制板的电源完整性PI 实际情况下电源回路的阻抗不是恒定的,而是频率的某一函数。CST印制板工作室可以仿真由于印制板间各分布式参数导致的电源回路阻抗在各频带上特性,并可以帮助设计者发现高阻频段,通过改变布线或添加旁路电容等方法改善印制板的电源完整性。 在实际的工程应用中,为了保证电源完整性,通常对电源回路的阻抗特性有一定要求。如图7所示为一印制板的数字电源部分。对于该印制板,工程上对输入阻抗的要求如图8所示。  图7PCB电源层  图8输入阻抗特性要求 用CST印制板工作室对该PCB生成网格后,建立如图9所示的电路以仿真裸板情况下的输入阻抗特性。该电路中在原本加电容的位置用100MΩ代替以模拟开路情况下的阻抗。  图9裸板时的仿真电路  图10裸板时的输入阻抗特性曲线 显然图10显示的裸板情况下的输入阻抗的特性曲线在低频时不满足输入阻抗的特性要求,在高频时也有部分频段超标。要改善输入阻抗的话可以考虑添加旁路电容,在仿真电路的电容位置加上容值为10nF的电容,同时为了更加准确地模型实际的电容的特性,需要考虑电容自身的寄生电感和电阻。这里,将电容的寄生电感值设为1nH,电阻值设为0.01Ω。其仿真电路如图11所示。  图11仿真电路  图12输入阻抗特性曲线[page] 从图12所示的输入阻抗特性曲线可以看出:在加入旁路电容之后,在低频段,电源的输入阻抗特性已经有了很大的改善,但是在高频时仍有一些频段超标。从阻抗特性上可以看到在高频段,阻抗已经呈现电感的特性,因此高频段的超标极有可能是由于电容的寄生电感的造成的。为此可以考虑选用质量更好的电容。这里,选用的电容的寄生电感为25pH,仿真电路如图13所示。  图13仿真电路  图14输入阻抗特性曲线 从图14所示的输入阻抗特性曲线中可以看到:选用寄生电感比较小的电容可以有效地抑制输入阻抗的高频段特性。从而保证在所要求的频段上输入阻抗均满足要求。 随着当今集成电路对供电稳定性的要求,印制板设计工程师需要关注于低电压、低翻转门限与大电流、多层长线供电所造成的压降。利用CST电磁工作室的稳恒电流求解器可以仿真整个PCB的电压分布,如图15所示:  图15IR-Drop分析 印制板电磁辐射EMI 对于电子产品的电磁辐射,国际电工委(IEC:InternationalElectrotechnicalCommission)制定了强制标准。通常,印制板都只是系统中的一部分,在进行电磁辐射分析的时候除了要考虑印制板本身的辐射问题外,还需要考虑系统中其它设备对对电磁辐射的影响,尤其是带有通风孔机箱的屏蔽效能。CST印制板工作室在进行SI仿真的同时,可以得到印制板上电流分布的幅度和相位信息,并通过与CST微波工作室的协同将该电流分布作为激励源,然后再加上机箱,充分考虑孔、缝对电磁辐射的影响。仿真的结果自动与内嵌的EMC国际标准限值进行对比,如图16所示。   图16电磁辐射的协同仿真 因此利用CST仿真软件,根据不同的电磁兼容问题,选择合适的工作室和求解算法,可以有效地对印制电路板的电磁兼容问题进行分析。同时利用软件强大的图像显示功能,直观地反映电磁场的空间分布,从而帮助印制板工程师准确定位可能存在电磁兼容问题的区域,在产品的研发阶段及早发现并解决电磁兼容问题。 温馨提示: 对产品进行EMC整改时,首先应考虑到单个产品整改与批量生产时的差异性。一般来说,EMC整改时会对产品各个部分进行仔细调整,所使用的对策及元器件都是反复挑选的。而在批量生产时,由于生产为流水线作业,很难对产品各个部分仔细调整,再加上所采用元器件的批量离散性,批量生产产品的EMC性能也会参差不齐。只有在产品整改时为这种差异留下足够的裕量,才能保证批量生产产品的EMC标准符合性。若批量生产的工艺一致性控制良好,所使用元器件的一致性很好,同时考虑到实验室测试设备不确定度,传导骚扰的整改至少要有4dB的裕量;辐射骚扰的整改至少要有6dB的裕量。若工厂的生产工艺一致性控制不是特别到位(如主要是手工或半手工操作,而非计算机控制的自动化操作),所采用的元器件离散性较大,建议裕量至少再提高3dB。必要时,可通过对EMC整改后批量生产的产品抽取至少三台样品进行相关项目检测,以确定是否均满足标准要求及结果的离散性如何,是否符合标准中对批量产品测试的标准符合性的判定准则。若都合格,则可判断该整改措施是合适且有效的。 对常见电磁兼容不合格,综合采用以下整改措施,一般可解决大部分问题:屏蔽问题: 加强屏蔽、减少缝隙:可以在屏蔽体的装配面处涂导电胶,或者在装配面处加导电衬垫,甚至采用导电金属胶带进行补救。 导电衬垫可以是编织的金属丝线、硬度较低易于塑型的软金属(铜、铅等)、包装金属层的橡胶、导电橡胶或者是梳状簧片接触指状物等。 布局布线问题: 在不影响性能的前提下,适当调整设备内部各部件之间的布局,电缆走向和排列,以减小不同类型的部件、电缆相互影响。 接地问题: 加强接地的性能,降低接地电阻;对于设备整体要有单独的低阻抗接地。 接口问题: 加强接口的滤波和金属机箱与屏蔽层的连接;在设备电源、信号的输入、输出线上改进或加装滤波器。 电缆问题: 正确选择传输电缆;电缆的屏蔽层正确接地;改变普通的小信号或高频信号电缆为带屏蔽的电缆;改变普通的低频、大电流信号或数据传输信号电缆为对称绞线电缆。 关键部位的处理: 对重要部件、板卡、器件进行屏蔽、隔离处理,如加装接地良好的金属隔离仓或小的屏蔽罩等。电路和电源问题:改进或增加电源、电路的滤波,以旁路去其高频干扰。 |