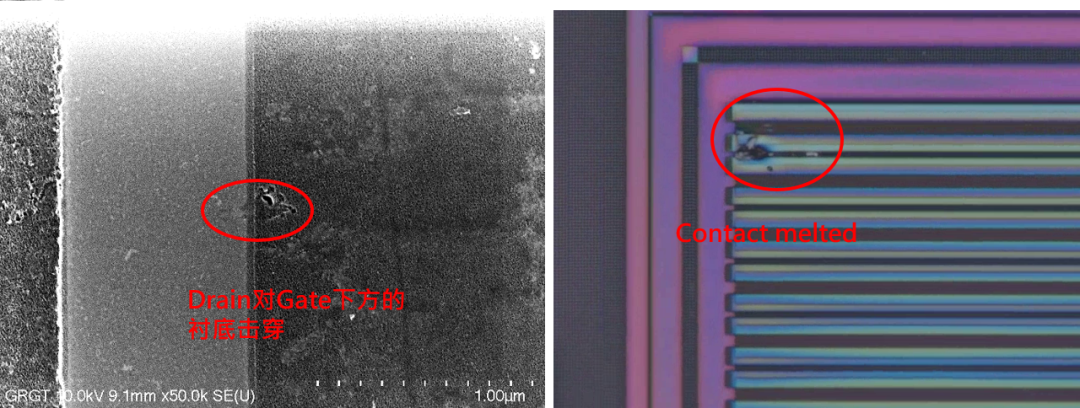

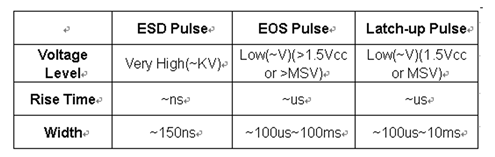

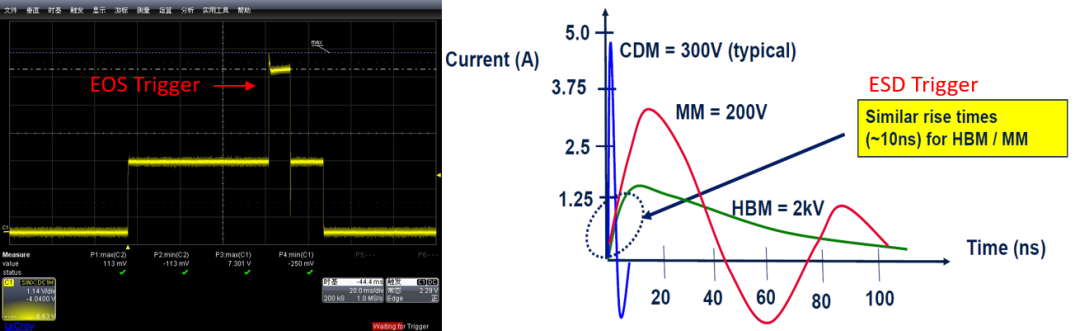

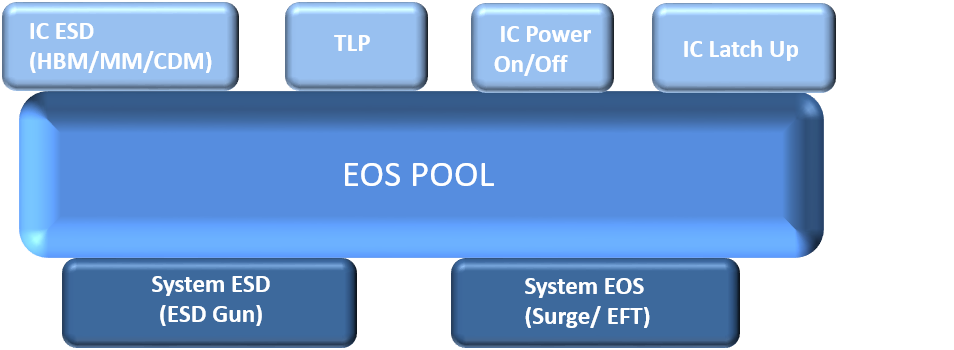

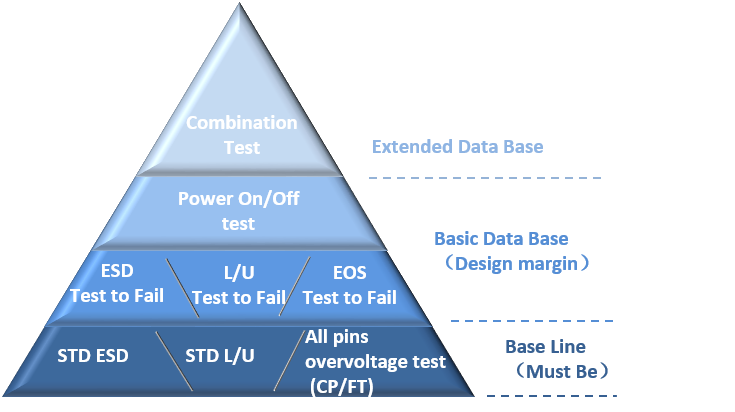

50%——在品控界是个很可怕的数字,有一对兄弟难题占到了产线不良率的一半“江山。” 在电子器件组装过程中,EOS(Electrical Over Stress)与 ESD(Electrical Static Discharge)造成的集成电路失效约占现场失效器件总数的50%,且通常伴随较高不良率以及潜在可靠性问题,是产线一大杀手。 当问题发生时,应该如何查找真因、寻找解决方案,一直以来都是困扰现场工程师、品控工程师的难题。广电计量集成电路失效分析实验室,通过多年的行业积累,总结出一套相对完整的针对EOS/ESD的分析方法,通过失效分析、模拟验证等手段,可以更好地协助现场工程师与设计工程师提升产线良率及IC的可靠性。 产线失效到底是由EOS还是ESD引起? 我们在做失效分析时,最常听到客户的要求是希望知道root cause是EOS还是ESD,确认失效机理及真因,是改善良率的第一步,也是非常关键的一步。通常,我们区分EOS还是ESD会首先通过失效分析手法挖掘IC的物理失效现象,然后从现象上去区分。 常见ESD物理失效表现:衬底击穿、多晶硅熔融、GOX pin hole、contact melted、metal melted等(见图1), 常见EOS物理失效表现:氧化层、金属层大面积熔融以及封装体碳化等现象(见图2)。  图1:常见ESD物理失效现象  图2:常见EOS物理失效现象 为什么EOS和ESD会造成不同的失效现象? ESD从广义上属于EOS的一种,但是现场应用中我们通常把ESD单独归类,除此之外的过电应力统归于EOS。EOS 是指长时间(几微秒到几秒)持续的过压或大电流造成的局部过热导致的失效,其电压、电流相对ESD较低,但是持续时间长能量更高,经常有同一功能区块多处大面积的burnout现象。ESD 单指在静电放电过程中瞬间高电压(通常在几千或上万伏特)大电流(1~10A)状态下引发的失效现象,主要特征为放电时间极短(1~100ns),因此一般呈现为轻微的点状失效。  表1:EOS/ESD信号特征  图3:EOS/ESD脉冲波形 什么情况下无法区分EOS/ESD? 一种情况是短脉冲EOS(持续时间几个微秒)与ESD的物理损伤十分相似,比如只造成很小面积的金属熔融,这种情况就很难区分是EOS还是ESD的能量造成。另一种情况是IC先经过了ESD损伤,在后续功能验证时大漏电流诱发了burnout现象,使得IC表面同时存在EOS和ESD的物理失效特征,尤其常见于PAD旁边的IO buffer线路上,这种情况下单从物理失效现象是无法判断初始失效是否由ESD导致。当遇到EOS/ESD无法区分的情况,需要通过模拟实验进一步验证,对IC或系统使用不同模型进行EOS/ESD模拟测试(见图4)test to fail,并针对失效IC进行分析。 通过对比验证批芯片与实际失效芯片的物理失效现象(失效线路位置及失效发生的物理深度),不仅可以用来归纳真因,还可以了解IC或系统在不同条件下的耐受等级,从而进一步指导优化产线防护或IC的可靠性设计。针对新投产芯片也可以考虑从多维度进行EOS/ESD的验证与分析(见图5),不断提升IC的可靠性品质。  图4:IC常见EOS模拟验证方式  图5:IC常见EOS/ESD测试项目 综上所述,当产线发生EOS/ESD失效时,应该从哪些方面进行分析及改良?我们通常建议客户参考以下流程进行: 1. 针对失效IC进行电性及物理失效分析,确认其物理失效现象(失效点对应的电路位置及失效的物理深度),配合现场失效信息收集,初步推断EOS/ESD失效模型; 2.针对EOS/ESD无法判断的情况,对相关IC或系统进行EOS/ESD模拟试验,验证其电压、电流耐受等级,并针对失效芯片执行失效分析,对比实际失效状况,归纳真因及梳理改善方向; 3. 探测现场容易发生EOS/ESD的位置(例如使用ESD Event Detector或高频示波器),针对产线应用进行改良。

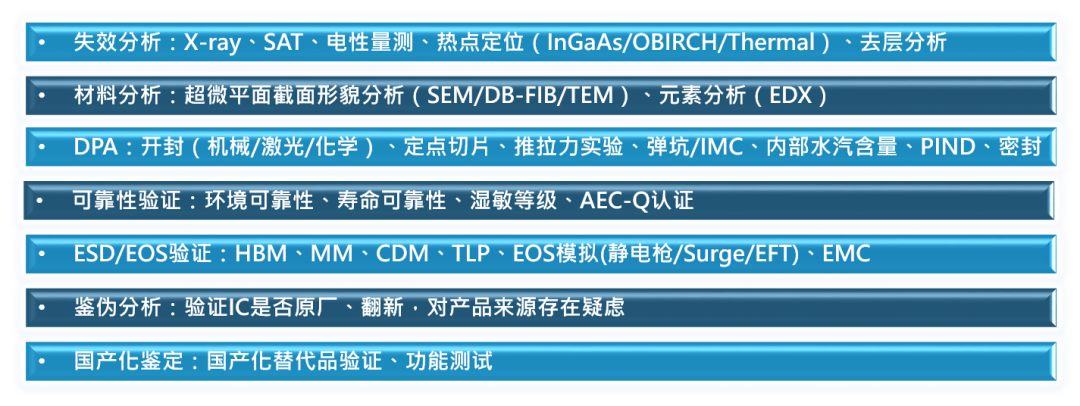

广电计量设备及解决方案 广电计量集成电路失效分析实验室,配备完善的EOS/ESD/RA等测试设备及完整的失效分析手法,拥有经验丰富的材料及电性能可靠性专家,可以针对IC进行全方位的失效分析及可靠性验证方案的设计与执行。  |