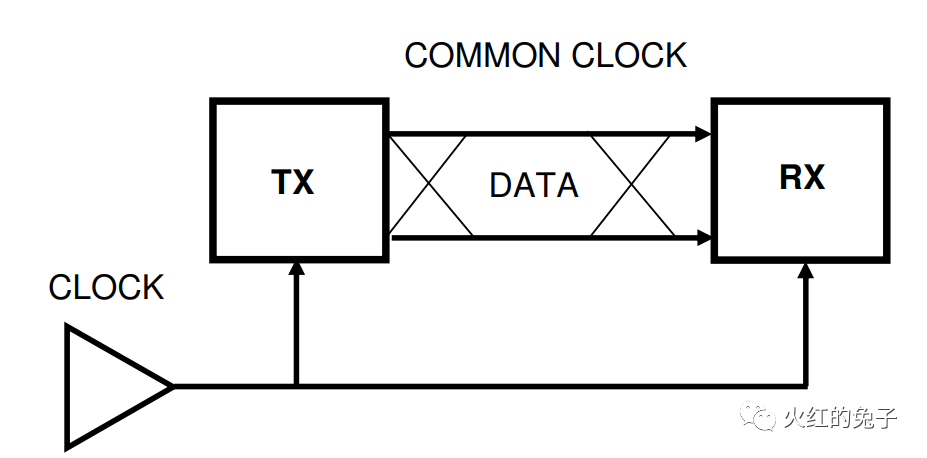

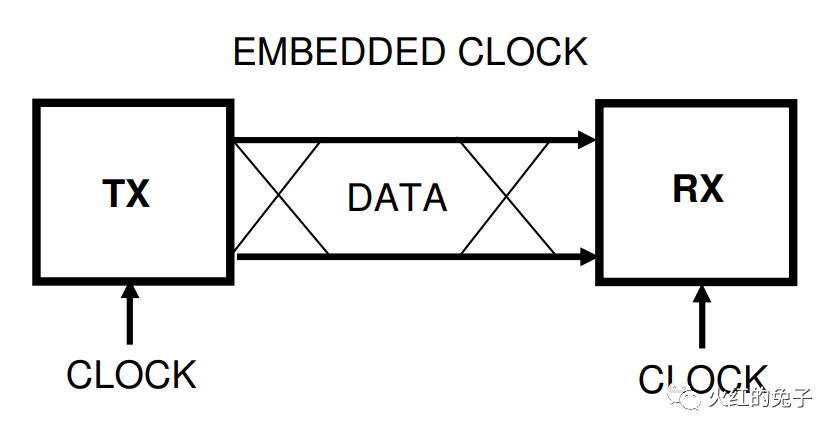

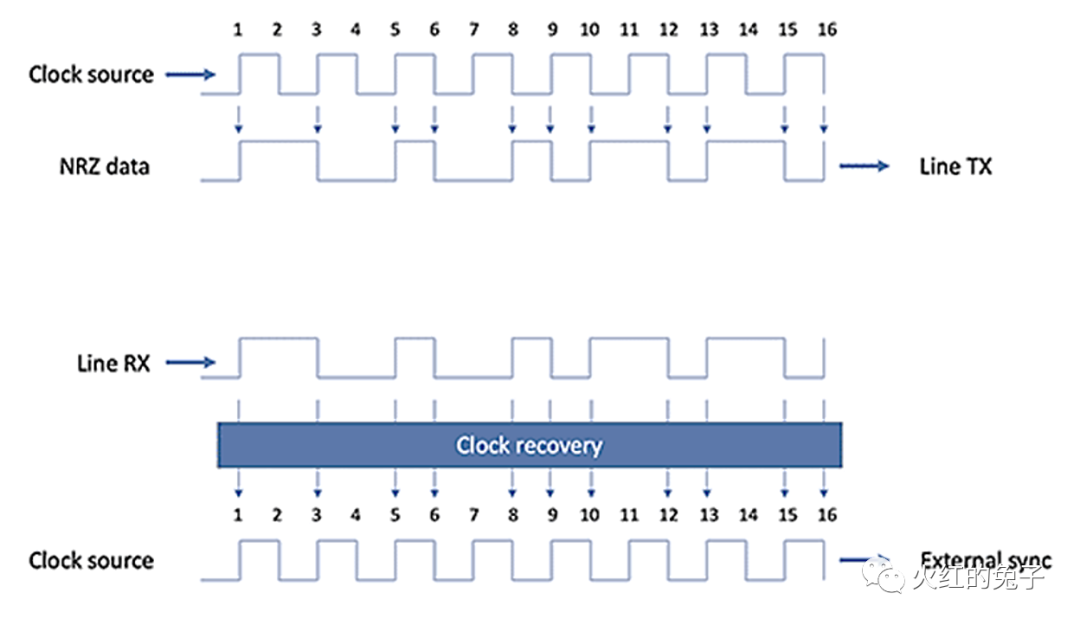

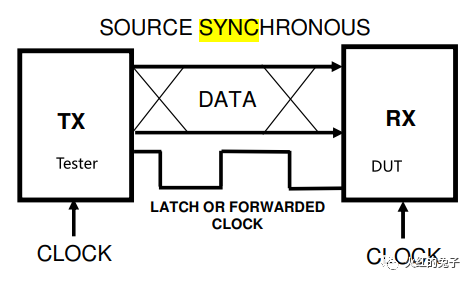

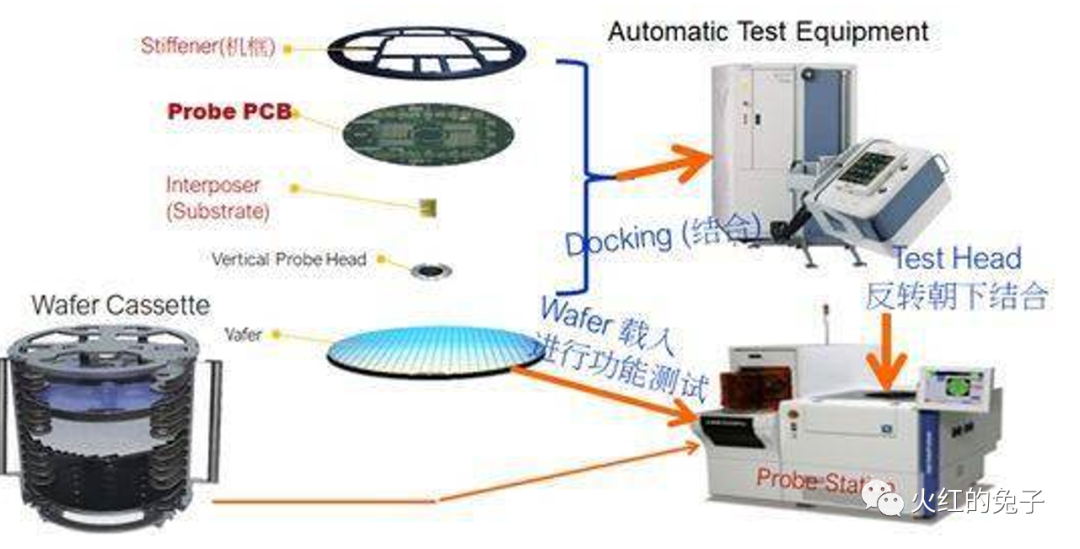

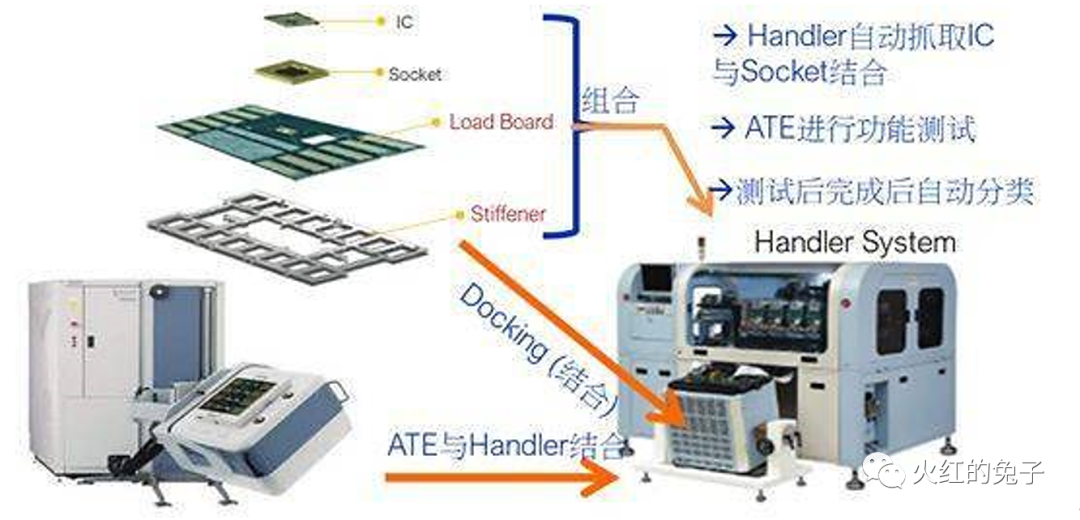

同步是ATE机台在数字信号测试中的一个核心话题,可以依据信号的速度分为两个层次,低速数字信号同步和高速数字信号同步。常用的SCAN/ATPG、MBIST、jtag协议的IP测试,适用于ATE机台的低速数字信号同步,相对简单。本章节将主要讲述ATE机台是如何实现DUT的不同IO之间的相位同步。 理解机台的接口时序同步机制对于DFT工程师在制定STA接口时序收敛策略是否有帮助? 对于ATE工程师,深入了解机台的高阶同步操作和原理,相信对测试flow的最佳实现策略、为什么、以及如何优化COT确定有很大帮助(有需要以后开单章)。 本篇文章面向DFT工程师角度,不会有太复杂的东西,从介绍中结合实际经验,想象一下产生的pattern是如何准确地符合预期地被执行。 本篇大纲 1. 时钟架构的简单分类,如何保证时钟和数据的相位关系? (第1点也可以跳过,不影响后续2点介绍。) 2. 机台在测试DUT时的硬件结构和信号传输路径,哪里做补偿? 3. 低速数字信号测试,机台补偿的方法和原理。 PART01 时钟类型 根据数字信号速率时钟架构一般可以分为全局时钟(common clock)和源同步时钟(source synchronous)两类。 全局时钟常用于低速数字信号接口:如下图,所有参与通信的设备都从一个中央提供的系统时钟中获取它们的数据生成和采样时序,很简单没什么好说的。  源时钟同步(source synchronous): 时钟源同步,单向数据信号的时序参考由生成这些信号的同一器件提供的时钟,而不是全局时钟。比如常见的phy使用的CDR(时钟数据恢复)技术,就是一种典型的源同步时钟框架。  下图的波形时序图:CDR VS 全局时钟的差异。  那么机台测试DUT时使用那种时钟架构进行测试呢? 我更偏向源时钟同步的另外一种类型:  假设TX为机台,RX为DUT,机台内部同源时钟产生时钟和数据,在机台侧保证不同信号的激励在一个较小的相位误差和较高的信号质量(较小jitter),因此只要能够保证数据路径和时钟路径传播的等长,那么就可以维持在DUT侧的数据和时钟之间的相对相位关系。 结论: 机台侧发送时钟和数据给DUT,且机台有能力保证机台侧各信号的相位关系稳定,因此只要能够保证数据路径和时钟路径传播的等长,那么就可以维持在DUT侧的数据和时钟之间的相对相位关系稳定。 PART 02 激励信号路径 DFT向量一般看中两个阶段的测试CP和FT两个阶段,CP和FT在硬件上的区别简单的来说: CP是测试的PCB(Load Board)上集成了基板和装针,可以直接contact wafer的bump。(了解详细点的可以看下图,或者跳过)  FT 是测试已经封装好的IC芯片,因此只需要一个socket和PCB(Load Board),IC放置于socket中既可开始测试:(了解详细点的可以看下图,或者跳过)

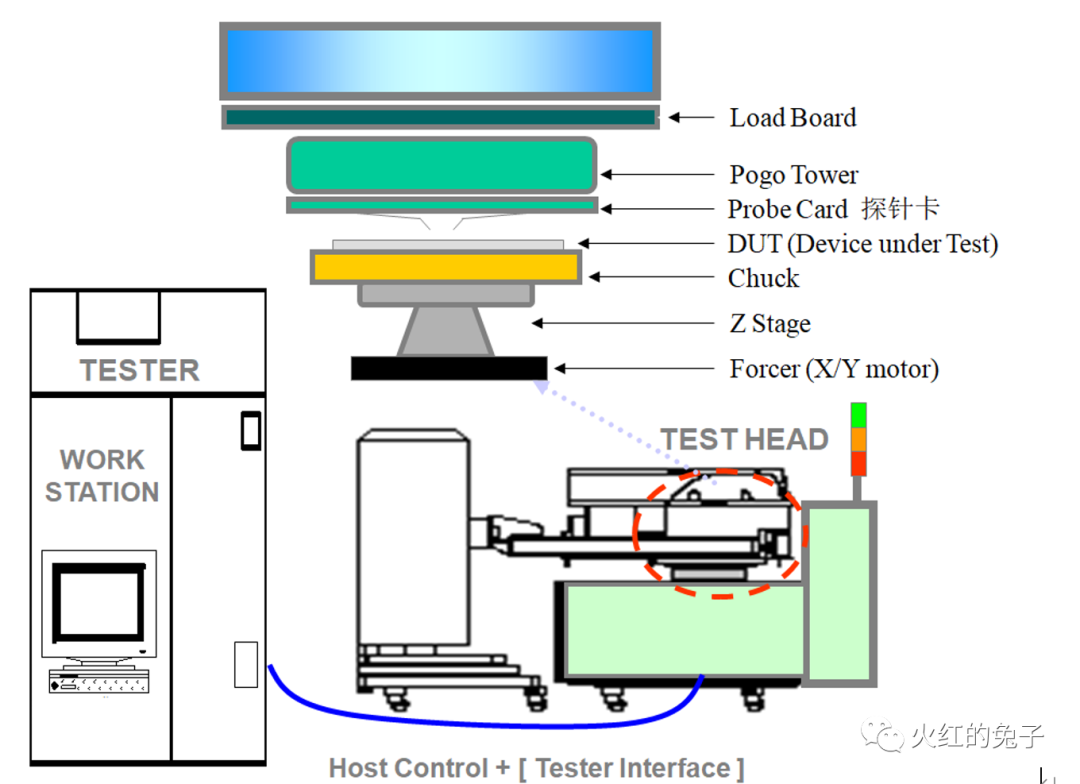

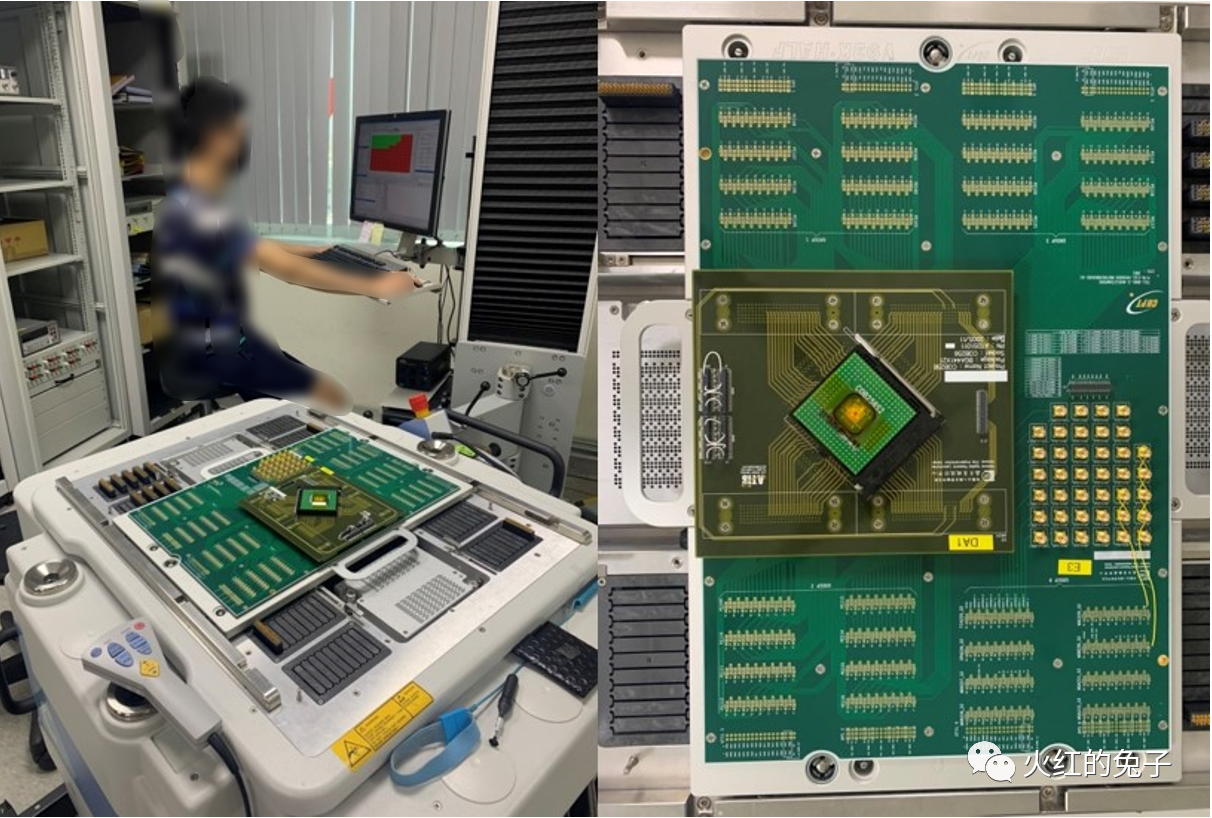

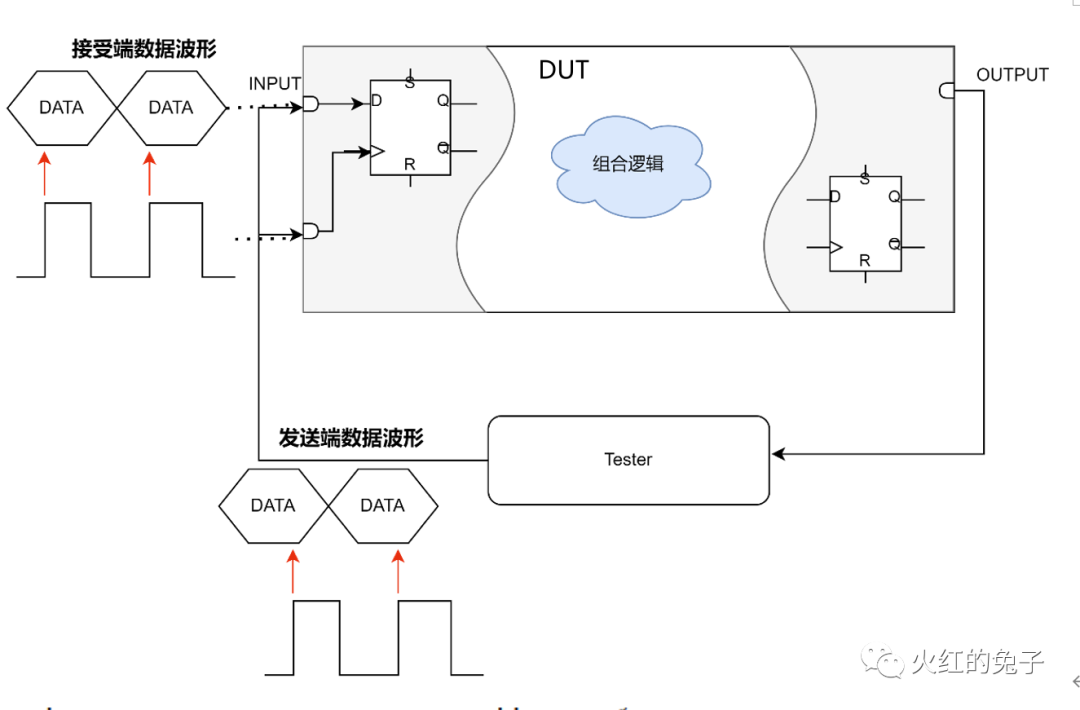

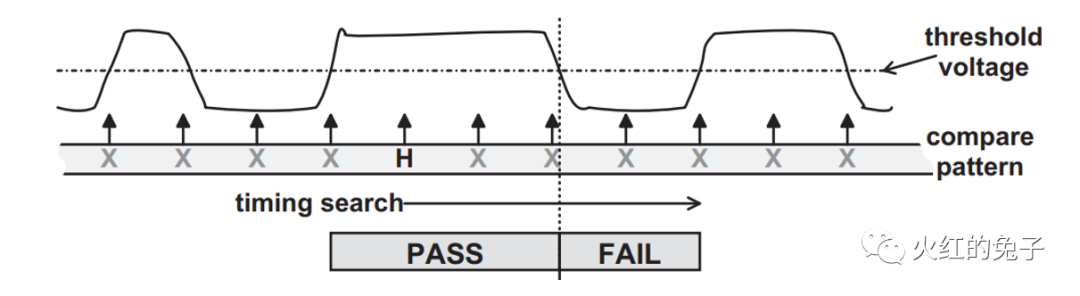

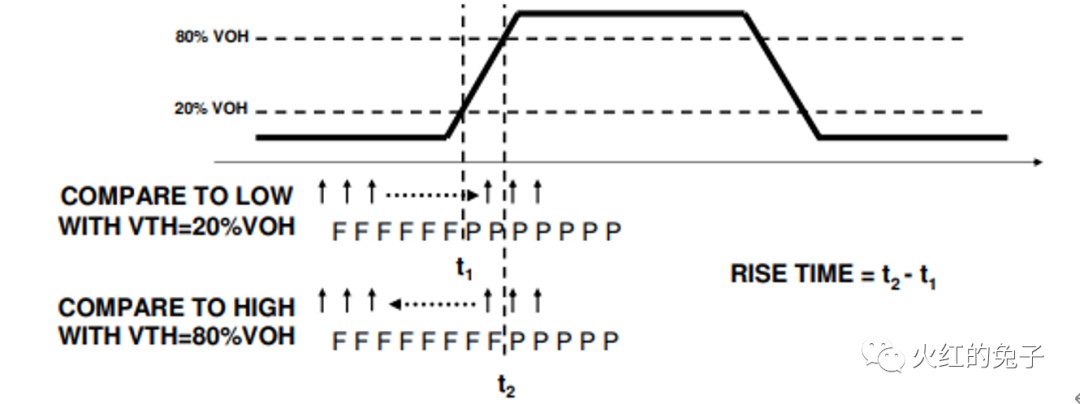

那么以FT为例子便可以提取总结出本小节的信号传输路径了, 如下图从左至右:(若下图异常,可以将手机深色模式的请调为浅色)  信号从Tester FPGA->Tester Cable -> Tester Pogo Pin -> Load Board -> Socket -> Substrate -> DUT. Tester Cable -> Tester Pogo Pin :由机台定期保养和校准保证drive沿相位的一致,用户无需要关心。 Tester Pogo Pin -> Load Board: Load Board一般比较大,走线基本在10in以上,因此有较大的时钟delay. Load Board -> Socket -> Substrate : Socket的针在选型之后一般都保证了等长,且非常短,引入的相位偏移忽略,基板同理。 IC的接口时序由STA signoff保证。 总结: 核心影响因素是Load Board的时延,得出了和第1节一样的结论。 如果能够保证Tester Pogo Pin -> DUT的不同IO之间的相位关系,那么机台就保证了信号在DUT接口时序的相位同步。 PART 03 机台如何实现同步 在第2节已经说明了Tester可以保证不同信号之间的信号相位同步。那么关键就是如何补偿Tester到DUT的路径,如下图所示,如果不做补偿,可以看到发送端时钟和数据的相对相位在DUT接受端已经发生了改变,这将导致测试不及预期,发生时序违例。  那么机台如何补偿这部分的走线延迟呢?Tester Pogo Pin -> DUT的走线补偿。 通常在测试开始之前,TE工程师会建立一个fixture文件存储Load Board每一根数字走线的时延,具体方法是使用TDR(Time-domain reflectometer)技术的反射脉冲来确定Load Board的时延参数。  TDR简单来讲,如上图就是发送一个高脉冲信号,然后测量沿导体的反射信号。通过脉冲信号发送时刻和反射信号接收时刻就可以确定走线的时延。和卫星通信确定两端距离异曲同工之妙。 那么为什么发送一个高脉冲信号,就一定能接受一个反射信号呢? TE工程师在进行TDR操作时,会首先去掉DUT,因此在Socket侧是开路的,根据阻抗计算公式:  开路时,RL为无穷,Z0为50欧姆,因此反射系数为1。也就是信号全部反射。(具体阻抗匹配公式涉及麦克斯韦方程和边界条件的二阶微分方程求解,有兴趣的可以搜Smith chart或阻抗匹配,这里不展开) 这样TE通过机台的TDR操作,机台就可以补偿输入和输出方向的走线延迟。 进一步延申1,如果STA在不同corner收敛了,但是余量较小,遇到工艺偏差,导致输出端的采样时刻不够合理?这时候怎么办?  比如上图比较H时,不是在中间去采样的,而是在靠近上升沿去比较的,那么在扫shmoo时,很可能遇到shmoo异常图形,你能反推到是这里的采样时刻不当引入?  如何补偿: TE工程对测试项进行PIN MARGIN测试,类似于扫一维shmoo,search最佳采样点,如上图通常取FFFFFFPPPPPPPFFFFF中间P对应的采样时刻,补充到fixture文件中。( = 眼图中心采样) 进一步延申2: 既然机台具备强大的Per Pin的补偿能力,那么对于IO内部在STA中的接口时序设置如max_delay,IO延时设置是否有帮助呢? 根据实测经验,虽然IO的delay较大,但是在不同corner之间的差异相对不大,可以类比为时钟latency+skew。 如果TE工程师能够支持Training,是不是可以适当调整STA的接口设置? |