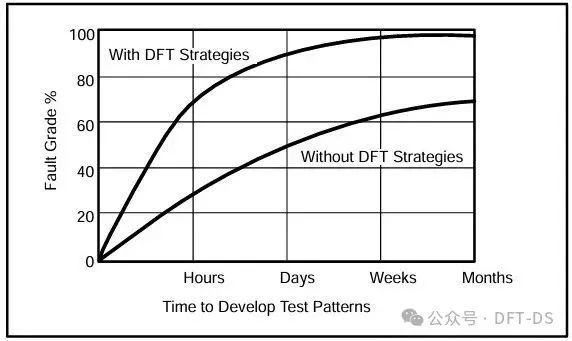

一、DFT的本质与价值1. 核心定义在当今数字化时代,芯片作为现代科技的核心,其复杂度和重要性都在不断攀升。从智能手机到AI,从汽车电子到IOT,芯片无处不在,而其质量的优劣直接决定了产品的性能和可靠性。然而,随着芯片制程的不断缩小(如今已达到18A甚至更小),芯片的规模和复杂度急剧增加,测试难度也呈指数级增长。测试作为芯片尤为重要的一个环节,是不能忽略的。DFT(Design For Test,可测性设计)技术应运而生,成为芯片设计中不可或缺的关键环节。 DFT是在芯片设计阶段植入专用电路结构,使芯片具备自我检测能力的设计方法论。在芯片设计过程中引入测试逻辑,并利用这部分测试逻辑完成测试向量的自动生产,从而达到快速有效的芯片测试的目的。其目标是在流片后快速定位硅片缺陷,确保出厂芯片功能可靠。  2. DFT的目标和作用 1)目标1. 提高测试覆盖率:通过插入测试逻辑,确保芯片中的每个逻辑单元和存储单元都能被测试到,从而提高测试覆盖率。3. 降低测试成本:通过优化测试流程,减少测试时间和测试设备的依赖,从而降低测试成本。 4. 提高测试效率:通过自动化测试逻辑,提高测试效率,减少手动测试的工作量。 5. 确保芯片质量:通过检测和定位芯片中的潜在故障,确保芯片的质量和可靠性。 2)作用1. 早期发现缺陷:在设计阶段引入测试逻辑,能够在制造完成后快速发现制造和封装过程中的缺陷,减少返工和修复成本。3. 提高生产效率:通过优化测试流程,减少测试时间,提高生产效率。 4. 满足行业标准:在某些行业(如汽车电子、航空航天等),DFT是满足行业标准(如ISO-26262/AEC-Q100)的必要条件。 |

| 功能测试 | DFT测试 | |

| 测试目标 | 设计过程中的bug | 生产制造过程中的Defect |

| 测试封装 | 封装后芯片级 | 晶圆级,封装后 |

| 测试平台 | PCB | ATE |

| 测试时间 | 长 | 短 |

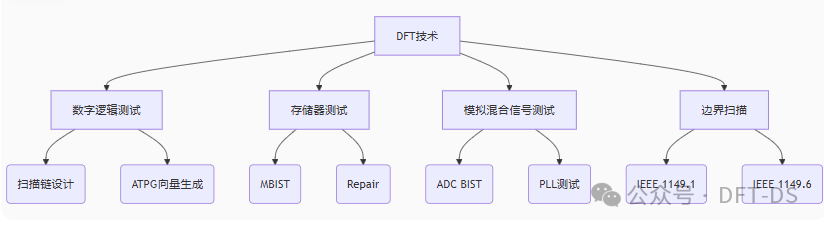

二、DFT技术体系全景图

扫描链(Scan Chain):

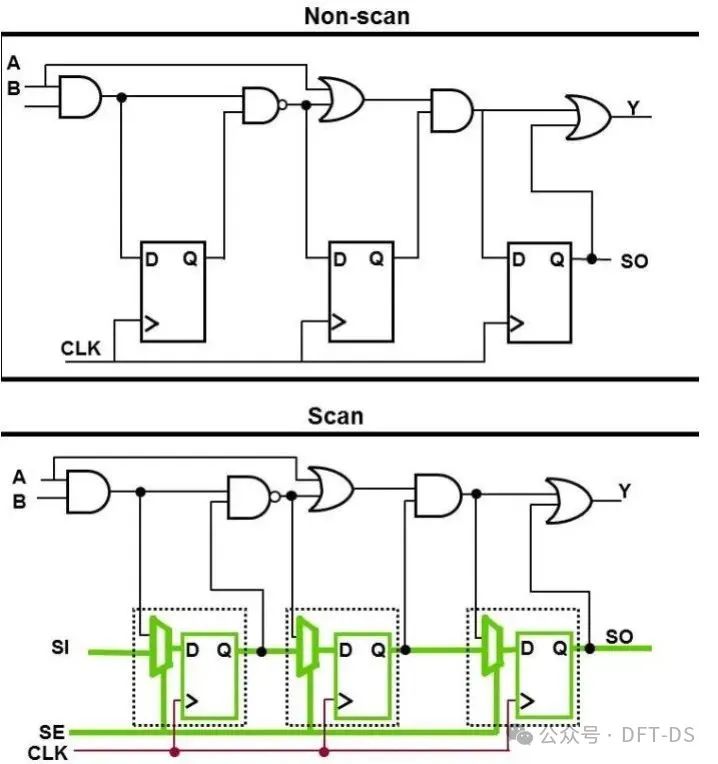

扫描链是DFT中最常用的技术之一,通过将寄存器连接成一条链,方便测试信号的加载和读取。扫描链技术能够有效检测寄存器和组合逻辑中的故障。

内建自测(BIST):

BIST技术允许芯片在不需要外部测试设备的情况下进行自我测试。BIST模块能够自主生成测试向量、施加测试激励,并捕获和分析响应信号,从而判断电路是否存在故障。

边界扫描(Boundary Scan):

边界扫描技术通过在芯片的输入/输出端口处插入测试逻辑,能够检测和修复芯片与外部电路之间的连接问题。边界扫描技术广泛应用于系统级测试中。

IP Test & Other:

硬核IP/软核IP-BIST and SCAN, 某些高速芯片的Loopback测试技术等。

三、核心DFT技术详解

1. 扫描链(Scan Chain)

· 原理:将时序元件(触发器)改造为移位寄存器· 实现流程:

扫描链是DFT技术中最常见的方法之一,主要用于测试逻辑电路。其基本原理是将芯片中的寄存器(Flip-Flop)重新配置为一个长的移位寄存器,在正常模式下,寄存器正常工作;而在扫描模式下,寄存器可以像移位寄存器一样加载和卸载数据。通过这种方式,工程师可以快速地将测试向量加载到寄存器中,并观察寄存器的输出,从而检测寄存器和组合逻辑之间的连接是否正确。

扫描链技术的优势在于它能够将复杂的时序电路测试问题转化为组合逻辑的测试问题,大大简化了测试向量的生成和应用。此外,扫描链还支持自动化测试向量生成(ATPG),进一步提高了测试效率。根据最新的研究,Scan chain技术在某些复杂芯片中的应用可以将Test coverage轻松提高到99%及以上。

· 关键参数:

o 扫描链长度:100-400寄存器/链(平衡测试时间与面积)

o 测试覆盖率:>95% (Stuck-at故障),车规>98%

Scan 相关可参考文章如下:

SCAN

2. 存储器BIST(MBIST/LBIST)

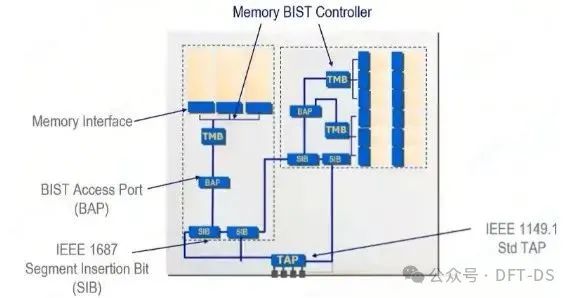

存储器BIST(MBIST):MBIST(Memory Build In-Self Test)是一种在芯片内部集成自测试逻辑的技术,主要用于测试芯片中的存储资源,如ROM和RAM。MBIST逻辑可以在芯片内部生成测试向量,并将测试结果与预期值进行比较,从而判断存储器是否存在缺陷。与传统的外部测试方法相比,MBIST不仅提高了测试效率,还减少了对昂贵测试设备的依赖。

MBIST技术的关键在于其测试算法的设计。为了确保测试的全面性和准确性,MBIST算法需要能够覆盖存储器的所有可能故障模式。根据最新的研究,MBIST技术可以将存储器测试时间缩短50%以上。此外,MBIST还需要考虑芯片的功耗和性能影响,以确保在测试过程中不会对芯片的正常运行产生负面影响。

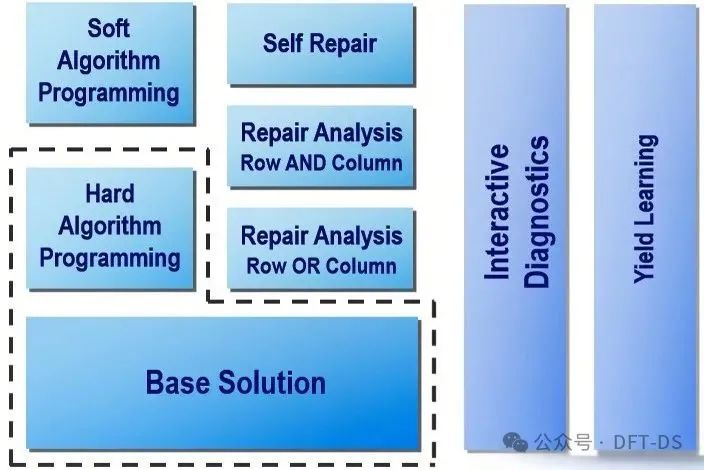

如下图所示为最basic的Mbist solution components。虚线部分为最基础内容算法实现和controller部分,任何的Mbist solution都必须包含,其他为可选项。而其他的部分包括,mem repair,diagnositcs,yield learning要看具体的公司和相应的design自行设计。

MBIST相关可参考文章如下:

MBIST

· 逻辑BIST(LBIST):

o 伪随机测试向量生成(LFSR)

o 响应压缩(MISR)

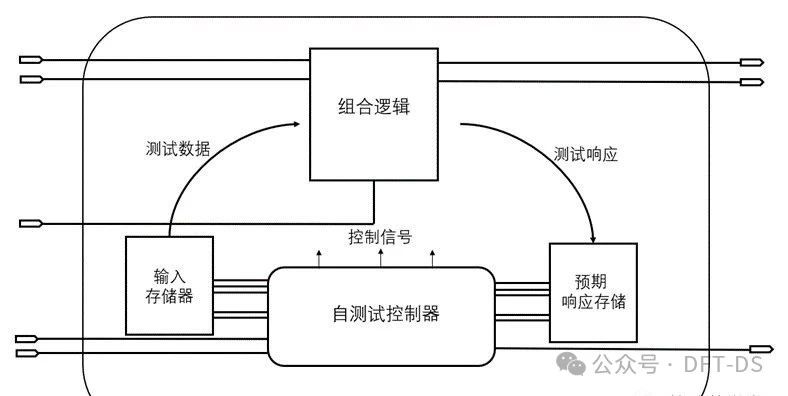

Logic BIST即逻辑内建自测试(logic Built-ln Self Test),该硬件电路结构的功能为生成测试数据,将其输入到被测电路,采集输出响应,验证输出结果是否正确,这一工作流程是由内建自测试控制器控制的,与ATPG过程类似的是我们可采用故障覆盖率来评价内建自测试的有效性。

LBIST相关可参考文章如下:

LBIST

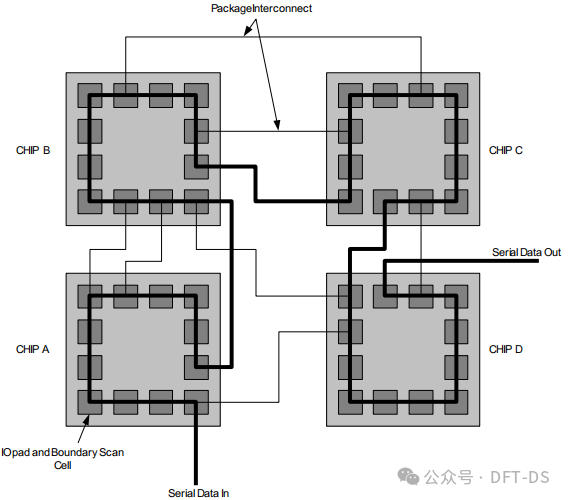

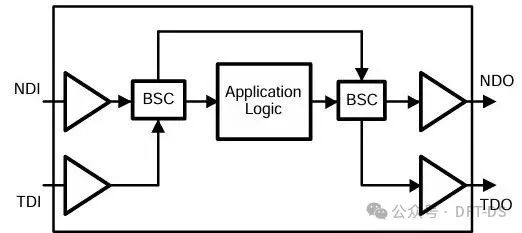

3. 边界扫描(Boundary Scan)

· 符合标准:IEEE 1149.1/6· 板级应用:芯片A TDI ──>BSD Cell──> TDO ──> 芯片B TDI/TDO

· 边界扫描技术主要用于测试芯片与外部封装、I/O接口以及芯片之间的互联。通过在芯片的边界处插入扫描单元,工程师可以在不接触芯片内部电路的情况下,对芯片的输入输出引脚进行测试。边界扫描技术的一个重要标准是JTAG(Joint Test Action Group),它允许多个芯片通过JTAG接口串联在一起,形成一个JTAG链,从而实现对整个系统的测试。

Boundary Scan技术的优势在于它能够提供对芯片外部连接的全面测试,减少了对物理接触测试点的需求。此外,边界扫描还支持ATPG和故障诊断,进一步提高了测试效率。根据最新的研究,边界扫描技术可以将芯片的外部连接test coverage提高到98%以上。

BSD相关可参考文章如下:

BSD

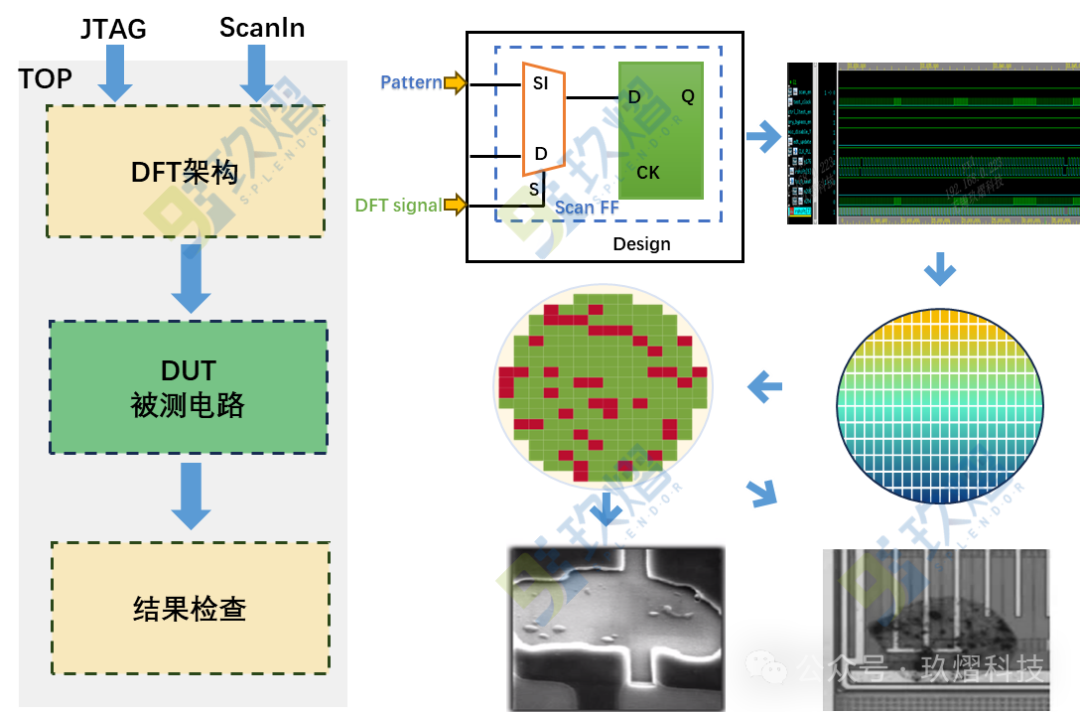

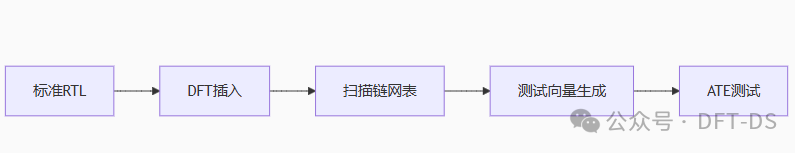

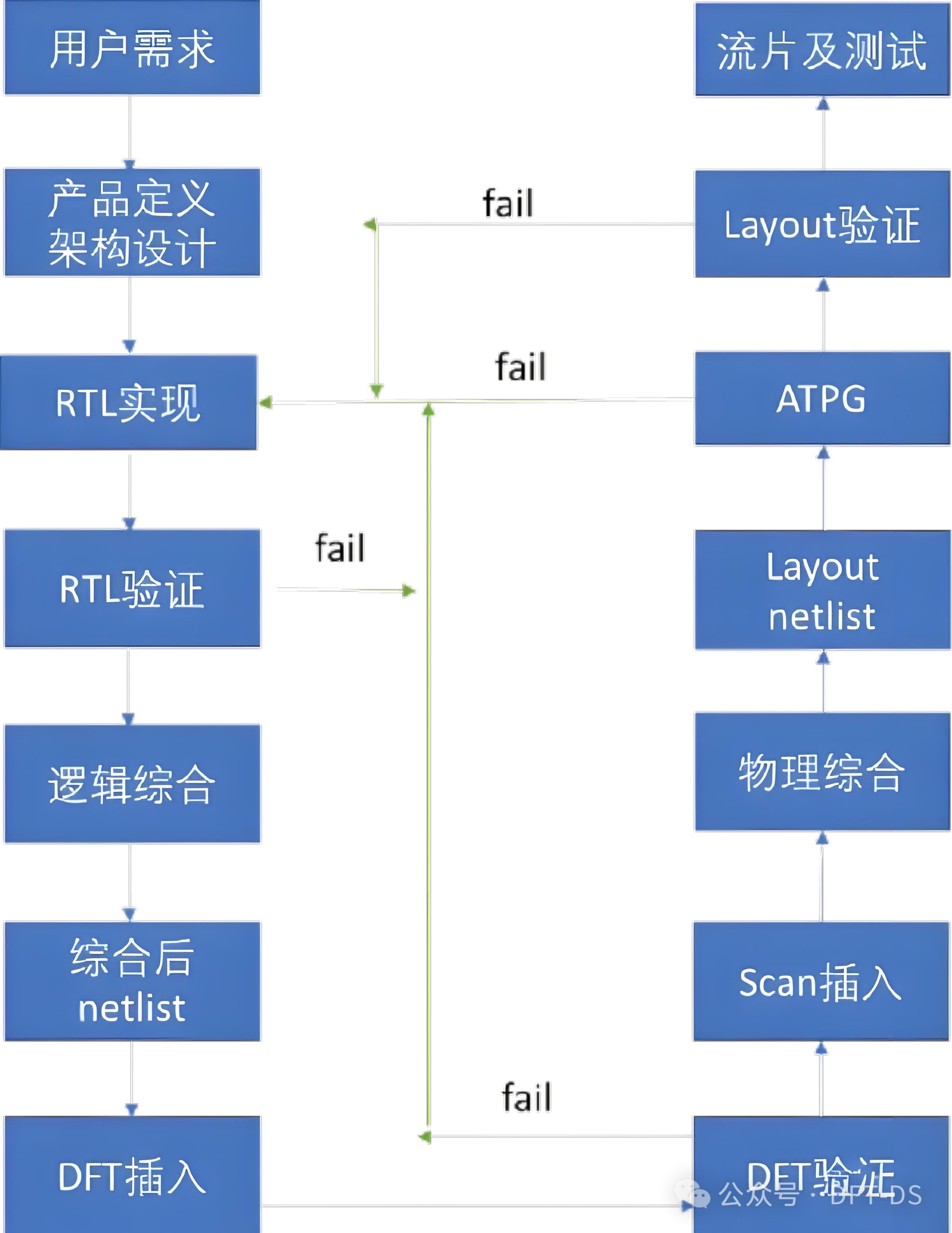

四、DFT设计流程

需求分析根据芯片的功能和应用需求,确定DFT的目标和要求。这包括测试覆盖率、测试时间、测试成本等关键指标。

DFT架构规划

根据芯片的特点和设计需求,定制DFT架构。例如,规划扫描链、BIST模块、边界扫描单元等测试逻辑的布局和连接方式。

DFT逻辑插入

在芯片设计中插入DFT逻辑,如扫描链、BIST模块、边界扫描单元等。这些逻辑需要与芯片的其他功能模块协同设计,确保不影响芯片的正常功能。

验证与优化

通过仿真和测试验证DFT逻辑的有效性,并根据测试结果进行优化。这包括优化扫描链的长度、调整BIST的测试算法、优化边界扫描的测试向量等。

ATE测试

在制造完成后,使用自动测试设备(ATE)对芯片进行测试。DFT逻辑能够显著提高ATE测试的效率和覆盖率。

五、DFT成本&质量分析

1. 面积开销

| 技术 | 面积占比 | 成本增加 |

| 扫描链 | 5-10% | <3% |

| MBIST | 3-8% | <2% |

| 边界扫描 | 1-2% | <0.5% |

2. DFT质量评价

测试覆盖率(Test/Fault Coverage):

测试覆盖率是衡量DFT质量的核心指标之一,它表示测试向量能够检测到的故障数量占总故障数量的比例。高测试覆盖率意味着更多的故障能够被检测到,从而提高芯片的可靠性。

测试成本:

测试成本包括测试设备的购置成本、DFT Pattern测试时间成本以及测试向量生成成本等。DFT设计应尽量降低测试成本,提高测试效率。

六、DFT工具介绍

市场上的三大DFT工具:

西门子的Tessent、新思的DFTC&TestMax以及Cadence的Genus& Modus Test Solution。

Tessent的EDT压缩架构在技术上的先进性,TestMax的设计与测试集成优势,以及Modus Test Solution的全面性,都是选择时的重要考量。此外,Tessent的用户友好GUI界面和简便的MBIST工具也是其显著的优势,使其在用户体验上占据了一定的优势。

用户反馈与案例研究:

Tessent的用户反馈:许多用户称赞Tessent的EDT压缩架构在处理大型设计时的高效性。案例研究表明,Tessent能够帮助用户显著降低测试成本和时间。此外,其直观的GUI界面和简便的MBIST工具也得到了广泛好评。

TestMax的用户反馈:用户普遍认为TestMax的设计与测试集成是其最大的优势。这种集成方法不仅提高了设计效率,还减少了设计周期。然而,在用户界面方面,TestMax略显不足,且MBIST工具未与TestMax集成,增加了使用的复杂性。

Modus Test Solution的用户反馈:Modus Test Solution的用户通常赞赏其与Cadence工具的无缝集成。尽管市场占有率较低,但Modus Test Solution在Cadence生态系统中提供了一致的用户体验。

总结与展望:

DFT作为芯片设计中的关键环节,通过引入扫描链、内建自测试(MBIST)、边界扫描等创新技术,显著提升了芯片的可测试性,将故障覆盖率提升至99%以上,同时将测试成本降低30%-50%。这种技术突破不仅加速了产品上市周期——据统计,DFT可使芯片开发周期缩短20%-30%,还通过早期故障检测减少了后期返工成本。

DFT技术的发展与芯片制造技术的进步紧密相连。随着芯片制程的不断缩小和复杂度的增加,DFT技术将不断演进,以满足更高的测试需求。未来,DFT技术可能会更加智能化、自动化,借助AI和大数据技术,实现更高效的故障诊断和测试优化。同时,随着量子计算等新兴技术的兴起,DFT技术也将面临新的机遇和挑战。