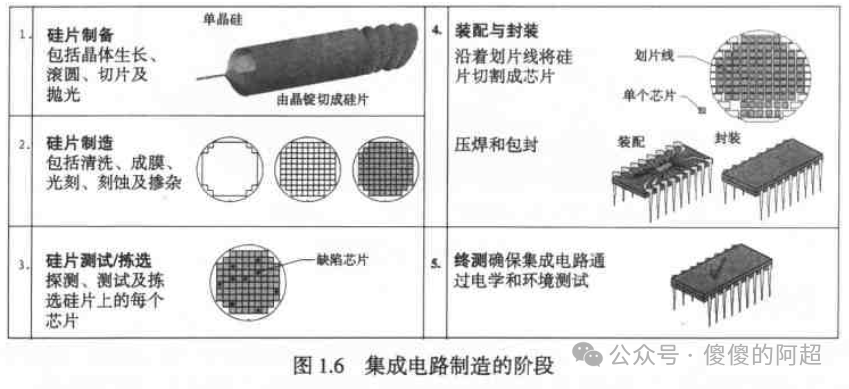

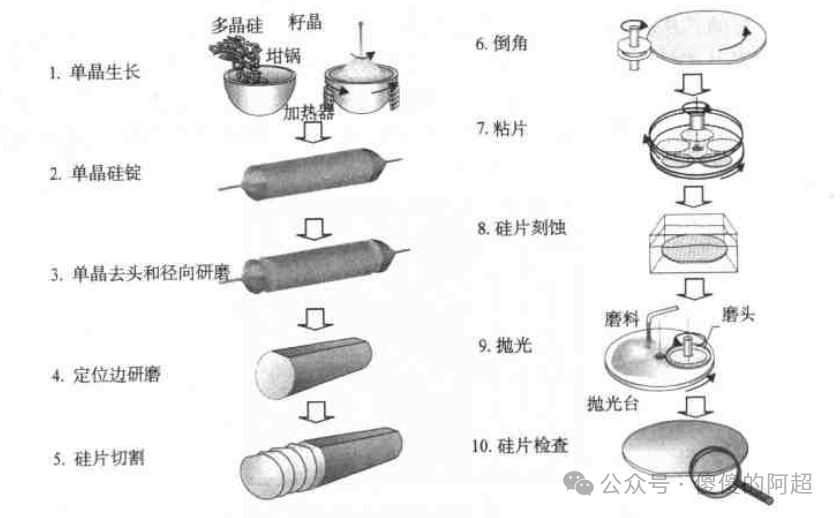

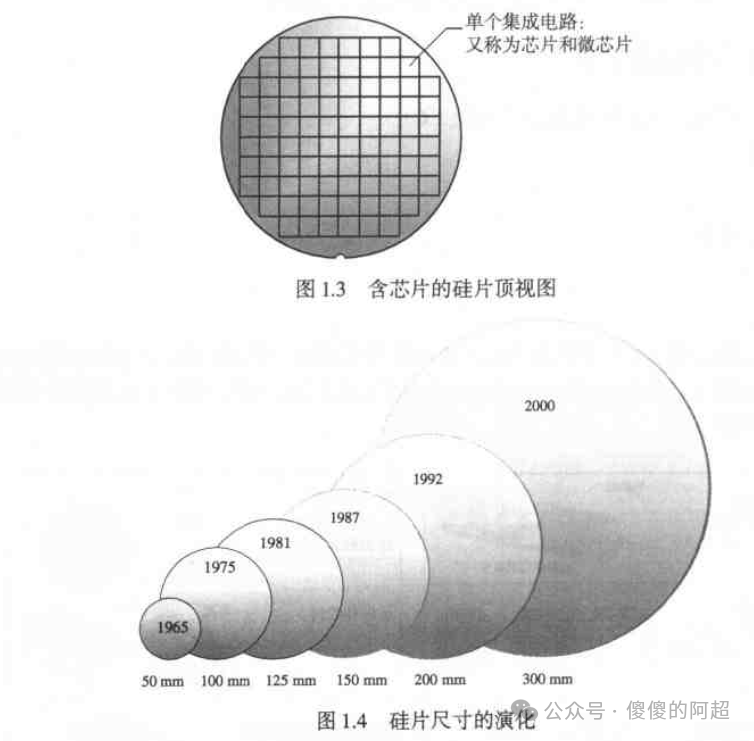

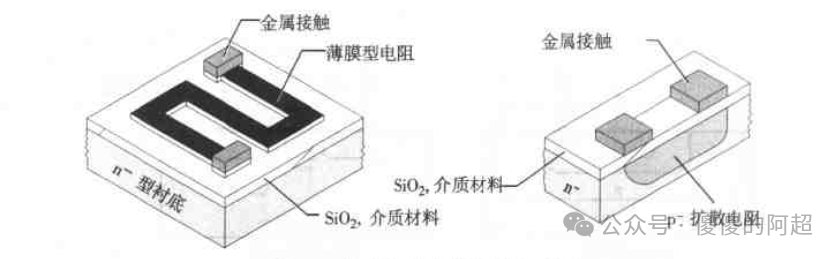

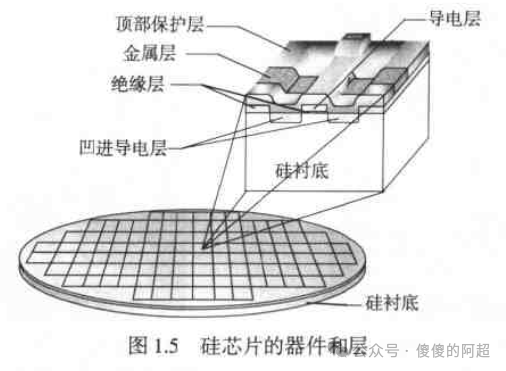

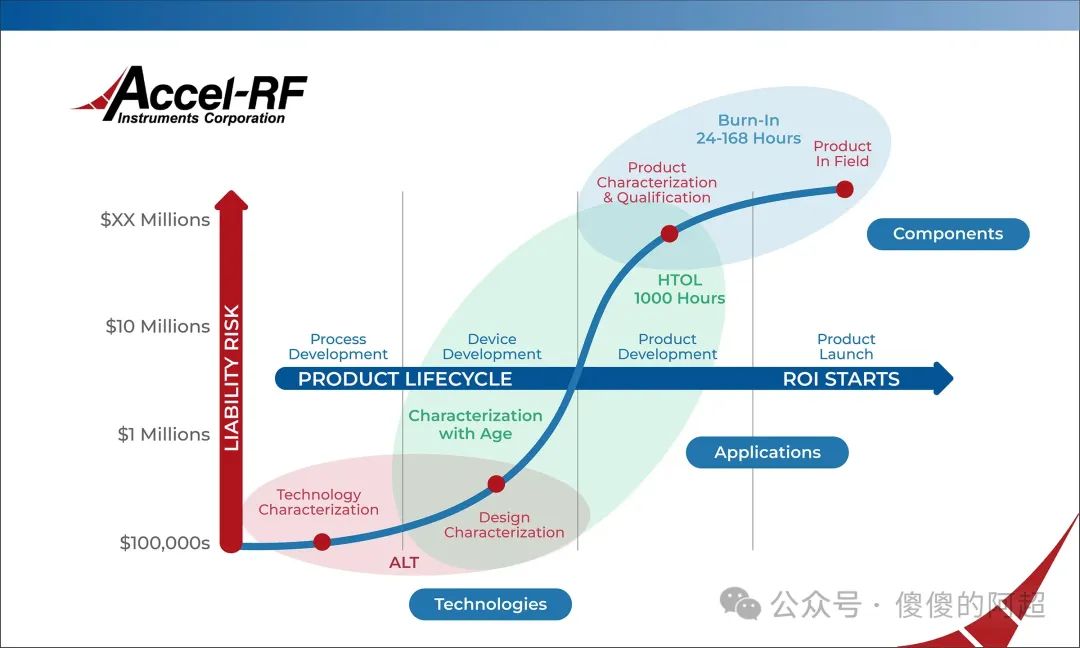

前言:俺木有IC 研发工作经验,工作中有涉及IC失效分析;本文all refer from books and websites, 仅供参考。一、制造过程  1. 硅片制备 - 将硅从沙中提炼并纯化—>经过特殊工艺产生硅锭—>切割为薄硅片。  2. 硅片制造 - 薄硅片 —> 清洗、成膜、光刻、刻蚀、参杂—>集成电路。 可以在一片硅片上同时制作几十甚至上百个特定的芯片 如果在一片硅片上有更多的芯片,制造集成电路的成本会大幅度降低。  二、材料与结构 IC-Integrated Circuit, 又称之为集成电路。电路由什么组成:电源、电阻、电容、电线、二极管、三极管等。那么集成电路就是将各元器件集成到一起实现特定的功能,而在一块硅片上实现此功能,使成本更低、尺寸更小,效率更高。这就形成了IC。 用于微芯片的电子器件是在衬底上构建的,通用的微芯片器件包括电阻、电容、熔丝、二极管和晶体管。 集成电路中的电阻:通过金属膜、参杂的多晶硅或通过杂质扩散到衬底特定区域产生。 电阻和芯片通过与导电金属接触实现连接。  寄生电阻:集成电路元件设计中产生的多余电阻,可积累且会降低电路器件性能。 集成电路中的电容:金属薄层、参杂的多晶硅、衬底扩散区形成。 寄生电容:由于衬底材料自动产生的电容,也会影响电路性能。 有元器件:控制电流方向、放大信号。 半导体器件的制作仅发生在接近硅片表面的几微米。在工艺加工过程中,硅片厚度提供足够的强度。  硅:熔点1412C,硬而脆;量大、高融化温度允许更宽的工艺容限、宽的工作温度范围、表面自然生成二氧化硅充当物理/化学阻挡层。 电子能级 原子级的能量单位是电子伏特(eV)。它代表一个电子从低电势处移动到高出 1V的电势处所获得的动能(与运动相联系的能量)。1电子伏特等于1.6 ×10- 焦能量。电子伏 特用来描述半导体制造不同步骤中的电子能量。 晶体硅缺陷(点缺陷、位错、层错):二氧化硅介质击穿、漏电流。 芯片趋势: · 提高芯片性能(尺寸小、紧密;新材料;提高元件数); · 提高芯片可靠性(设计、制程); · 降低芯片成本; 三、可靠性测试 作为电路系统中最简单、最单纯、最上游的元件之一,芯片在测试时的样品数量和测试时长都远高于module类测试,但由于其生命周期内所受应力种类相对较少(还有各类封装),其测试项目一般较少。  (Image source: https://info.accelrf.com/semiconductor-reliability-testing-guide#a-life-testing) 芯片常见测试项目如下: 1. ALT(Accelerated Life Testing ) 由于其使用时间长,长时间测试以判定其退化性能。施加应力(常规):电(直流电压)、热(温度)、RF(射频)。 2. HTRB(High-Temperature Reverse Bias, 高温反向偏压) · evaluates the long-term stability of devices under high drain-source bias; · intend to accelerate failure mechanisms of the main blocking junction; · stressed close to the maximum rated reverse breakdown voltage with temperatures near the maximum rated junction temperature,; · typically over 1,000 hours; · a static DC bias condition test with no RF component; · During testing, the leakage current is continuously monitored; · The combination of electrical and thermal stress help reveal weaknesses and degradation effects in field depletion structures at the device edges and in the passivation. 3. HTOL(High-Temperature Operating Life) · performed on a representative sample size of devices to validate expected performance; · The goal is not to drive the device to failure as with ALT, but the life is taken out of the part in this stage and it would not be sold into the market; 4. Burn-in · a short-duration stress test; · concerned with screening devices for early life failure; · performed over a large sample size of identical device types, allows the manufacturer to capture a statistically based snapshot of the field performance of the device; · must perform their intended function for an expected period under all possible environments encountered in the field; Others: HAST TC ESD Latch-up IOL(intermittent operating life test), High-Voltage Switching 各试验注意事项: a. 通道温度(channel Temperature):进行加速寿命计算时的基础,确保样品not overstressed;影响温度因素:环境温度、器件热阻、封装和安装材料、功耗等。 b. 工装(Fixturing):测试温度高、在电压或RF下, 芯片放热高,因此工装需保证各测试样品间的独立,防止相互干扰。 c. 多通道支持 d. DC、RF 施加

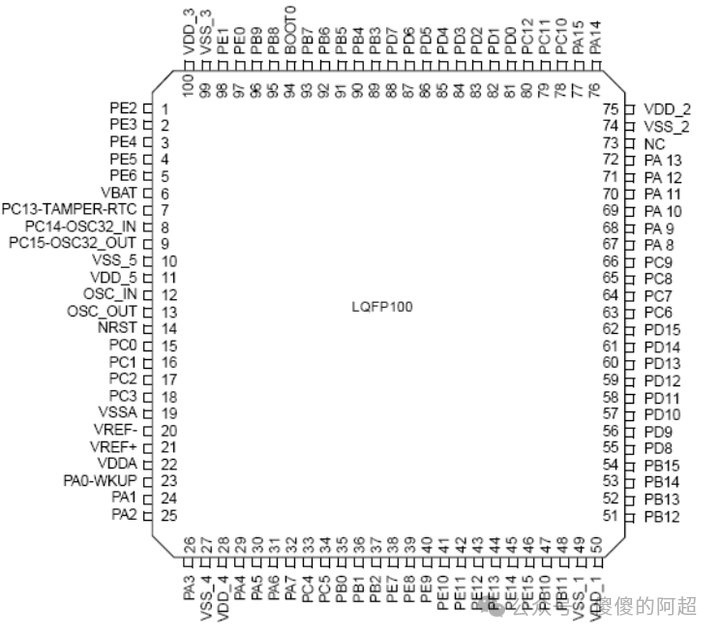

IC测试可参考:JEDEC/IPC/JES/IEEE/AEC 四、失效分析 1. 引脚解释与说明 工作中常看到报告中的VDD,VDD_Main, VSS 等,一时懵逼不知其意。此篇文章(https://zhuanlan.zhihu.com/p/565840030)解释较好。  如上:

2. 常见失效模式 净化间沾污:颗粒(开路、短路)、金属杂质、有机物沾污、自然氧化层、ESD 开路、短路、ESD、参数漂移 3. FA 写作ing,后续再发出来。tools 可参考FA device 各章节 Reference: 1. 半导体制造技术, Michael Quirk & Julian Serda 2. https://info.accelrf.com/semiconductor-reliability-testing-guide#a-life-testing 3. https://www.britannica.com/technology/integrated-circuit/Microprocessor-circuits 4. https://www.ti.com/support-quality/reliability/reliability-testing.html 5. https://en.iclabcn.com/574.html 6. https://zhuanlan.zhihu.com/p/565840030 7. https://www.britannica.com/technology/capacitor 8. https://www.utmel.com/blog/categories/integrated%20circuit/types-structure-and-packages-of-integrated-circuits 9. http://finance.sina.com.cn/wm/2021-06-07/doc-ikqcfnaz9667462.shtml |