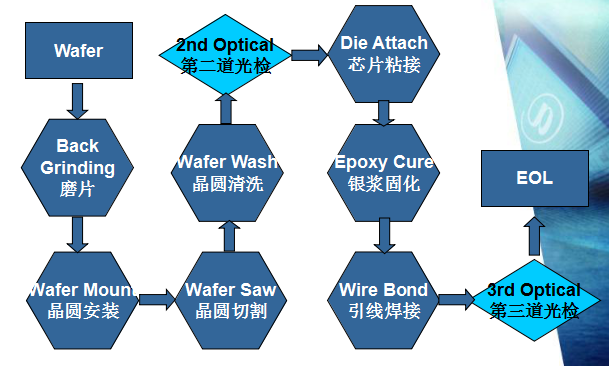

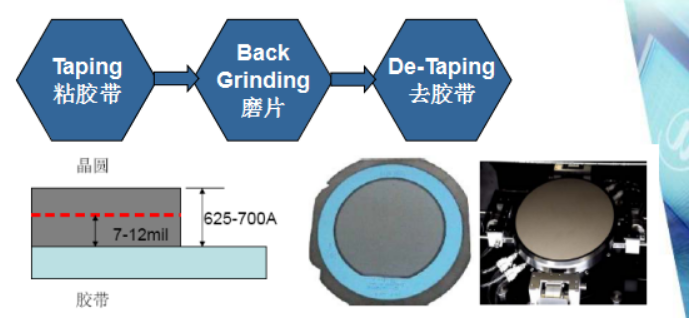

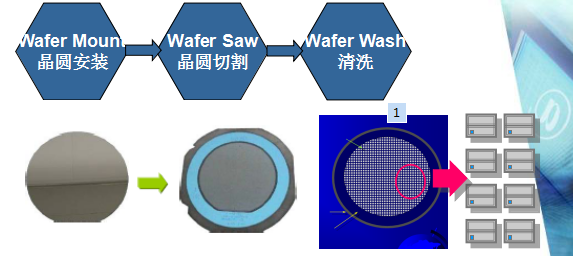

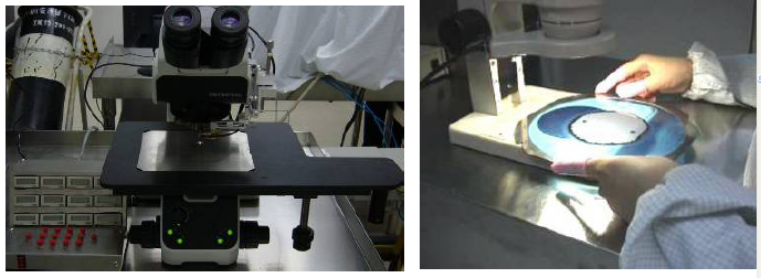

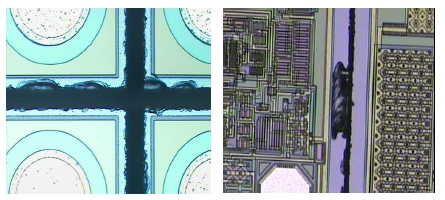

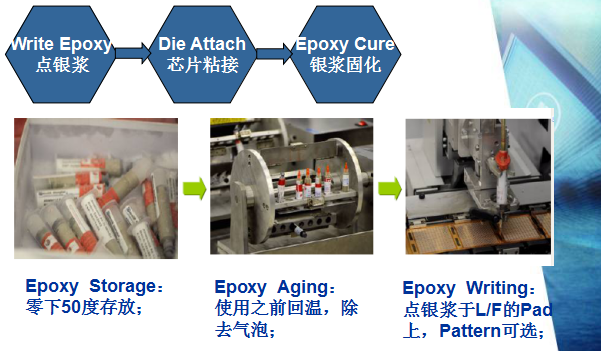

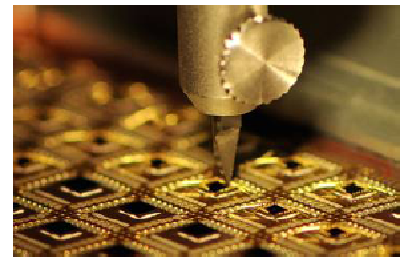

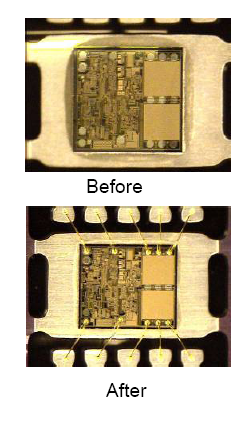

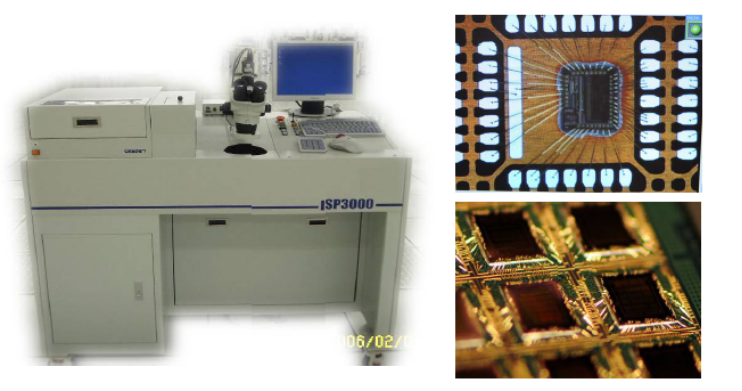

FOL– Front of Line前段工艺  FOL– Back Grinding背面减薄  将从晶圆厂出来的Wafer进行背面研磨,来减薄晶圆达到 封装需要的厚度(8mils~10mils); 磨片时,需要在正面(Active Area)贴胶带保护电路区域 同时研磨背面。研磨之后,去除胶带,测量厚度; FOL– Wafer Saw晶圆切割  将晶圆粘贴在蓝膜(Mylar)上,使得即使被切割开后,不会散落; 通过Saw Blade将整片Wafer切割成一个个独立的Dice,方便后面的 Die Attach等工序; Wafer Wash主要清洗Saw时候产生的各种粉尘,清洁Wafer; FOL– 2nd Optical Inspection二光检查   主要是针对Wafer Saw之后在显微镜下进行Wafer的外观检查,是否有出现废品。 FOL– Die Attach 芯片粘接  芯片拾取过程: 1、Ejector Pin从wafer下方的Mylar顶起芯片,使之便于 脱离蓝膜; 2、Collect/Pick up head从上方吸起芯片,完成从Wafer 到L/F的运输过程; 3、Collect以一定的力将芯片Bond在点有银浆的L/F 的Pad上,具体位置可控; 4、Bond Head Resolution:X-0.2um;Y-0.5um;Z-1.25um; 5、Bond Head Speed:1.3m/s; FOL– Epoxy Cure 银浆固化  银浆固化: 175°C,1个小时; N2环境,防止氧化:  Die Attach质量检查: Die Shear(芯片剪切力) FOL– Wire Bonding 引线焊接   利用高纯度的金线(Au) 、铜线(Cu)或铝线(Al)把 Pad 和 Lead通过焊接的方法连接起来。Pad是芯片上电路的外接 点,Lead是 Lead Frame上的 连接点。 W/B是封装工艺中最为关键的一部工艺。 FOL– 3rd Optical Inspection三光检查  |