|

IDDQ测试在大规模集成电路测试中尤为重要,本文将详细阐述IDDQ测试原理,测试方法。

IDDQ TUTORIAL

Goals:

To show how a quiescent current supply test, Iddq, contributes to ICdefect isolation.

To understand the challenges of the Iddq measurement.

To select from the available Iddq test methods, the ones which mostpractically reduce test time.

To Identify and validate circuit defect using failures analysistechniques and relate Iddq anomalies to the circuit flaw cause.

Objectives:

List the circuit requirements and test conditions for Iddq and describehow Iddq limit is derived.Write the advantages and disadvantages of the three main categoriesof electrical tests DC, Function Iddq and AC in isolating defects.List the order of defect types and their related symptoms and the characteristics of a valid Iddq failure.

Topics:

Iddq Concepts

Defects and Faults

Iddq Test Pattern Generation

Testing Methods

Failure Analysis

Review Questions

Iddq Concepts

13.0Introduction

CMOS IC makers were frustrated, because, oddly, some parts which were successfully tested failed to function in the field, while some other parts suffered performance degradation.

Two peculiarities were common to these escape (bad) parts:

(1) Iddq is several order of magnitude higher than the normal expected residual value of less than 1uA.

(2) Iddq value varies with the applied pattern between normal to abnormal.

A circuit defect, such as a short or partial transistor saturation, was suspected since CMOS is a nanowatt logic. See the example below for explanation of such case where a defective device eludes screening.

13.1 Example

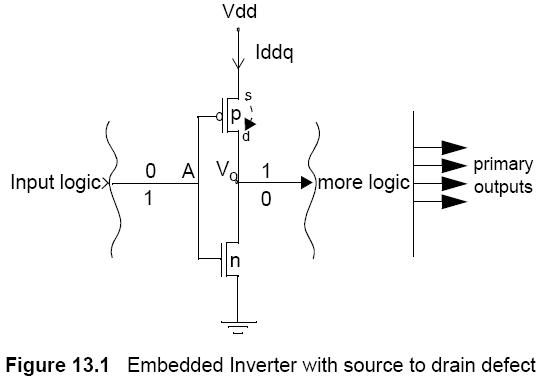

An embedded inverter is shown in Figure 13.1 in which the source and drain of the p-FET are shorted.

Ans (1): When an input logic 0 pattern is applied at A, the n-FET is turned off and the voltage appearing at the output correspond to logic

1. The value of Iddq is residual despite the existence of the short.

However, when an input logic 1 pattern is applied, the n-FET is turned on elevating Iddq.

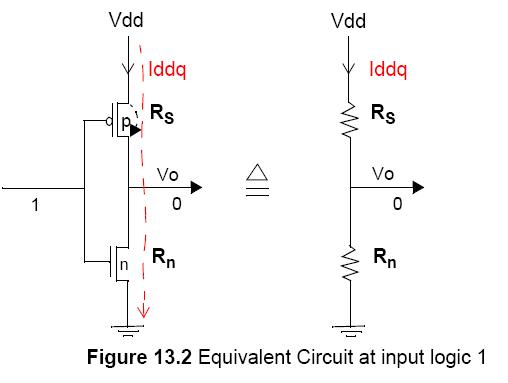

Ans (2): Assume that the short is resistive. The equivalent circuit of the elevated Iddq is the voltage divider shown in Figure 13.2.

Rs is the short resistance and Rn is the output ON resistance of then-FET.

By assuming that Rs/Rn is greater than 3, Vo turns to be logically correct for the subsequent gate. Although weak, this logic level allows function test to pass. Flaws due to one type of defects called bridging have impedances that could easily meet the previous assumption of Rs/Rn > 3.

If Iddq was monitored during logic 1 application, that defect would have been found. There would be no need to propagate and validate, as in conventional function, any signal at the primary outputs.

13.2 What is Iddq Testable?

To be able to use this powerful, and at first glance simple, detection method some requisites are needed namely:

The device circuitry must be CMOS.

The magnitude of background current from voltage dividers, embedded RAMs, pull-up or pull-down resistors, etc., must not be high enough to swamp the minuscule Iddq measurement.

The voltage applied to any part of the circuit must not partially turn on the p or the n-FETs. Refer to the CMOS Transfer Characteristics.

The part is rested from all external as well as internal transients at time of measurement.

13.3 The Advantages of Iddq

Diagnosing defects using Iddq offers several advantages because:

Iddq is a cost-effective test method indispensable to identify some defects which are indiscernible by the conventional functional tests.

The applied pattern needs only sensitize the node. This offers an immense computational reduction (1:7) over the conventional function test in pattern generation.

It has been proven that the number of Iddq measurements required to reach a fault coverage greater than 90% is relatively small (2 digits).

Iddq performs, to some extent, the job of burn-in by isolating those devices which will not survive in the field; the walking-wounded ones.

Iddq enhances quality, shortens time-to-market and provides an efficient SPMC (Statistical Process Monitor and Control) for yield enhancement.

The types of potential problems detected by Iddq include:

Process flaws: bridging, deformed traces, mask problems, incomplete etching, logically redundant defects.

Design flaws: Floating gates, logic contention, mask generation errors.

13.4 Why doesn’t Iddq replace Function?

Iddq is intended to complement and not replace function for several reasons:

Neither conventional function nor Iddq alone detects 100% of the defects.

The Iddq timing is not set to run at the max specified frequency all the times due to test method constrains.

The voltages and currents requirements Vil/Vih, Iol/Ioh, Vdd are different in conventional function than those in Iddq.

13.5 What Iddq does not detect

Iddq does not detect any defect which does not lead to an appreciable increase in the supply current such as:

Highly resistive interconnects and open defects which do not elevate Iddq.

Defects which inhibit the transistor from being conductive.

Transmission gate defects which lead to weak logic.

Dynamic interconnects such as capacitive and inductive coupling.

有兴趣者可下载后仔细研读: IDDQ测试解析

|