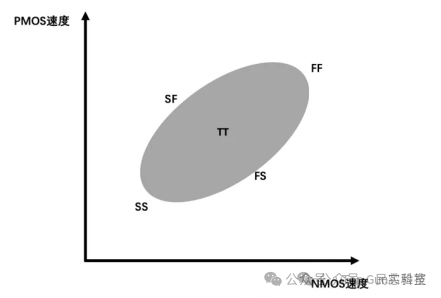

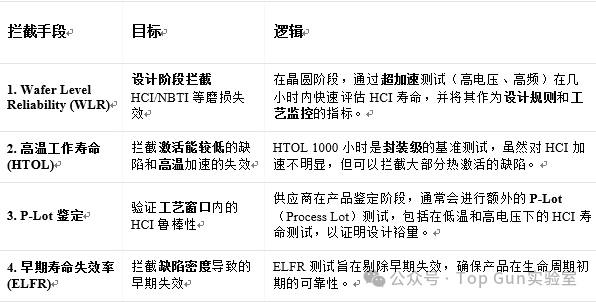

在半导体可靠性验证中,关于AEC-Q100的一些常见疑问,为什么抽样不要求Corner片?为什么是3个Lot而非Corner片? Corner片(Process Corner)的局限性 Corner片(快片FF、慢片SS、快慢片FS/SF、典型片TT等)是集成电路设计和验证阶段常用的概念。它们代表了工艺参数(如沟道长度、氧化层厚度、阈值电压等)的极端组合,用于验证设计的功能鲁棒性和性能边界。 然而,Corner片在可靠性鉴定中存在局限性: o 非代表性:Corner片代表的是工艺窗口的边缘,在实际量产中出现的概率极低。它们并不能代表量产批次的整体质量水平和工艺波动。 o 侧重性能而非缺陷:Corner片主要关注性能(速度、功耗),而可靠性测试关注的是缺陷密度和磨损失效。可靠性缺陷(如颗粒污染、封装空洞)的分布与工艺参数的Corner状态并无直接关联。 3个Lot的统计学意义(工艺波动) AEC-Q100强制要求使用来自3个不同Lot的样本进行可靠性鉴定,其核心逻辑在于:3个Lot旨在覆盖时间维度和工艺波动带来的缺陷密度和质量一致性差异。 o 统计学保障:如上一篇文章所述,3个Lot各77个样本(共231个)的零失效结果,可以在90%置信度下将批次允许的不良率(LTPD)降至1%左右。这是对量产批次质量的统计学承诺。 o 工艺稳定性:要求3个Lot必须来自不同时间、不同晶圆或不同封装批次,以确保工艺流程的长期稳定性和可重复性。如果某个Lot因工艺参数漂移导致可靠性下降,将无法通过鉴定。 结论:Corner片验证设计鲁棒性,而3个Lot验证量产质量一致性和统计可靠性。 测试项目为什么没有LTOL?如何拦截HCI失效? LTOL(低温工作寿命)与HCI失效:HCI(Hot Carrier Injection,热载流子注入)是一种典型的磨损失效机制,主要发生在MOS晶体管的栅氧化层界面。 o 失效机理:高电场和高电流密度导致载流子获得高能量,注入到栅氧化层,造成阈值电压漂移和跨导下降。 o 低温加速效应:HCI失效在低温下通常表现出加速效应。这是因为低温下载流子的平均自由程增加,更容易获得足够能量成为“热载流子”。因此,LTOL(Low Temperature Operating Life,低温工作寿命)是拦截HCI失效的理想测试。 AEC-Q100不强制LTOL的原因与替代方案 AEC-Q100的确没有将LTOL列为强制性的封装级鉴定测试项目。这并非意味着忽略HCI,而是通过更高效、更具针对性的手段进行拦截:  核心逻辑: o HCI是设计问题:HCI寿命主要取决于器件设计(如栅氧化层厚度、沟道长度)和工艺参数。一旦设计和工艺确定,HCI寿命相对稳定。 o WLR更高效:在晶圆级进行HCI寿命测试(WLR)比在封装级进行LTOL 1000小时测试效率更高、成本更低,且能更早地发现设计或工艺问题。 o 因此,车规认证将HCI的拦截主要放在设计阶段的WLR验证和量产阶段的工艺监控中,而不是依赖于耗时且昂贵的封装级LTOL鉴定测试。 思考: 当Design House不完全使用Fab厂提供的标准库(Standard Cell Library),而是采用定制器件(Custom Devices)、模拟/混合信号电路或特殊版图(Layout)时,Fab厂通用的WLR数据确实无法完全覆盖这些特定设计的HCI风险。 在这种情况下,拦截HCI风险的逻辑会从“依赖Fab”转向“设计公司自主管控”。那么Design House如何通过可靠性工程手段来来接定制器件的HCI风险呢?我们在下一篇文章中进行探索。 |