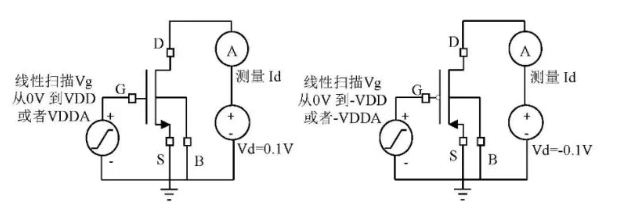

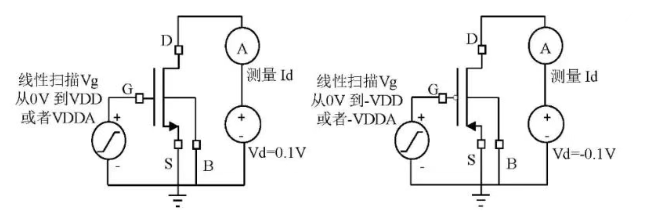

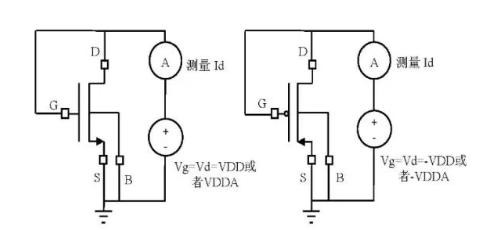

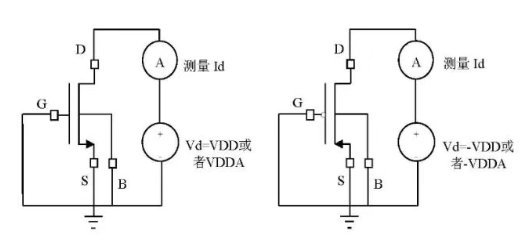

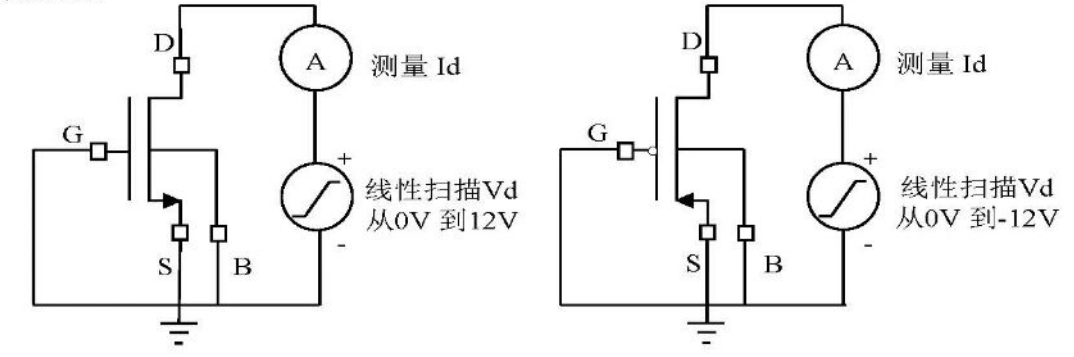

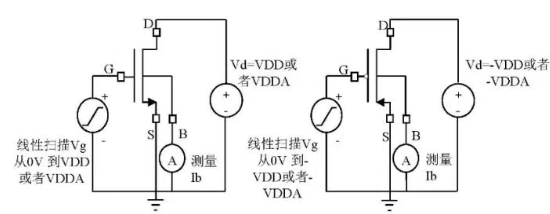

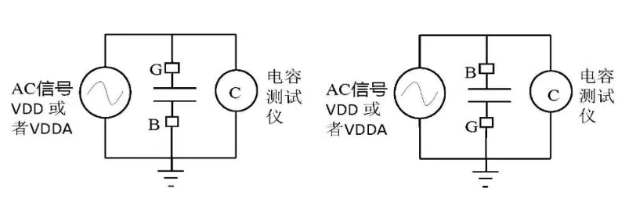

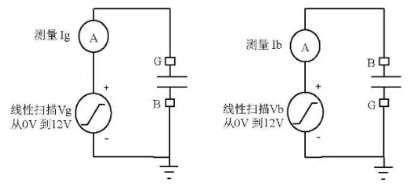

MOS参数1. 阈值电压Vt第一种测试方法是最大电导测量,也是线性外推法:a. 对于NMOS,首先设定Vd=0.1V和Vb=Vs=0V,然后线性扫描Vg从0V到VDD或者VDDA(VDD为低压器件的最大工作电压,VDDA为中压器件的最大工作电压。),测得最大电导时Vg的值,求该点的斜率,通过该点利用斜率作斜线相交于x轴得到数值Vg(x),那么Vt=Vg(x)-0.5Vd。 b. 对于PMOS,首先设定Vd=-0.1V和Vb=Vs=0V,然后线性扫描Vg从0V到-VDD或者-VDDA,测得最大电导时Vg的值,求该点的斜率,通过该点利用斜率作斜线相交于x轴得到数值Vg(x),那么Vt=Vg(x)0.5Vd 。  第二种方法是利用电流常数测阈值电压: a. 对于NMOS,首先设定Vd=0.1V和Vs=Vb=0V,然后线性扫描Vg从OV到VDD或者VDDA,测得Vg在I/W=0.1uA/um时的值,那么Vt=Vg。 b. 对于PMOS,首先设定Vd=-0.1V和Vs=Vb=0V,然后线性扫描Vg从OV到-VDD或者-VDDA,测得Vg在I/W=0.1uA/um时的值,那么Vt=Vg.  阈值电压的影响因素: a. 阱离子注入异常:这个在inline中一般没有监控参数; b.离子注入损伤在退火过程中没有激活:这个在inline中一般没有监控参数; c.AA或多品硅栅刻蚀后的尺寸异常:这个主要关注AA AEI CD POLY CD以及MG等相关参数; d.栅氧化层的厚度异常导致:这个关注DG相关的工艺参数; e. 对于NMOS,关注SMT loop 相关工艺参数;PMOS,应该还要关注SiGe loop相关工艺参数。 2.饱和电流Isat 这个目的在于测试MOS工作在饱和区,也就是刚刚沟道发生夹断的电流大小。 a. NMOS饱和电流Idsat,设定Vd=Vg=VDD或者VDDA,Vs=Vb=0V,测量电流Id,那么Idsat=Id/W; b. PMOS饱和电流Idsat,设定Vd=Vg=-VDD或者-VDDA,Vs=Vb=0V,测量电流Id,那么Idsat=Id/W.  饱和电流的影响因素: a. 阱离子注入异常导致; b. N+或者P+离子注入异常; c. LDD离子注入异常; d. 离子注入损伤在退火过程中没有激活; e. AA或多晶硅栅刻蚀后的尺寸异常; f. 栅氧化层的厚度异常; g. 对于NMOS,关注SMT loop 相关工艺参数;PMOS,应该还要关注SiGe loop相关工艺参数。 3.漏电流Ioff 测试在MOS管没有开启时,沟道中通过电流 a. NMOS漏电流Ioff,首先设定Vd=1.1VDD或者1.1VDDA,Vg=Vs=Vb=0V,测量电流Id,那么Ioff-=Id/W; b. PMOS漏电流Ioff,首先设定Vd=-1.1VDD或者-1.1VDDA,Vg=Vs=Vb=0V,测量电流Id,那么Ioff-=Id/W.  漏电流的影响因素: a. 阱离子注入异常; b. LDD离子注入异常; c. AA刻蚀损伤在退火过程中没有消除, d. 接触孔刻蚀异常。 4. 击穿电压BVD测试 测试在截止区时,源漏之间电流突然增大,一般达到微安量级时的电压。 a. NMOS击穿电压BVD,首先设定Vg=Vs=Vb=0V,然后线性扫描Vd, 从0V到12V,得到Vd在Id/W=0.1uA/um时的值,该点的电压值就是击穿申压BVD; b. PMOS击穿电压BVD,首先设定Vg=Vs=Vb=0V,然后线性扫描Vd, 从0V到-12V,得到Vd在Id/W=0.1uA/um时的值,该点的电压值就是击穿申压BVD。  击穿电压的影响因素: a. 阱离子注入异常; b. LDD离子注入异常; c. 离子注入损伤在退火过程中没有激活: d. 多品硅栅刻蚀后的尺寸异常; e. 接触孔刻蚀异常。 5. 衬底电流Isub测试 在理想的MOSFET模型中,我们认为栅极控制沟道,而源、漏和衬底之间是绝对绝缘的。但在实际工作中,特别是当晶体管处于饱和区时,会有一个非零的电流从沟道流入衬底。这个电流就是衬底电流。它对电路的主要危害是引起可靠性退化(热载流子效应)、逻辑错误和功耗增加。 a. 测量NMOS衬底电流,首先设定Vd=VDD或者VDDA,Vs=Vb=0V,然后线性扫描Vg从0V到VDD或者VDDA,测得最大衬底电流,那么Isub=Ib/W; b. 测量PMOS衬底电流.,首先设定Vd=VDD或者VDDA,Vs=Vb=0V,然后线性扫描Vg从0V到-VDD或者-VDDA,测得最大衬底电流,那么Isub=Ib/W。  衬底电流的影响因素: a. 阱离子注入异常; b. LDD离子注入异常; c. 离子注入损伤在退火过程中没有激活. 栅氧化层参数1.栅氧电容Cgoxa. 测量NMOS栅氧化层电容Cox,首先在栅电容的一端多品硅栅上加载AC100KHz(VDD或者VDDA)扫描电压,另一端PW衬底接地,来测试电容C,Cox=C/Area。 b. 测量PMOS栅氧化层电容Cox。,首先在栅电容的一端NW衬底上加载AC100KHz(VDD或者VDDA)扫描电压,另一端栅极接地,来测试电容C,Cox=C/Area。  栅氧电容影响因素: a. 阱离子注入异常; b. 离子注入损伤在退火过程中没有激活; c. 栅氧化层的厚度异常:这个厚度主要和DG工艺相关。 2.电容击穿电压BVgox a. 测量NMOS栅氧化层击穿电压BVgox,首先在栅电容的一端栅上加载DC扫描电压,Vg从0V到12V,另一端PW衬底接地,测试电流Ig,得到Vg在Ig/Area=100pA/um2时的值,BVgox=Vg,就是击穿电压。 b. 测量PMOS栅氧化层击穿电压BVgox,首先在栅电容的一端衬底上加载DC扫描电压,Vb从0V到12V,另一端栅接地测试电流Ib,得到Vb在Ib/Area=100pA/um2时的值,BVgox=Vb就是击穿电压。  影响电容BVgox的因素与影响电容Cox |