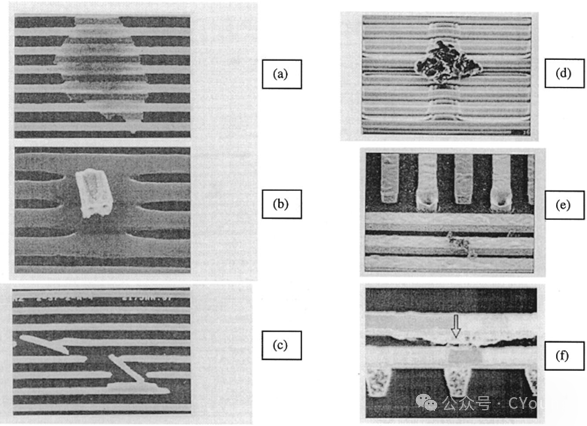

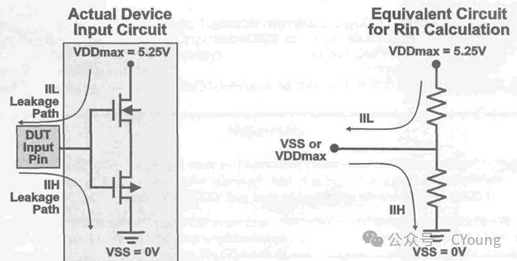

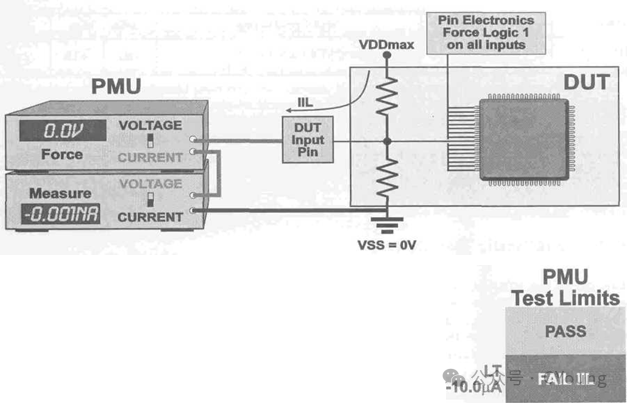

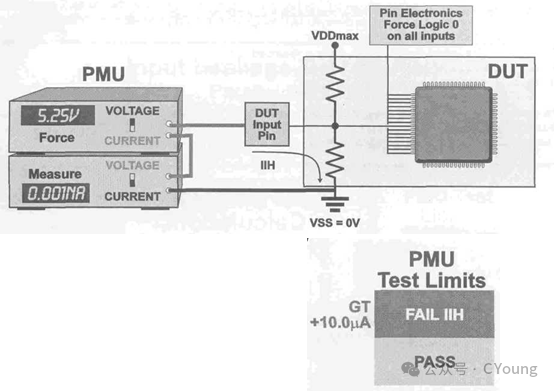

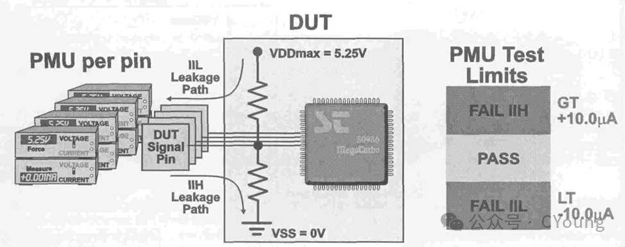

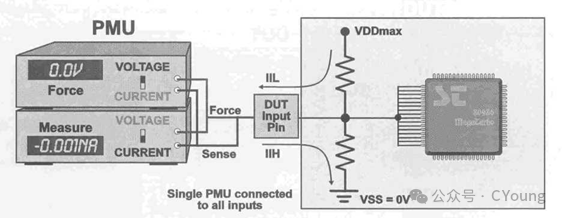

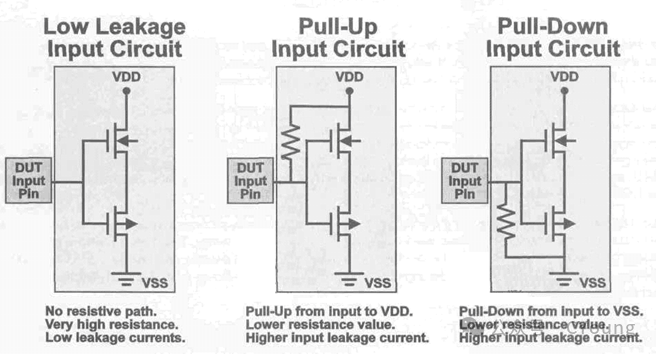

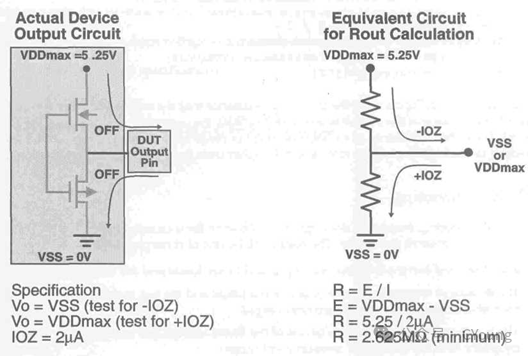

这是我的第六十五篇原创文章嗯哼,关于上一篇写了IC测试最基础的开短路测试(Open/short, OS),发现有许多朋友对IC测试感兴趣的。其实吧,芯片产业也是这几年的风口。水涨船高,IC测试开发本来是个相对较为偏门的岗位,也越来越推到台前倍关注。 看过之前文章的朋友们都知道,其实呢,我在芯片设计公司工作,并非在华天,长电这样的测封厂。我本职工作还是做嵌入式软件,偏向底层驱动和框架,就是和 IC 设计部门配合比较多,然后就多委派我做了ATE相关的编码工作。我从了解到入这行其实也就这这半年不到时间,我发现关注上篇文章的朋友挺多,还有不少是入行好几年的ICTer前辈,若有不妥之处,还请各位前辈们指正。 那么今天咱们继续写写关于IC测试相关的东西,漏电测试(leakage Test),在我的理解里,他主要的功能还是和OS一样,都属于IC本身的结构型基础测试。 01 在IC设计中,我们理想的情况是芯片的输入引脚或那些有三态输出的引脚,对电源和地的电阻非常大。也就是说,当我们给这些引脚施加上电压时,流入或流出的电流应该要非常小,甚至小到忽略不计,但是这只存在于理想状态下。流入流出哲这些IO的这种小电流被称为漏电流。 随着制造工艺的进步,芯片内部和引脚之间的绝缘膜变得越来越薄,这就导致了漏电流的发生概率增加。此外,在制造过程中, 如果出现了工艺缺陷,比如电路桥接、异物污染,或者在封装过程中出现芯片划伤、裂纹等问题,也会导致漏电流增大。  在实际的测试中,有些产品可能会表现出漏电流较大,但它们的功能仍然正常。这类产品虽然看起来没有问题,但它们存在潜在的可靠性风险。因此,我们进行漏电流测试的目的是为了筛选出那些可能存在缺陷的产品,避免它们流入市场,防止对终端产品造成更大的损失。 除了完整性的测试意义,还有就是确保IC的低功耗的功率。在咱们IC正常工作中,漏电流越小,电路的静态功耗就越低,特别是在低功耗IC的设计中非常的重要。 综上咱们知道其实漏电测试(Leakage Test)也是属于芯片本身的结构型测试的一种,所以一般情况下,咱们漏电测试会放在OS测试之后进行,因为这样可以尽早的发现IO结构问题,为之后的function的功能测试做准备。 02 咱们的漏电测试一般包括输入漏电测试(IIL&IIH)和输出高阻态漏电测试(IOZL&IOZH)。 输入漏电流的测试方法比较简单,其实就是对测引脚施加额定的电压,然后测试其流入或流出的电流是否符合咱们相应的设计规范。 IIL 是IC输入引脚被强驱低电平(L)时的电流(I)泄漏情况。 IIH是IC输入引脚被强驱高电平(H)时的电流(I)泄漏情况。  综上,咱们知道,IIL/IIH 实际上就是加压测流(FVMI)。 IIL 测试的具体步骤如下: · 首先将 VDDMAX 施加到DUT的电源,以确保IC在电压最大值状态下工作; · 将所有无关输入引脚设置为逻辑 1(VIH = VDDMAX); · 使用 PMU 驱动测试引脚为逻辑 0(VIL = 0); · 等待几个微妙时间,测量流过测试引脚的电流,并设置相应的limit阈值,并与 IIL 限值进行比较; · 对所有输入引脚重复此测试;  同理,测试 IIH 测试的具体步骤如下: · 首先将 VDDMAX 施加到DUT的电源端,以确保IC在电压最大值状态下工作; · 将所有无关输入引脚设置为逻辑 0(VIL = 0); · 使用 PMU 驱动测试引脚为逻辑 1(VIH = VDDMAX); · 等待几个微秒时间,测量流过每个引脚的电流,并与 IIH 限值进行比较; · 对所有输入引脚重复此测试;  02 上面测试方法是通过串行来进行测试,相当于只能一个一个IO的来进行测试。但是在某些测试系统中,可以用并行测试。并行漏电测量涉及利用多个 PMU 同时测量多个引脚上的电流。所有输入引脚都被强制为高电平状态,并用并行测量每个引脚上的电流。随后,将测试结果与设计值进行比较以得出结论。  具体测试流程为: · 首先,为DUT提供VDDmax的电源。 · 使用多个 PMU 强制每个输入引脚在 VDDmax 时处于高电平状态(用于 IIH 测量)。 · 等待1到5微秒,检测电流,并根据比较得出结论 · 然后,将引脚拉至 VSS 并重复上述步骤进行 IIL 测量。 这种测试方法的优势在于可以快速执行 IIL/IIH 测试,同时还能测量每个引脚的单独漏电流数值。 然而,这种方法的缺点就是难以检测输入IO之间的漏电流。 我们在实际的测试中,用这种的方式比较多。比如使用 IO 漏电测试的3380P 的测试程序如下: io_leakage_test() { DATALOG_MSG="io_leakage_test"; TEST_NO(200); //IO Leakge test FORCE_V_MLDPS(DVDD18_33_SEN ,3.45V,@6V,@1A,1A, NORM, ON,3mS); // 0V FORCE_V_PPMU(RPD_PINS,0.0V,,@20uA,,1mS); JUDGE_I_PPMU(RPD_PINS,-5uA,1uA,1mS,100, AVE,50uS,,); // 3.45V FORCE_V_PPMU(RPD_PINS ,3.45V,,@20uA,,1mS); JUDGE_I_PPMU(RPD_PINS - MIPI_PINS,-1uA,5uA,1mS,100, AVE,50uS,,); JUDGE_I_PPMU(MIPI_PINS ,-2uA,5uA,1mS,100, AVE,50uS,,); FORCE_V_PPMU(RPD_PINS,0.0V,,@2mA,,1mS); POWER_DOWN_FAIL_SITE_X(); } 03 除了上面两种测试方法外,还有一种测试法,叫联合测试。所谓的联合测试实际上就是将所有输入引脚组合成一个引脚,并使用单个 PMU 测量总漏电流。测试概念如下所示:  联合测试的电流限制设置为设备规格中单个引脚的值。这种测试适用于高阻抗CMOS输入,对于有上拉/下拉电阻的输入不适用,因为漏电流总和可能超过单引脚限制。 联合测试漏电流的优点是可以快速执行,并且不需要每个引脚的 PMU 电路。缺点是该方法只能用于测试具有非常高阻抗的输入,每个引脚的单独电流测量未知,并且每次发生故障时必须使用串行测试方法重新执行测试,还有对硬件设计有一定的要求,得考虑是否会影响之后功能测试。 04 最后在咱们IC设计中,某些IO可能具有固定上拉或者下拉结构,其漏电流表现会有所差异,这一点可能需要通过项目设计人员来确定,电路输入引脚一般有如下三种结构:  输入引脚到电源端和接地端没有上拉/下拉电阻,引脚对电源和地为高阻状态,此时输入高电平漏电流和输入低电平漏电流都很小,通常为正负几个微安或更小。 输入引脚与电源端之间存在上拉结构,对地为高阻状态,此时输入高电平电流表现与无上下拉电阻无差异。但输入低电平时,由于电源端与输入引脚存在电压差和电阻通路,其电流测试值会明显偏大,通常为几十到几百微安。其电流方向为从被测器件流向测试机,结果为负值。 输入引脚与地端之间存在上拉电阻结构,对电源端为高阻状态,此时输入低平漏电流的表现与无上下拉电阻时无差异。但输高低电平时,由于输入引脚与地存在电压差和电阻通路,其电流测试值会明显偏大,通常为几十到几百微安。其电流方向为从测试机流向被测器件,结果为正值。 05 最后咱们再说一下输出高阻测试(IOZL & IOZH),和之前的输入不同,这个是输出高阻测试。一般MCU 的 IO 默认状态是浮空输入,不符合咱们的浮空输出测试方案,所以往往这种方案得配合 Pattern 向量来改变内部状态进行测试,这里咱们不考虑这种,只考虑默认就是浮空输出的状态。 高阻态也是浮空状态,也叫三态,表示 DUT 引脚外部呈现高阻抗。一般高阻都用在通讯协议的IO上,比如咱们常见的I2C,SPI等协议,高阻输出的高电平都是由于外部的上拉电阻决定,这个上拉电阻,是可以决定通讯协议的速率的上限。 IOZL是指当输出处于高阻状态(Z)施加低电压(L)时,从输出(O)流出的电流(I)。IOZH 是指当输出处于高阻状态(Z)并施加高电压(H)时,从输出(O)流出的电流(I)。 IOZL 测量引脚在高阻状态下对 VDD 的电阻,而 IOZH 测量对 VSS 的电阻。  测试流程如下: · 首先,为设备提供 VDD 电源。 · 将设备的引脚设置为输出高阻状态,并使用 PMU 强制将引脚拉高/拉低。 · 测量针脚上的电流。低于 -IOZ (-2µA):失败 高于 +IOZ (+2µA):失败 · 其他范围:通过 串行测试的优点是能够精确测量单个引脚的电流,但速度较慢。此外,这种测试需要设置钳位电流。 关于并行测试方法涉及在多个引脚上同时使用多个 PMU。这里就不重复说明了,还是之前类似的操作。 06 好了,这篇漏电测试就讲这么多,说了一大堆,实际上漏电测试原理还是加压测流,是不是没有想象中的复杂。 看了看上篇文章讲OS的,发现咱们入这行的人也不少,下方也有不少老鸟给小萌新提的不少建议。我想要不我牵头拉个群,为入坑前辈和想要入坑的朋友一个沟通的平台。我觉得这个挺有意义的,毕竟学习是个痛苦的过程,一个人学习更是。当然我也入行没多久,也可以学习学习,利人利己嘛,我也会把我学习资料和对应的书籍翻译放群里,供有兴趣的朋友下载学习。 |