|

1、什么是SPI? 高速、全双工、同步的通信总线。通信简单 数据传输速率块

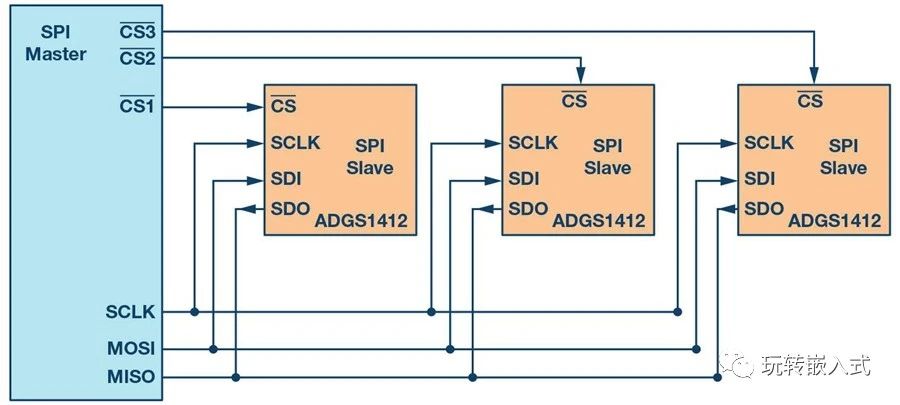

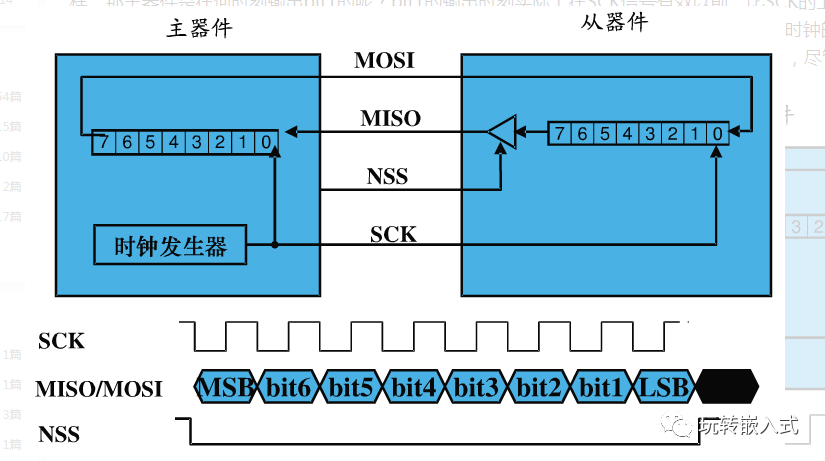

(2):主从机通信模式 三线制和四线制之分。信号线包括SDI(串行数据输入 Serial Digital IN)、SDO(串行数据输出 Serial Digital OUT)、SCLK(时钟)、CS(片选)。SDO/MOSI – 主设备数据输出,从设备数据输入SDI/MISO – 主设备数据输入,从设备数据输出SCLK – 时钟信号,由主设备产生;CS/SS – 从设备使能信号,由主设备控制。当有多个从设备的时候,因为每个从设备上都有一个片选引脚接入到主设备机中,当主设备和某个从设备通信时将需要将从设备对应的片选引脚电平拉低(一般低有效)。

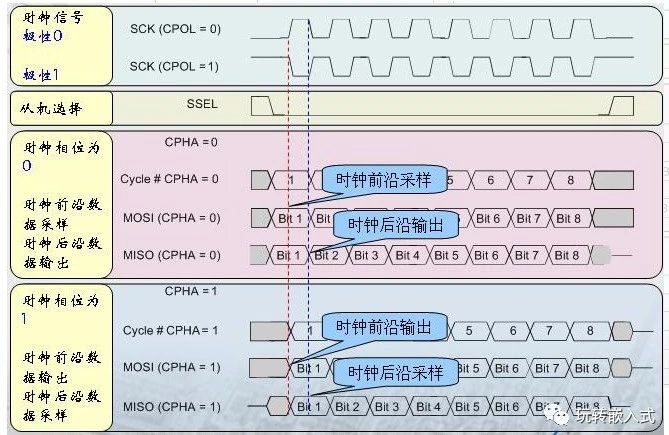

CPOL(时钟极性)和CPHA(时钟相位)来控制主设备的通信模式。:CPOL=0,CPHA=0 Mode1:CPOL=0,CPHA=1 Mode2:CPOL=1,CPHA=0 Mode3:CPOL=1,CPHA=1

CPOL是用来配置SCLK电平的有效态的;时钟相位 CPHA是用来配置数据采样是发生在第几个边沿的。CPOL=0表示当SCLK=0时处于空闲态,所以SCLK处于高电平时有效;CPOL=1表示当SCLK=1时处于空闲态,所以SCLK处于低电平时有效;CPHA=0表示数据采样是在第1个边沿,数据发送在第2个边沿;CPHA=1表示数据采样是在第2个边沿,数据发送在第1个边沿;CPOL=0,CPHA=0:此时空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。CPOL=0,CPHA=1:此时空闲态时,SCLK处于低电平,数据发送是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。CPOL=1,CPHA=0:此时空闲态时,SCLK处于高电平,数据采集是在第1个边沿,也就是SCLK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。CPOL=1,CPHA=1:此时空闲态时,SCLK处于高电平,数据发送是在第1个边沿,也就是SCLK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。

|