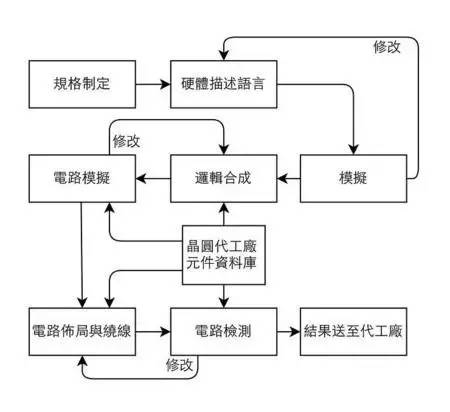

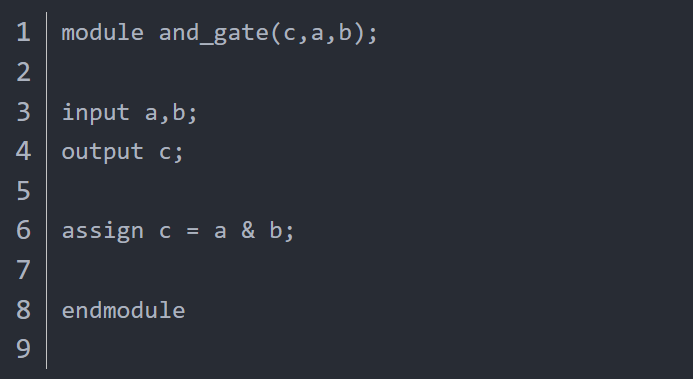

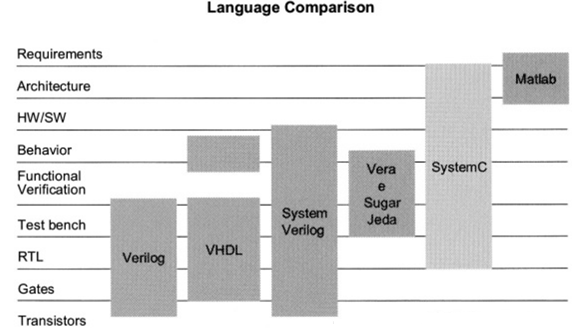

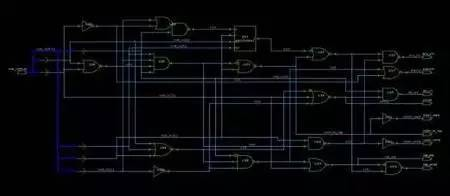

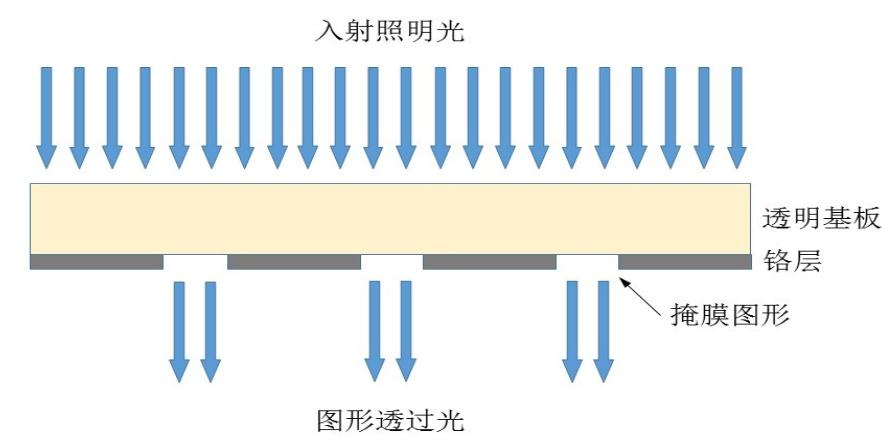

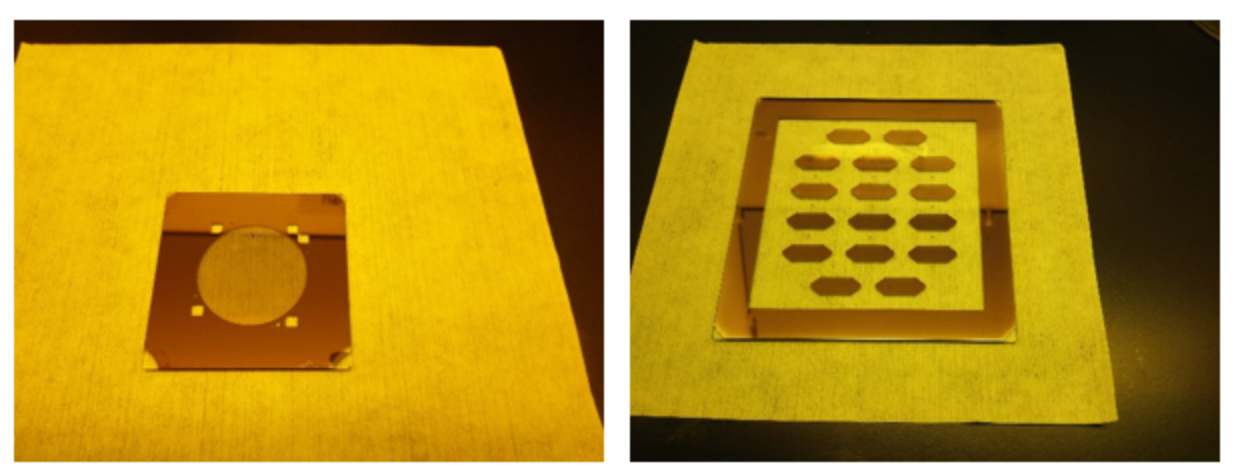

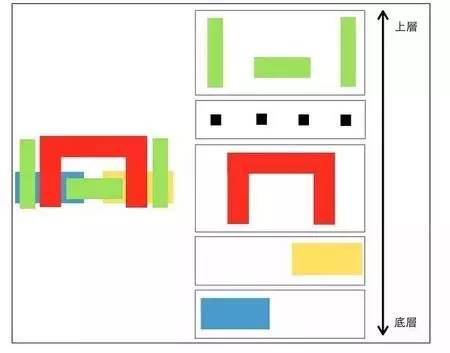

梳理完晶圆制造和芯片封装测试两大环节,系列文章还剩下最后芯片设计这最重要的一部分。近几年芯片设计相关岗位一直以高薪资、高门槛著称,一般对从业人员的研发技术能力要求比较高,目前多为相关专业的优秀硕士乃至博士学历者且有相当丰富的行业经验。下面笔者作为门外汉将从数字IC设计流程、模拟IC设计流程、EDA工具与IP核、掩模版四个方面浅浅地将自己了解或者学习到的分享给大家,权当班门弄斧。一、数字IC设计流程 芯片设计主要分为模拟IC设计和数字IC设计。首先以数字IC为例展开介绍下。  数字IC设计流程:1.规格制定→ 2.逻辑设计 → 3.功能仿真 → 4.逻辑综合 → 5.形式验证 → 6.静态时序分析 → 7.可测性设计 → 8.物理设计 → 9.寄生参数提取和信号完整性分析 → 10.静态时序分析 → 11.物理验证 → 12.版图交付。 其中2~7属于前端流程,9~12为后端流程。下面各个步骤作简要分享。 第1步:规格制定(Specification) 在 IC 设计中,最重要的步骤就是规格制定,需要根据需求制定芯片的功能和性能指标,完成设计规格文档。 第2步:逻辑设计(Logic Design) 逻辑设计是指基于HDL(硬件描述语言)在RTL(Register-Transfer Level)级实现逻辑设计,并通过逻辑验证或者形式验证等验证功能正确。常使用的HDL有Verilog、System Verilog、VHDL 等。  用Verilog描述与门 上图显示了Verilog描述与门的一种形式。作为常用的一种硬件描述语言,Verilog可以从五个层次对电路(系统)进行描述,包括:系统级、算法级、寄存器传输级(即RTL级)、门级、开关级。我们平时用得最多的为RTL级,故Verilog代码也经常被称为RTL代码。 HDL用于开发RTL非常合适,但由于开发难度大、故障率高、运行速度慢、与软件语言兼容性差,使其用于抽象程度更高的建模例如行为级建模、软硬件建模、架构级建模等就显得难堪大任。这时就需要专门的系统建模语言能够支持对复杂并行系统的模拟,SystemC正是为此而生,为软硬件系统建模提供了强有力的支持。  引用自《SystemC: From the Groud Up》 第3步:功能仿真 即前仿真,默认为理想状态,不会有timing的问题,主要验证模块逻辑功能的正确性,所以又叫功能仿真。编译跑仿真的EDA工具有VCS,Qustasim等,debug的工具一般是Verdi。接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。 第4步:逻辑综合(Logic Synthesis) 指将RTL转换成特定目标的门级网表(netlist),并优化网表延时、面积和功耗。  控制单元合成后的结果 第5步:形式验证(静态验证) 使用Synopsys的Formality工具对电路功能进行检查,比对RTL和Netlist的功能是否一致。 第6步:静态时序分析(Static Timing Analysis,STA) 使用Synopsys的PT(Prime Time)工具对电路时序进行检查。STA满足时序约束,得到最终的Netlist。 第7步:DFT(design for test)可测性设计 随着集成电路规模的增大,制造出来的芯片是否有问题越来越难以被测试,因此有了可测试性设计。通过插入扫描链(scan chain)和BIST等方式,方便生产的芯片进行测试。使用EDA工具为DFT compiler。 第8步:物理设计(Physical Design) 指将门级网表根据约束布局、布线并最终生成版图的过程,其中又包含:数据导入 → 布局规划 → 单元布局 → 时钟树综合 → 布线。 第9步:寄生参数提取和信号完整性分析 由于导线本身存在的电阻,相邻导线之间的互感,耦合电容在芯片内部会产生信号噪声,串扰和反射,产生信号完整性问题,因此提取寄生参数进行分析验证是十分必要的。 第10步:静态时序分析(Static Timing Analysis,STA) 此时电路每个单元位置,各项参数都已确定,再做静态时序分析是最准确的。 第11步:物理验证(Physical Verificaiton) 通常包括版图设计规则检查(DRC),版图原理图一致性检查(LVS)和电气规则检查(ERC)等。 第12步:版图交付(Tape Out) 在所有检查和验证都正确无误的前提下,传递GDSⅡ格式的版图文件给代工厂生成掩膜图形,并生产芯片。 二、模拟IC设计流程 模拟IC的设计流程中,芯片定义、版图交付和数字电路相同,但是电路设计、版图设计、版图验证和数字电路有所不同。对于模拟芯片设计而言,设计时是不能够用Verilog代码来描述功能的,这也是模拟设计与数字IC设计最大的区别。 模拟IC设计流程:1.规格制定 → 2.电路设计 → 3.SPICE仿真 →4. 版图设计 → 5.版图验证 → 6.后仿真 → 7.版图交付。 第1步:规格制定(Specification) 第2步:电路设计 根据系统需求,设计晶体管级的模拟电路结构。常用的电路图编辑工具有Cadence Virtuoso – Schamatic Composer。 第3步:SPICE仿真 编辑完成后常用Synopsys HSPICE或Cadence Spectre进行电路模拟验证电路的功能和性能,俗称SPICE仿真。 第4步:版图设计 按照设计规则,绘制电路图对应的版图几何图形,并仿真版图的功能和性能。常用的工具是Cadence Virtuoso – Layout Editor(LE)。 注:这里的版图不是电路图,而是交给芯片制造厂用于制作掩膜版的设计图纸。 第5步:版图验证 DRC:DRC保证版图满足芯片制造厂的设计规则; LVS:证明版图与网表的一致性; NE:版图的电路提取; ERC:电学规则检查; PEX:寄生参数提取; 常用的DRC/LVS EDA工具:Mentor Calibre、 Synopsys Hercules; 第6步:后仿真 根据提取的寄生参数,再用软件验证一下,能否实现想要的功能和性能。在以上的过程中发现错误都需要反复地修改。 第7步:版图交付 生成GDSⅡ文件,交给芯片制造厂流片。 三、EDA工具与IP核 完成芯片设计除了设计人员的构思和规划,一般最为需要的还有EDA工具以及现有的IP资源,他们是巨人的肩膀。 其中EDA(Electronic Design Automation)电子设计自动化,常指代用于电子设计的软件,可以看到前文提到的RTL仿真与综合、IC版图设计、验证等重要的设计环节都是基于对应的EDA平台展开的。目前Synopsys、Cadence和Mentor(Siemens EDA)占据着超过90%以上的EDA市场份额,在10纳米以下的高端芯片设计上其占有率甚至高达100%。IP(Intelligent Property)代表着知识产权的意思,在业界是指一种事先定义、经过验证的、可以重复使用,能完成特定功能的模块。IP核可以分为硬核、固核和软核,是构成大规模集成电路的基础单元,SoC甚至可以说是基于IP核的复用技术。目前这一领域大部分市场份额亦被欧美占据,市场前三依次是Arm、Synopsys、Cadence。 四、关于掩模版 最后还有一个比较关键的问题,那就是芯片设计与制造在哪个节点以及如何结合起来的? 版图交付为芯片设计最后的节点,最终生成的GDSⅡ文件会给到晶圆厂用来制作光刻掩膜版(Photomask,又称光罩)。它是微电子、集成光电子制造中光刻工艺所使用的图形母版,由不透明的遮光薄膜在透明基板上形成掩膜图形,并通过曝光将图形转印到晶圆上。其工作原理和实物图片如下。  掩模版工作原理  掩模版实物(图片取自中国科学技术大学维纳研究与制造中心官网) 一般来说IC的版图文件中会有多个图层,上下层的分别对应着各自的任务。一块掩膜版对应其中某一个图层上的图形。下图中,左边就是经过电路布局与绕线后形成的电路图,每种颜色便代表一张个图层或者掩模版。右边则是将每个图层摊开的样子。  IC图层展开 由底层开始逐层制作掩模版并嵌入晶圆制作的流程(光刻阶段)中,最后便会产生期望的成品晶圆和芯片。 关于掩模版的工艺流程,参考中国科学技术大学维纳研究与制造中心的掩模制版过程(光刻掩膜版设计与加工指南 (ustc.edu.cn)): 1)绘制生成设备可以识别的掩膜版版图文件(GDS格式) 2)使用无掩模光刻机读取版图文件,对带胶的空白掩膜版进行非接触式曝光(曝光波长405nm),照射掩膜版上所需图形区域,使该区域的光刻胶(通常为正胶)发生光化学反应。 3)经过显影、定影后,曝光区域的光刻胶溶解脱落,暴露出下面的铬层 4)使用铬刻蚀液进行湿法刻蚀,将暴露出的铬层刻蚀掉形成透光区域,而受光刻胶保护的铬层不会被刻蚀,形成不透光区域。这样便在掩膜版上形成透光率不同的平面图形结构。 5)在有必要的情况下,使用湿法或干法方式去除掩膜版上的光刻胶层,并对掩膜版进行清洗。 |