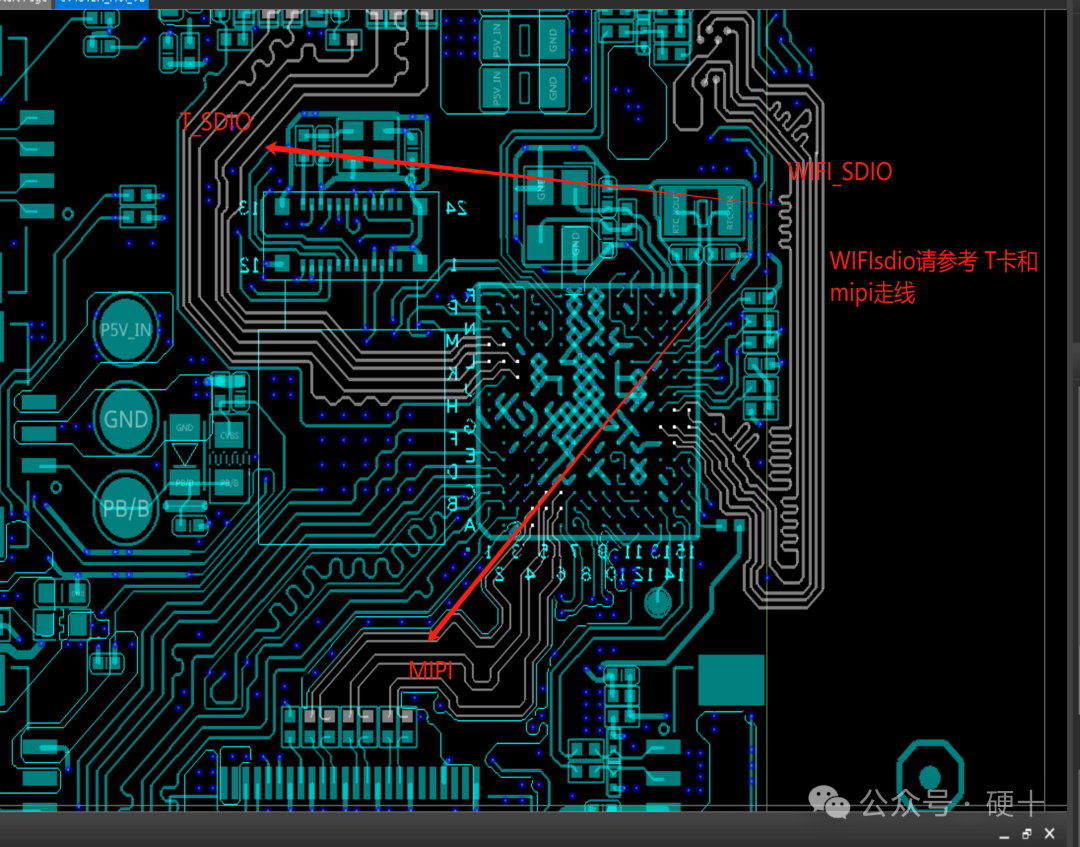

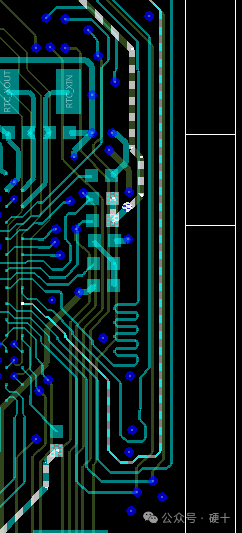

在PCB设计中,工程师们往往对高速信号的完整性保持高度警惕,却容易忽视低速信号走线的阻抗控制问题。当相邻走线间距呈现不规则变化时,即便信号速率不高,仍然会引发意想不到的信号质量问题。这种间距变化带来的阻抗扰动,远比单纯考虑串扰问题更值得关注。一些速率虽然不算特别高,但是对时序、信号质量有要求的数字接口,例如“SDIO”。我要注意走线间距的问题。  如果走线可以间距足够的大,例如满足3W,并且可以用GND隔离,并且足够的空间打GND地孔,那么也没什么纠结的。但是往往我们没有那么多足够的空间来走线。这时候,我们需要判断让两根线的间距增大一些。但是不要盲目铺GND 为什么不要随便在高速线旁边铺铜? 那么,我们就像知道,此时50Mbps的信号,或者100Mbps的信号走线是否会干扰相邻信号。  我们实际场景中,只能做到2W,是否有串扰问题呢?  空间受限时的妥协方案若PCB空间不足,可采取以下平衡策略:1. 优先级分级 : CLK信号 :必须满足4W间距或地线隔离。 CMD信号 :次优先级,≥3W间距。 DAT0-DAT3 :组内等长优先,组间允许局部放宽至2.5W(需SI验证)。 2. 局部密度调整 : 非关键信号(如CD检测)可缩小间距至2W。 3. 牺牲布线层 : 将SDIO信号单独布置在一层,避免与其他高速信号(如DDR、USB)平行。 比“串扰”危害更大的是“阻抗变化” 如果我们做不到3W,把间距缩小为2W,除了串扰问题,还有什么问题呢? 当 PCB 走线间距无法满足 3W 规则(即线中心距为 3 倍线宽),而只能采用 2W 时,会对信号完整性和 EMI 产生显著影响,具体问题及对策如下: 1. 串扰增加 间距从 3W 减至 2W 时,相邻信号线间的电场耦合增强,串扰噪声可能增加 30%~50%(差分对更敏感)。 高频信号(如 PCIe Gen4 以上)的近端串扰(NEXT)可能超出规范要求,导致误码率上升。 2. 阻抗偏差 差分对间距缩小会降低差分阻抗(典型值下降约 5~10Ω),若设计容差为 ±10%,可能超出允许范围。 单端线与参考平面的间距变化也会影响单端阻抗,导致反射增加。 3. EMI 辐射增大 紧密间距会增加共模电流辐射,尤其是当差分对不平衡时,EMI 可能超出 FCC/CE 认证限值。 虽然100MHz以下的信号对2W间距的相邻走线串扰影响是有限的,但是会影响阻抗,间距的变化会导致阻抗变化,从而引起反射,导致信号质量变差。我们还是把2W优化为2.5W。  |