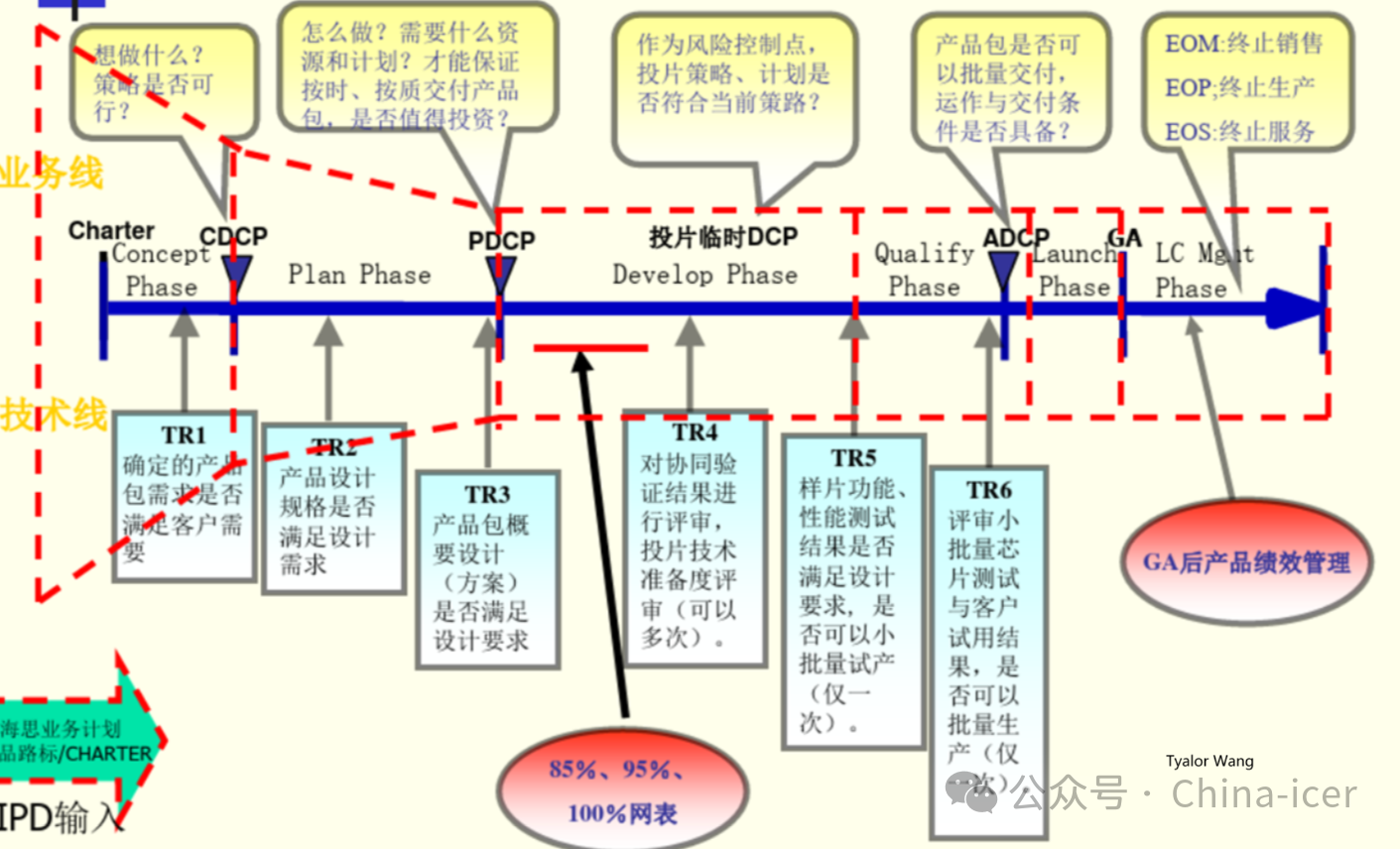

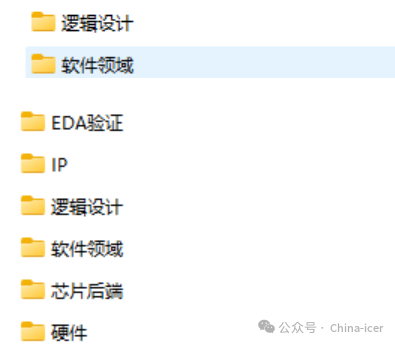

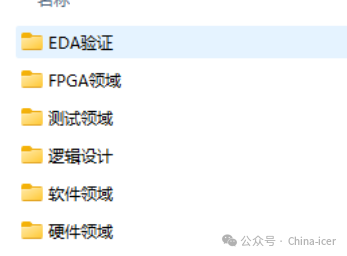

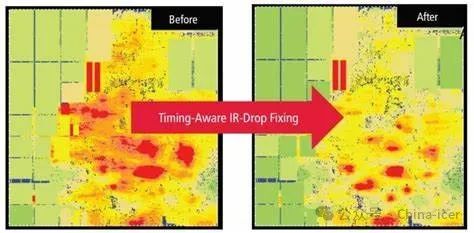

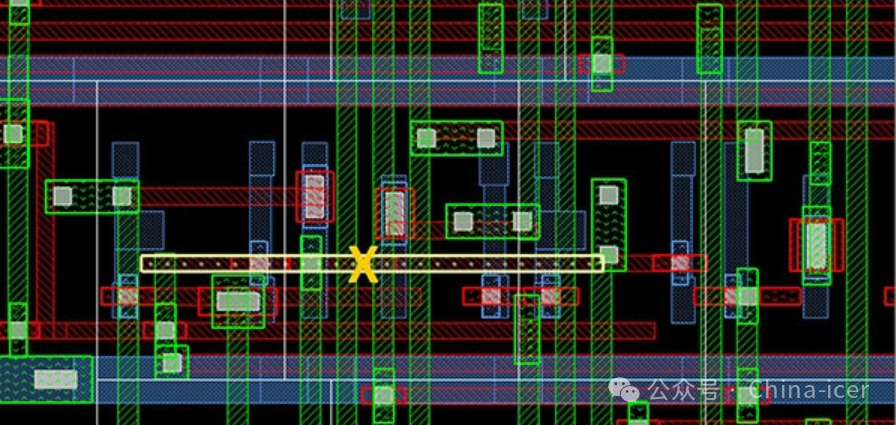

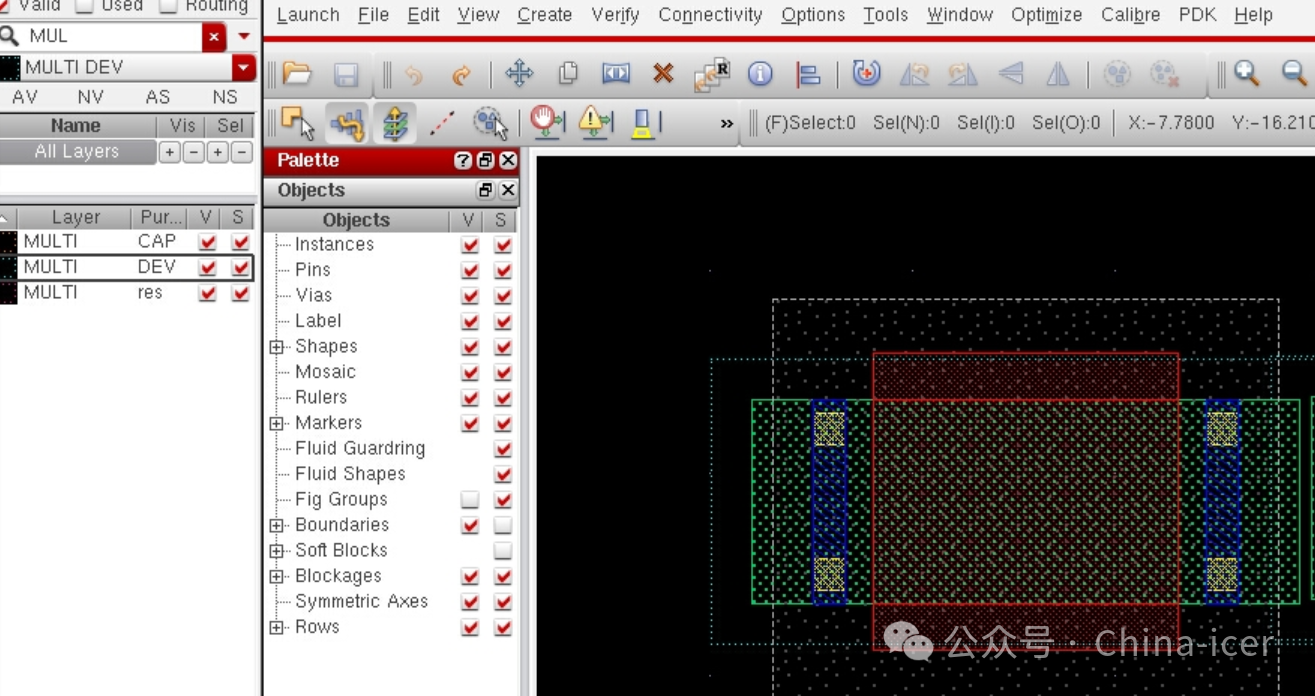

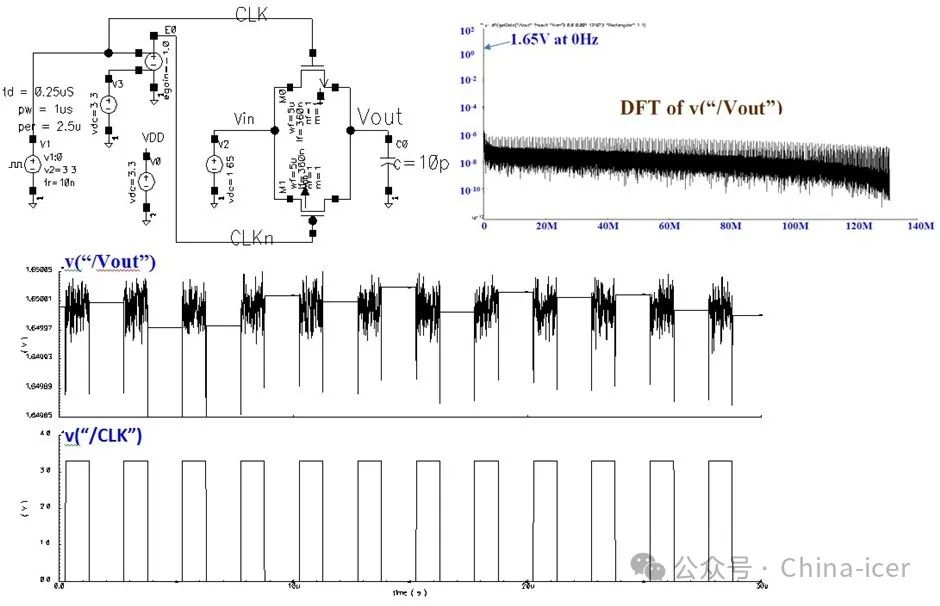

Part A:答疑分享半导体芯片研发项目的技术复杂性是很高的软硬一体的项目, 而且涉及多个部门分工协作, 根据我的20年做芯片的经验,重风控、平衡风险收益、重多方决策、重流程、重质量的项目, 才是一个优秀的项目。 总结2个共性问题, 希望知道 Signoff的节点和TR的节点 1、 TR的原则, 参考海思的流程, 如下图。每个TR点都很重要,  如何保证每个TR点的验证是充分,有效和符合的呢? 就需要 一系列的 2 3 4级文件支撑。 这才是海思IPD文件的关键, 但是并不一定 100%适合所有的公司,需要理解,吸收, 裁剪,落地、应用,匹配、试点、应用。所有部门从职责界定、资源提供到检查改进方方面面的个例芯片的要求、公司的资源投入和需求, 如下图,笔者公司之前TR1/2的文件目录:   二, 芯片Signoff 只有当这些检查全部通过,芯片才有可能成功流片。这些检查一部分可由工具自动完成,而另一部分则需要我们将工具无法自动执行的检查项整理成清单,逐一核对。 芯片 Tapeout 前的 sign off 工作是一个复杂而严谨的过程,涵盖了多个方面的检查和优化;只有全面、细致地完成这些 signoff 工作,才能提高芯片流片成功的概率,确保芯片的质量和性能 常见的Signoff IR Signoff 包括静态 IR 分析(Static IR Analysis)和动态 IR 分析(Dynamic IR Analysis)。通过这些分析,确保芯片在工作时电源网络上的电压降(IR Drop)在合理范围内,避免因电压降过大导致芯片性能下降或功能错误。  Power Switch Cell 和 Isolation Cell 检查 对 Power Switch Cell 和 Isolation Cell 进行检查,保证电源开关单元和隔离单元的正常工作,以实现芯片不同模块间电源的有效管理和隔离 Timing Signoff 必须确保所有 corner(如典型工艺角、最坏情况工艺角等)下的 setup 和 hold 时序都满足要求,没有任何违例。这需要对时钟路径、数据路径等进行精确的分析和调整。 2. DRC Check 进行设计规则检查(DRC Check),涵盖基本设计规则(Base DR)、金属层相关规则(Metal D)等。确保芯片版图的物理布局符合制造工艺的要求,如线宽、间距、通孔尺寸等规则,避免因物理设计违规导致芯片制造失败  Antenna Check 进行天线效应检查(Antenna Ched),防止在芯片制造过程中因天线效应导致晶体管栅氧化层被击穿,影响芯片的可靠性。 LVS Check 进行版图与原理图一致性检查(LVS Check),保证版图实现与原理图设计的一致性,确保芯片的电气连接和功能与设计意图相符。  Noise Analysis 进行噪声分析(Noise Analysis),考虑芯片工作时各种噪声源对信号的影响,如电源噪声、串扰噪声等,确保信号在噪声环境下仍能正确传输和处理。  Crosstalk Analysis 进行串扰分析(Crosstalk Analysis),分析相邻信号之间的串扰情况,避免因串扰导致信号失真或错误触发。 顺序没有通用性,大家熟悉每个点的作用,可以根据各家芯片而定 FM signoff/Net freeze signoff Power Signoff Low Power Signoff IR Drop Signoff SI/PI/PV Drop signoff CLR signoff signoff DRC/LVS signoff DRM Signoff |