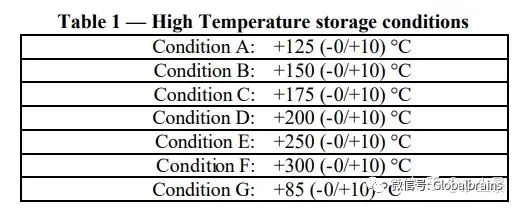

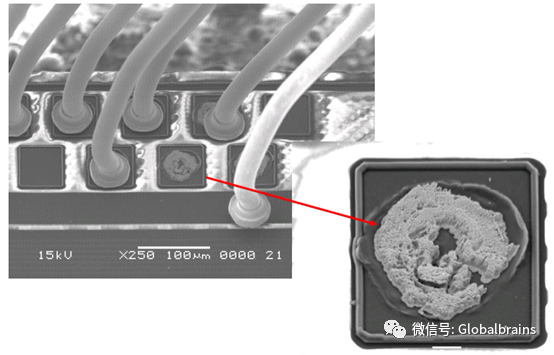

HTSL:High Temperature Storage Life参考标准:JESD22-A103C 1 Scope The test is applicable for evaluation, screening, monitoring, and/or qualification of all solid state devices. High Temperature storage test is typically used to determine the effect of time and temperature, under storage conditions, for thermally activated failure mechanisms of solid state electronic devices, including nonvolatile memory devices (data retention failure mechanisms). During the test elevated temperatures (accelerated test conditions) are used without electrical stress applied. This test may be destructive, depending on Time, Temperature and Packaging (if any). HTSL测试用来测试在存储环境下,时间和温度对芯片的影响,这个测试用来激发芯片的热失效,包括非挥发性存储器件。在这个测试过程中,芯片测试是不需要加电的。这个测试可能是破坏性的,取决于时间,温度和封装。  2 Apparatus 2.1 High temperature storage chambers The apparatus required for this test shall consist of a controlled temperature chamber capable of maintaining the specified temperature over the entire sample population under test. 这个测试需要一个能够时刻监控温度的chamber。 2.2 Electrical test equipment Electrical equipment capable of performing the appropriate measurements for the devices being tested, including write and verify the required data retention pattern(s) for nonvolatile memories. HTSL测试后需要进行电学测试,电学测试的设备要可对芯片进行擦写和验证数据保持的pattern功能。 3 Procedure 3.1 High temperature storage conditions The Devices under test shall be subjected to continuous storage at one of the Temperature Conditions of Table 1 HTSL测试过程中,chamber的温度需要保持在一个特定的温度下。  NOTE CAUTION should be exercised when selecting an accelerated test condition since the accelerated temperature used may exceed the capabilities of the device and materials, thereby inducing failures (overstress) failures that would not occur under normal use conditions. 选择测试条件的时候,要注意测试的条件要根据芯片和封装材料的特征来选择。因为如果选择的条件不合适,很可能在测试条件下失效,但是在正常使用下会没有问题。 As a minimum the following items should be taken into consideration: 1) Melting point of metals present, especially solder. Degradation of metals includes metallurgical interfaces. 金属的熔点要考虑进去,往往在金属和化合物结合的面上会出现恶化。 2) Package degradation. For example Glass Transition Temperature and thermal stability (in air) of any polymeric materials. 封装恶化:例如,玻璃的转化温度和化合物材料的热稳定性。 3) Moisture rating of package (per J-STD-020). 封装的湿敏等级 4) Temperature limitations of silicon devices. For example: Charge loss in Nonvolatile memories. 芯片的热限制,例如:NVM芯片的电荷损失 The Qualification and Reliability monitoring test conditions have typically duration of 1000 hours per condition B of Table 1 (JESD 47). Other conditions and durations may be used as appropriate. The devices may be returned to room ambient conditions for interim electrical measurements. 芯片在测试过程中可以在常温下安排电学测试 3.2 Measurements Unless otherwise specified, interim and final electrical test measurements shall be completed within 96 hours after removal of the devices from the specified test conditions. Intermediate measurements are optional unless otherwise specified. 除非有特殊限制,临时测试和最后的final测试应该在移出测试环境的96H小时内完成电学测试 The electrical test measurements shall consist of parametric and functional tests specified in the applicable procurement document. For nonvolatile memories, the data specified data retention pattern must be written initially, and then subsequently verified without re-writing. 电学测试应该包括parametric测试和功能测试。对于NVM芯片,数据保持的pattern应该在测试前写入到芯片中,HTSL测试完成后再确认数据是否正确。 3.3 Failure criteria A device will be considered a High Temperature Storage failure if parametric limits are exceeded, or if functionality cannot be demonstrated under nominal and worst-case conditions, as specified in the applicable procurement document. For nonvolatile memories, the specified data retention pattern shall be verified before and after storage. A margin test may be used to detect data retention degradation. 器件测试的参数超过spec或者功能fail可以判定为fail。 Mechanical damage, such as cracking, chipping, or breaking of the package, (as defined in test method B101 “External visual”) will be considered a failure, provided that such damage was not induced by fixtures or handling and it is critical to the package performance in the specific application. 机械性的损坏,例如:crack,chipping或者封装break,也要定义为fail,这种还要区分一下是在固定,handling还是在测试后出现的异常。 Cosmetic package defects and degradation of lead finish, or solderability are not considered valid failure criteria for this stress. package表面的defect或者lead的恶化,或者锡球可焊接性出问题,不应该被归类为HTSL导致的fail。 4 Summary The following details shall be specified in the applicable procurement document. a) Electrical test measurements. b) Sample size and number of failures (specify zero if none observed). c) Time and conditions, if other than 1000 hours per condition B. d) Intermediate electrical test measurements, if required. e) Nonvolatile memory data retention pattern (for appropriate devices)

|