ESD防护设计—NMOS的妙用(一)

时间:2023-04-23 11:30来源:番茄ESD小栈 作者:ictest8_edit 点击:

次

在芯片级ESD防护中最普遍的器件就是增强型NMOS(下文中的NMOS都是增强型),接下来的几期会浅谈一下NMOS在ESD防护中的作用与设计思路。

目前主流的ESD-NMOS有两大设计思路:GGNMOS(Gate Ground NMOS),GCNMOS(Gate Couple NMOS)。其中GGNMOS最为常见,设计最为简单。但是其巨大的寄生电容使其在serdes与AD-DA等领域应用受限。而GCNMOS与GGNMOS完全是两种工作原理,GCNMOS的应用场景更为广阔,使用更为灵活,且相较于GGNMOS晦涩复杂且玄学的器件级仿真,GCNMOS可以在cadence中进行电路级仿真,使得其在电路设计人员眼中的可靠性大幅提高(GGNMOS也一样靠谱,但是仿不出来结果。。。没法交差。。。。)

GGNMOS与GCNMOS其本质的差异是工作原理的不同,这期就先从GGNMOS讲起。

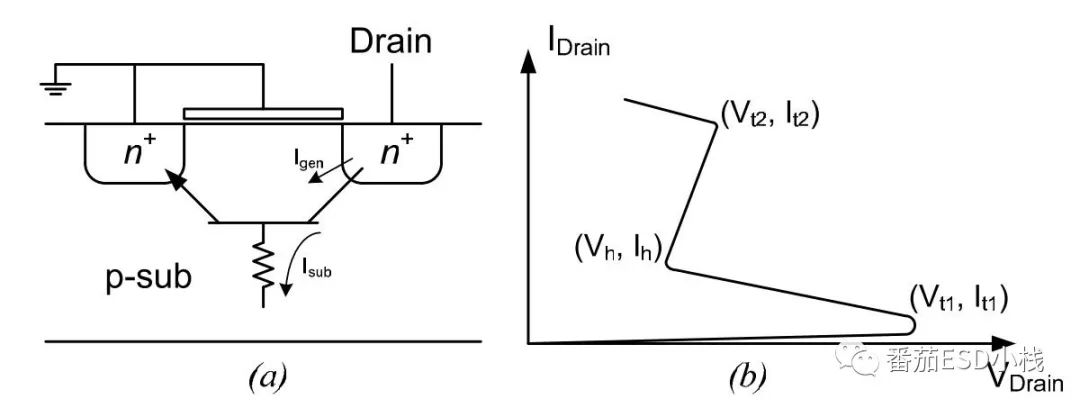

图一.GGNMOS工作原理与TLP曲线

GGNMOS工作原理:

GGNMOS结构如图所示:栅极接地,整个管子处在常关态,导电沟道关闭。通过调整Drain与P-sub的掺杂浓度与拓扑结构使其Breakdown Voltage位于ESD Design Window内,要高于正常工作电压。在正常工作的情况下整个GGNMOS处于高阻态,并联在PAD与GND轨间,不会影响电路的正常工作状态。当ESD电流从PAD进入IC后,整个回路电压提升,当电压达到Drain(N)/Sub(P)的反偏击穿电压后,器件体内Drain/P-sub会发生雪崩击穿,大量雪崩击穿产生的载流子通过衬底电阻,产生压降。当Vsub-source压降>0.7V后,在器件体内由Drain—Psub—Source构成的NPN寄生三极管完全导通,此时Drain的电位对应TLP曲线中的(Vt1,It1)点,该点电压称为trigger voltage。

当发生trigger后,整个GGNMOS表现出负阻行为,称为snap-back,发生snap-back是由于Drain—Psub—Source构成的NPN寄生三极管导通后,来自source端的漂移载流子数目开始增多,导电机制的变化使得维持相同电流的偏压大幅度降低,器件出现负阻特性。当电压降低到Vh,电流提升到Ih。(Vh,Ih)被称为holding voltage,这一点说明器件中电流基本是由漂移载流子提供,雪崩击穿产生的载流子可忽略不计。此时负阻特性结束,整个器件发生电导调制效应,可以理解为整个器件完全导通,IV特性与电阻相似。随着电压与电流的增加,当达到(Vt2,It2)点,整个器件会发生二次击穿,表明器件烧毁。

图二.GGNMOS不同状态下的电场分布。

图二给出了电场分布的大致示意图,并给出大注入情况下的二维横向泊松方程。考虑到三维空间下,在纵向也会产生电场。外加Krik效应与Early效应,真实状态的电场分布会极其复杂。

总结:ESD电流会造成Drain与衬底P-sub的反偏结击穿,此时器件中以雪崩击穿载流子为主,衬底电阻在雪崩载流子作用下产生偏压,Drain—Psub—Source构成的NPN寄生三极管完全导通,此时电压称为Trigger Voltage表明器件开始发生snap-back特性,导电机制发生转变,当偏移载流子提供所有的电流后,电压会降低,该点的电压称为Holding Voltage,之后器件的电路特性类似于电阻,直至二次击穿,器件损坏。

GGNMOS设计思路:

用于ESD防护的NMOS与常规NMOS现阶段已经产生了结构差异。目前最主要的工艺差异有LDD注入和Silicide层,ESD防护器件目前会去除这两项工艺,同时GGNMOS会将Drain拉宽。

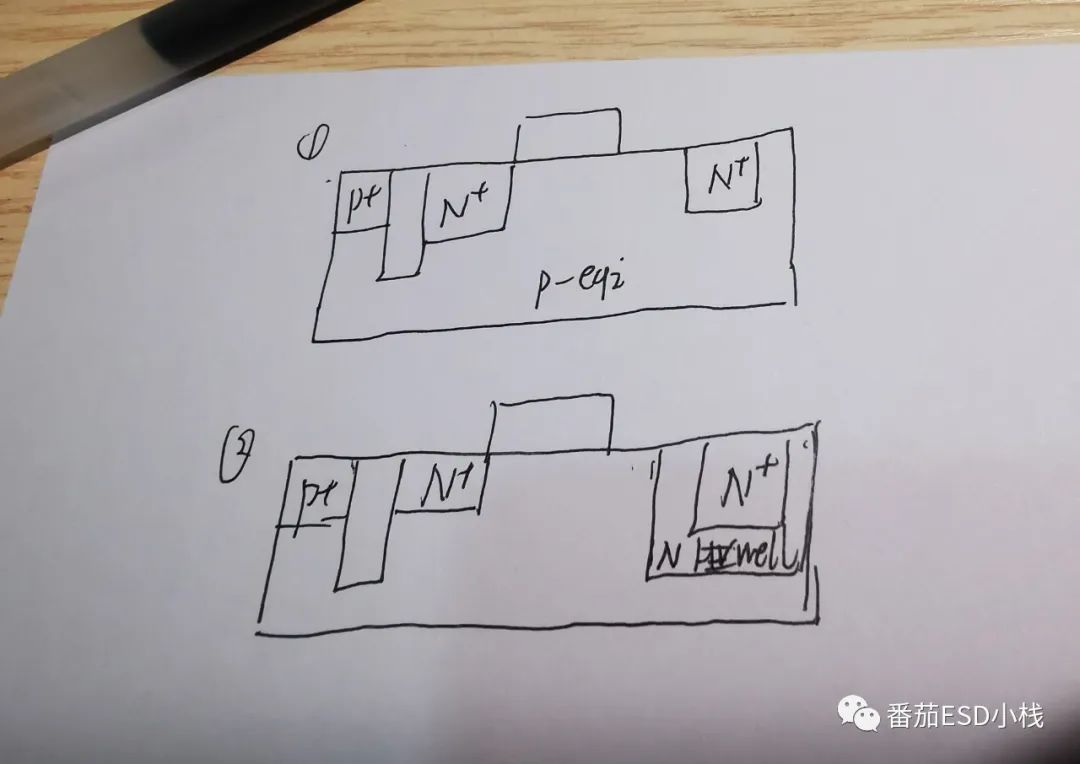

图三.普通NMOS与ESD-NMOS的区别。

LDD在普通NMOS中便于表面沟道的形成,但是在GGNMOS中会造成这部分耐压过低,电场过于集中,不利于器件鲁棒性。同样Silicide是降低源漏区的表面电阻,便于载流子在表面流动,而GGNMOS反而需要载流子往体里流动,通过体内的寄生三极管流出,所以专门的Silicide block mask 遮挡Silicide注入。

目前大部分snap-back型ESD器件的设计思路无外乎三点:trigger Voltage ,holdding Voltage,Second breakdown Voltage 。GGNMOS也是如此。针对trigger Voltage主要是调整反偏PN结的雪崩击穿电压。一种设计思路是改变两边的掺杂浓度:线性缓变结的反向击穿电压会高于突变结,浓度越低反向击穿电压越高。

图四。GGNMOS漏端浓度调节方法。

如图所示,调节方法要么改变P-sub浓度,在某些外延层工艺中衬底替换为P-eqi,要么将N+放入Nwell中。通过这两种思路来改变结击穿电压

|

------分隔线----------------------------