|

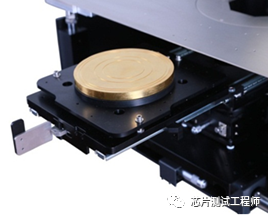

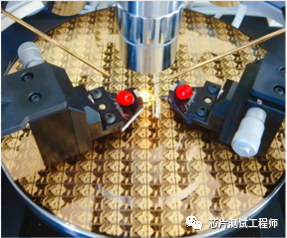

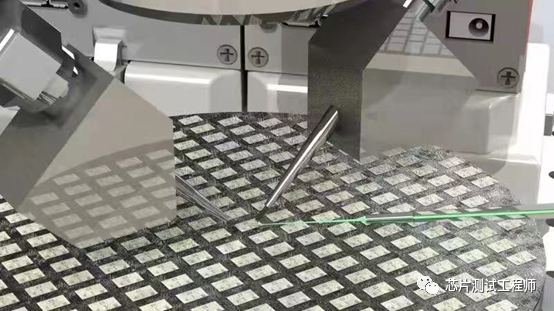

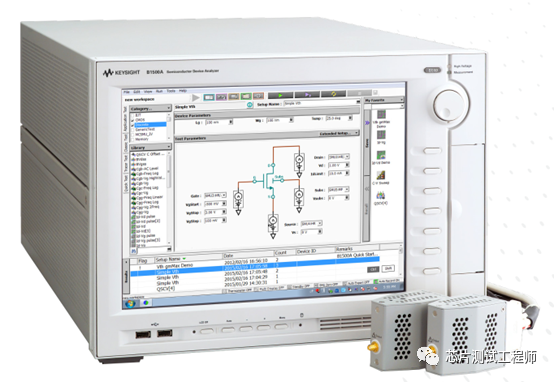

芯片测试是极其重要的一环,有缺陷的芯片能发现的越早越好。在芯片领域有个十倍定律,从设计-->制造-->封装测试-->系统级应用,每晚发现一个环节,芯片公司付出的成本将增加十倍!!! 所以测试是设计公司尤其注重的,如果把有功能缺陷的芯片卖给客户,损失是极其惨重的,不仅是经济上的赔偿,还有损信誉。因此芯片测试的成本也越来越高! 一、常见的测试手段,CP(Chip Probing)测试和FT(Final Test)测试: 1、CP测试 芯片测试分两个阶段,一个是CP(Chip Probing)测试,也就是晶圆(Wafer)测试。另外一个是FT(Final Test)测试,也就是把芯片封装好再进行的测试。  CP(Chip Probing)指的是晶圆测试。CP测试在整个芯片制作流程中处于晶圆制造和封装之间。晶圆(Wafer)制作完成之后,成千上万的裸DIE(未封装的芯片)规则的分布满整个Wafer。由于尚未进行划片封装,芯片的管脚全部裸露在外,这些极微小的管脚需要通过更细的探针台来与测试机台连接。 在未进行划片封装的整片Wafer上,通过探针将裸露的芯片与测试机连接,从而进行的芯片测试就是CP测试。  晶圆CP测试,常应用于功能测试与性能测试中,了解芯片功能是否正常,以及筛掉芯片晶圆中的故障芯片。 2、FT测试 封装后成品FT测试,常应用与功能测试、性能测试和可靠性测试中,检查芯片功能是否正常,以及封装过程中是否有缺陷产生,并且帮助在可靠性测试中用来检测经过“火雪雷电”之后的芯片是不是还能工作。需要应用的设备主要是自动测试设备(ATE)+机械臂(Handler)+仪器仪表,需要制作的硬件是测试板(Loadboard)+测试插座(Socket)等。  二、芯片测试注意事项 1、检测前要了解集成电路及其相关电路的工作原理 检查和修理集成电路前首先要熟悉所用集成电路的功能、内部电路、主要电气参数、各引脚的作用以及引脚的正常电压、波形与外围元件组成电路的工作原理。如果具备以上条件,那么分析和检查会容易许多。  2、测试不要造成引脚间短路 电压测量或用示波器探头测试波形时,表笔或探头不要由于滑动而造成集成电路引脚间短路,最好在与引脚直接连通的外围印刷电路上进行测量。任何瞬间的短路都容易损坏集成电路,在测试扁平型封装的CMOS集成电路时更要加倍小心。 3、严禁在无隔离变压器的情况下,用已接地的测试设备去接触底板带电的电视、音响、录像等设备 严禁用外壳已接地的仪器设备直接测试无电源隔离变压器的电视、音响、录像等设备。虽然一般的收录机都具有电源变压器,当接触到较特殊的尤其是输出功率较大或对采用的电源性质不太了解的电视或音响设备时,首先要弄清该机底盘是否带电,否则极易与底板带电的电视、音响等设备造成电源短路,波及集成电路,造成故障的进一步扩大。 4、要注意电烙铁的绝缘性能 不允许带电使用烙铁焊接,要确认烙铁不带电,最好把烙铁的外壳接地,对MOS电路更应小心,能采用6~8V的低压电路铁就更安全。 5、要保证焊接质量 焊接时确实焊牢,焊锡的堆积、气孔容易造成虚焊。焊接时间一般不超过3秒钟,烙铁的功率应用内热式25W左右。已焊接好的集成电路要仔细查看,最好用欧姆表测量各引脚间有否短路,确认无焊锡粘连现象再接通电源。 6、不要轻易断定集成电路的损坏 不要轻易地判断集成电路已损坏。因为集成电路绝大多数为直接耦合,一旦某一电路不正常,可能会导致多处电压变化,而这些变化不一定是集成电路损坏引起的,另外在有些情况下测得各引脚电压与正常值相符或接近时,也不一定都能说明集成电路就是好的。因为有些软故障不会引起直流电压的变化。 7、测试仪表内阻要大 测量集成电路引脚直流电压时,应选用表头内阻大于20KΩ/V的万用表,否则对某些引脚电压会有较大的测量误差。  8、要注意功率集成电路的散热 功率集成电路应散热良好,不允许不带散热器而处于大功率的状态下工作。 9、引线要合理 如需要加接外围元件代替集成电路内部已损坏部分,应选用小型元器件,且接线要合理以免造成不必要的寄生耦合,尤其是要处理好音频功放集成电路和前置放大电路之间的接地端。 |