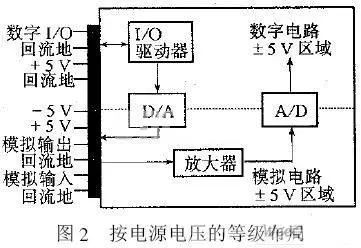

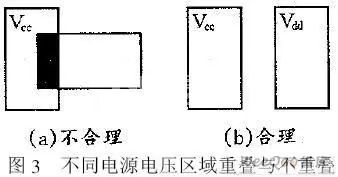

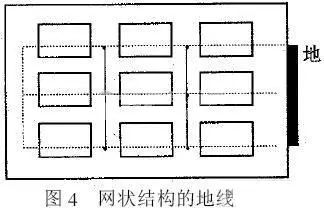

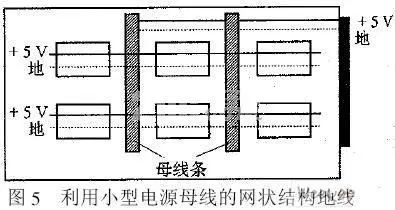

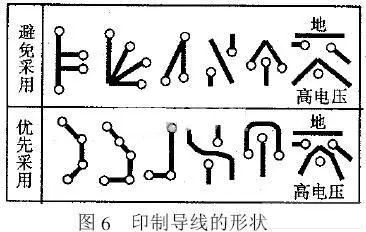

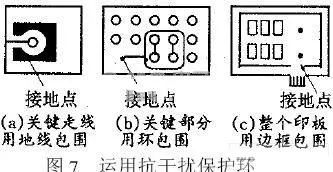

从电子系统电磁兼容性角度出发,详细地叙述了双面印制电路板上的元器件的布局、供电线路和信号线信号线路的布线原则;并对双面印制板的自动布线进行讨论。印制电路板(简称印制板)是电子应用系统中元器件、电源线和信号线的高度集合体。印制板设计的好坏对其系统的电磁兼容性的能力有很大的影响,因此印制板的设计决不单是元器件与线路的简单布局、排布,只要有意识加强电磁兼容性设计,才能使其系统的抗干扰能力增强,稳定性提高。 对于常用的单片机系统,时钟频率一般在4~12 MHz,其余的集成电路多为74HC和74LS系列,若采用单面的印制板,很难满足需要,采用多层的,代价又太大,所以大多采用双面印制板。使用双面印制板时,只要充分地考虑了电磁兼容性问题,是可以满足应用方面要求的。 当然,单片机系统的电磁兼容性所涉及的问题是方方面面的。本文只就双面印制板面上单元电路(或元器件)的布局、线路的布置等与电磁兼容性相关问题进行简要地分析,并相应地给出具体措施。 1 印制板上单元电路的布局 双面印制板上各种单元电路的相互位置,直接影响系统的电磁兼容性。因此对将要使用单元电路的进行甄别就显得很重要。根据单元电路在使用中对电磁兼容性的敏感程度的不同进行分组。分组的目的是为了按组对印制板区间进行分割,让同组元器件放在一起,以便于在空间上保证各组间的元器件不产生相互干扰。一般按工作速度快慢或电源电压的等级进行分组。 1.1按工作速度的快慢分组布局 单元电路工作频率越高,速度就越快,信号的频谱也就越丰富;高频分量比例越大,对外干扰也就越强。可根据单元电路的工作频率分为高速电路(如微处理器),中速电路(如显示处理),低速电路(如接口)和模拟电路(如模拟信号放大器)。多种速度电路在印制板上的布局一般如图1所示。 1.2按工作电源电压的等级分组布局 一般说来电源电压不同,电路的种类往往不同。例如,数字电路用5v的较多,模拟电路中运算放大器等用12v、15v较多;若用同种电源电压的电路中仍有数字与模拟元器件之分,还可以再分组。不同的电源电压的等级布局如图2所示。  注意:不能将电源电压等级不同的元器件交叉重叠,以防止相互串扰。其元器件分布的合理性如图3所示。  [page] 2 地线和电源线的布置 从解决电磁兼容性着眼,印制板上的线,以地线最为重要,所以对双面印制板来说地线要布置得特别合理。 2.1采用分类的地线 地线分类是根据不同的电源电压、数字与模拟、高速与低速和大电流与小电流等分别设置地线。分类设地的目的是为了防止其地线阻抗耦合干扰。双面印制板用轨线作地线,即使轨线较宽,电感量也不能忽略,高频电流通过时仍有可观的电压降,所以一般采用分地方法。所谓的分地,就是在布线时分开,而最后都汇集到直流电源的一点地上。 2.2采用网状结构的地线 对于同类单元电路(或元器件)提高电磁兼容性效果的有效方法是采用网状结构地线如图4所示。图中实线为正面轨线,虚线为反面轨线,实线与虚线相互垂直,交叉点处由金属化孔连接。这样电流可以就近回流。图4中的垂直地线可能给正面布线造成一定困难,可用小型母线来替代,并与电源供电线连结起来如图5所示。图中垂直的宽线条代表小型电流母线,可以装卸,便于调度。   2.3供电线应与地线配合布置 应从两个方面入手,一是尽可能减少供电线路的特性阻抗;二是减小供电回路面积。 双面印制板的供电线路是由轨线组成的,为减小供电用轨线对的特性阻抗,供电轨线和地轨线应尽可能地宽,并且利用正反面使它们相互平行靠近,若可能的话相互放置对应面,使供电环路面积减小到最低程度。不同的供电环路不要相互重叠,以便于减小电磁的干扰。 2.4退耦电容的配置 双面板上采用轨线对供电,除了注意轨线对的走线方式,同时应在每片集成电路旁加容量为0.01~0.10 uF的高频去耦电容,还应在印制板连接的电源轨线对引入处加一个高频去耦电容和一个容量1~10 uF的低频滤波电容,以进一步提高电源去耦滤波的低频特性。 3 信号线的布置 3.1 不相容的信号应相互隔离 高频与低频、电流大与电流小、数字与模拟信号是不相容的。在考虑了不相容元器件的位置后,在信号线的布置上仍应该注意它们之间的隔离,以免相互之间产生耦合干扰。一般可采取以下措施: (1)不相容的信号线应相互远离,不要平行;分布在正反两面的信号线应相互垂直。以减少线间的电场和磁场的耦合干扰。 (2)高速信号线尤其是时钟线应尽可能地短,必要时可在高速信号线的两边加隔离地线。 (3)作为单元电路的输入、输出的信号线应布置在各自区域,不要交叉。 3.2尽量减小信号环路的面积 减小信号环路面积,减少环路的重叠,对于大电流环路抗串扰尤为重要。在双面板上,信号线及其回流线应该紧靠一起布置,最好每条信号线都有自己的回流线,尤其是直流放大器,否则容易给电路造成干扰。 [page] 4 其它电磁兼容性措施 4.1 走线形状不要有缠结和分支或硬拐角。因为那样可能会破坏导线特性阻抗的一致性或导致反射和产生谐波或局部高电压引起放电现象。一般优先选用和避免采用的印制导线形状,如图6所示。  4.2在敏感元器件接线端头和印制板的边框用地、环保护起来,如图7所示。注意保护环不能充当电流回线,只能单点接地。  4.3不要在印制板上留下空白的铜皮层。因为它们既可能充当发射天线,也可能充当接收天线,必须将它们接地。 4.4 I/O驱动电路尽可能靠近印制板边,让它们尽快地离开印制板。 4.5 闲置不用的门电路输入、输出不要悬空;闲置不用的运算放大器同相输入端要接地,反相输入端接其输出。 5 有选择地使用自动布线 印制板布线大多采用布线软件来进行自动布线,这是造成印制板电磁兼容性能力下降的主要原因。自动布线软件事先根据人为规定方法进行布线,其布线的原则大多数都是充分利用印制板的面积资源,目前尚未见到有判断识别相邻件或线相容性能力的自动布线软件。由于双面印制板的可用面积资源有限,所以设计者应谨慎使用自动布线,亲自参与一部分布线工作。一般手工操作的有:印制板区域的分割(元器件的布置);地线与供电线的布置;高速信号线的布置(可首批自动布线);敏感器件的线及线端保护等。 6 结束语 本文从实用的角度讨论了双面印制电路设计中的电磁兼容性技术。根据我们多年在单片机系统应用开发中的经验,力求从实用的角度出发,给出了双面印制板设计中的一些相应抗干扰措施。欢迎关注《必学大课堂》:这里可得到EMC学习干货、技巧、项目案例以及各类资讯等!掌握心得,减少EMC研发成本带来的困境。通常与EMC相关的产品研发成本主要体现在3个方面:1)因EMC测试不通过而导致修改设计带来的开发轮数增加,最终增加的开发成本,不但包括时间,还包括人力,物力;2)对于EMC技术把握不准导致设计或增加无用的元器件成本;3)反复测试而导致的测试费用。 |