I. 半导体器件电气短路测试简介A. IC制造中短路检测的必要性在集成电路(IC)的制造过程中,电气短路是一种常见的缺陷类型。这些短路可能源于多种制造工艺问题,例如颗粒污染、掩模未对准、电迁移残留物或有缺陷的金属化过程。未经检测的短路会导致器件立即发生故障、可靠性降低、功耗过大,在严重情况下甚至可能导致灾难性的故障或损坏器件本身及其所在的系统。且早期识别并剔除有缺陷的裸片可以避免在这些不良品上进行昂贵的封装和后续测试工序,从而显著降低生产成本。因此,短路检测是确保IC质量和可靠性的关键环节。

|

| 测试类型 | 主要目的 | 典型检测机制 | 与H/L测试的相关性 |

| VDD-VSS 电源短路 | 检测电源和地轨之间的直接短路。 | 施加限定电压,测量电流(或反之)。 | 基础性 |

| I/O 引脚开路 | 检测I/O引脚连接的缺失。 | 施加电流,测量电压(二极管测试);或功能性测试。 | H/L测试的背景 |

| I/O 引脚间短路 | 检测两个信号引脚之间的短路。 | 复杂;可能需要特定的矢量图形或高级分析。 | 与H/L测试不同 |

| I/O 引脚至VDD短路 (H型) | 检测I/O引脚与VDD电源轨之间的短路。 | 正向偏置VDD保护二极管或直接测量。 | 核心“H”测试 |

| I/O 引脚至VSS短路 (L型) | 检测I/O引脚与VSS/GND电源轨之间的短路。 | 正向偏置VSS保护二极管或直接测量。 | 核心“L”测试 |

II. VDD-VSS(电源轨)短路

A. 检测原理

VDD-VSS电源轨短路测试旨在识别主电源轨(如VDD, VCC)与地或参考轨(VSS, GND)之间是否存在低阻抗(异常导电)路径。这种短路是一种关键故障模式,一旦器件上电,将导致极大的电流消耗,可能引发热失控、器件烧毁,甚至损坏测试设备 3。

B. 电源轨短路的测试方法学

此类测试通常在器件未上电或仅施加极低功率的状态下进行,以防止在存在短路时造成进一步损坏。常用的方法包括:

① 施加电压,测量电流(Force Voltage, Measure Current - FVMI):

在VDD和VSS之间施加一个低的、电流受限的电压(例如,3中提到的100mV)。然后测量流过该路径的电流。如果测得的电流显著高于预设阈值(例如,3中提到的 >20µA),则表明存在短路。施加电压的电源必须具备电流钳位功能,以防止过流损坏。

② 施加电流,测量电压 (Force Current, Measure Voltage - FIMV):

在VDD和VSS之间强制通过一个小的、受控的电流。然后测量由此产生的电压。如果电压非常低,则表明存在低阻抗路径,即短路。

C. 重要性及测试位置

VDD-VSS短路测试通常是裸片或封装器件上进行的首批电气测试之一。是一个关键的“看门人”步骤。对存在VDD-VSS短路的器件施加全功率可能具有破坏性,不仅损坏DUT,还可能损坏ATE本身。因此,在进行任何其他上电测试之前,对这种严重故障进行低功率的初步检查至关重要。

III. I/O引脚的开路/短路测试

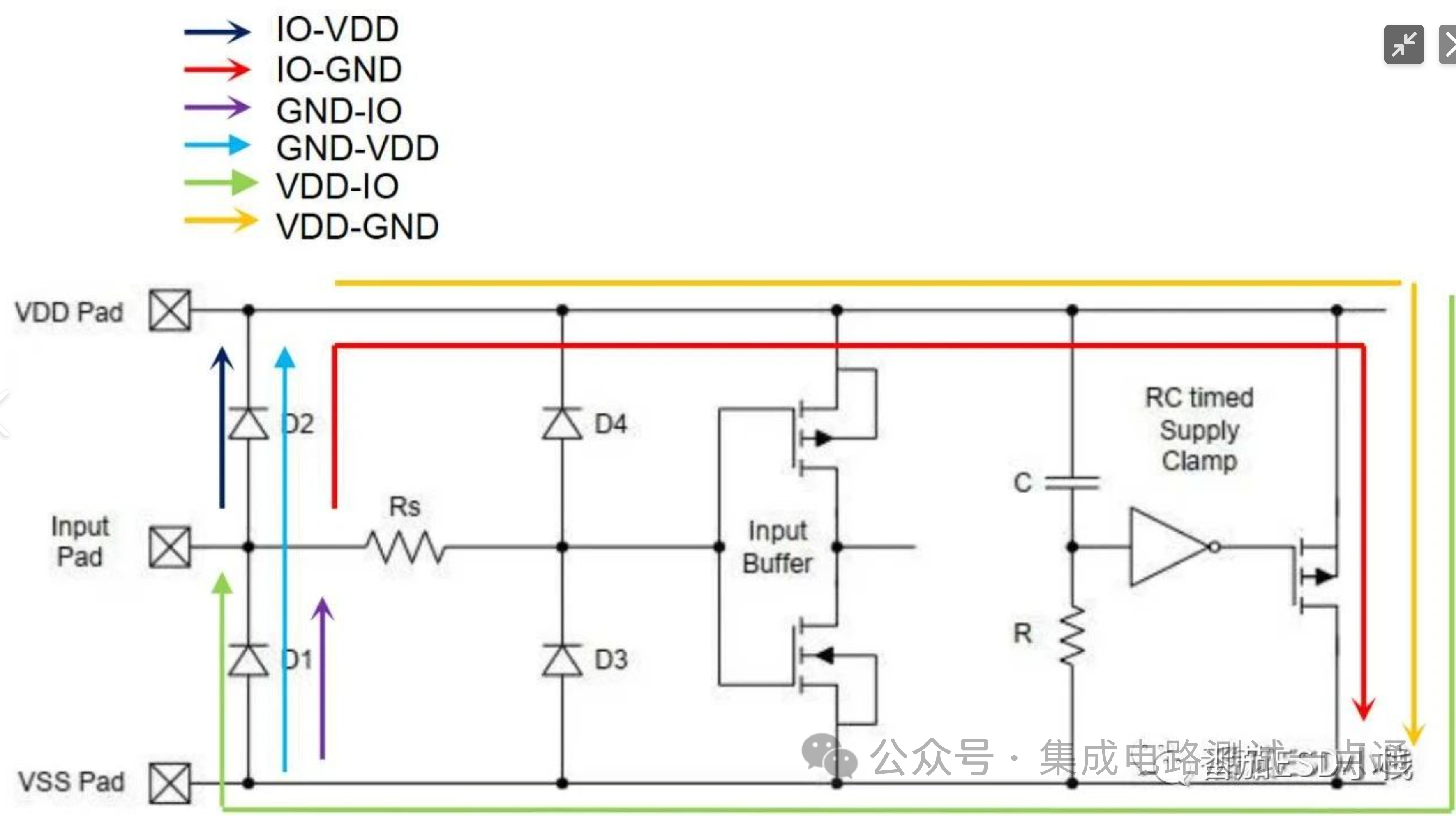

A. ESD电路在IO开短路测试中的作用

现代IC的几乎所有I/O引脚上都集成了静电放电(ESD)保护结构。这些结构通常包括从I/O焊盘连接到VDD的二极管和从I/O焊盘连接到VSS的二极管。它们的主要设计目的是将ESD电流安全地分流,避免损坏内部敏感电路。但在测试中被巧妙地用作检测连续性以及短路/开路缺陷的测试结构。ATE可以通过正向或反向偏置这些具有可预测电气特性(如正向压降、反向偏置泄漏)的二极管,来检查从测试仪引脚到芯片焊盘的连接完整性,并检测与相应电源轨的短路情况 3。

B. I/O引脚连续性的一般测试方法学

此类测试的目标是验证到DUT引脚的电气接触(无“开路”),并检查是否存在与其他引脚或电源轨的意外短路。ATE通常使用其每引脚测量单元(PPMU)或类似的直流资源来执行这些测试。

常用的方法是施加电流,测量电压 (FIMV):向被测引脚(Pin Under Test, PUT)注入或从中抽取一个小的电流(例如3和7中提到的 ±100µA),然后测量PUT上的电压。

· 如果引脚开路,强制电流无法轻易流过,测得的电压通常会达到ATE仪器上预设的电压钳位值,表明存在高阻抗。

· 如果引脚与另一个节点(例如,地或保持在某个电位的另一个引脚)短路,测得的电压将接近该节点的电位(如果短路通过二极管,则会显示二极管压降)。

C. I/O引脚至VDD的“H”短路

· 原理与目标缺陷

· “H”短路测试专门用于检测I/O引脚与高电位电源轨(VDD) 之间是否存在意外的低阻抗路径(短路)。此测试也间接检验了连接I/O引脚与VDD的ESD保护二极管的完整性。此外,它还可以检测某些内部I/O缓冲器故障,例如一个卡死的PMOS上拉晶体管,它会将输出连接到VDD 9。

·

机制与测试执行(以FIMV为例)

除待测引脚外,所有其他I/O引脚和VSS引脚通常保持在0V或已知的低电位 3。向被测引脚(PUT)注入一个小的正电流(例如,+100µA,要在ATE仪器设置电压钳位)然后测量PUT上的电压。

· 预期效果与失效标准

PASS - 引脚良好,未与VDD短路:如果VDD保护二极管完好无损,并且没有与VDD短路,则测得的电压将大约是此二极管阳极所连接电位(例如,如果DUT VDD在此测试中保持在0V,则对于硅二极管,V_put ≈ 0.7V)以上一个二极管正向压降。3给出的通过范围是0.2V到1.5V。

FAIL - 与VDD短路或VDD侧问题

1.如果引脚直接与VDD电源轨短路(且VDD已上电),电压将接近VDD,强制电流将流入VDD。如果测试时DUT VDD为0V,则与此0V VDD短路将导致低电压,类似于与地短路。

2.如果VDD保护二极管短路,电压将很低(接近VDD引脚的电位,如果VDD接地则为0V)。

3.如果VDD二极管测试的电压 > 1.5V,意味着电流正在被灌入,但电压异常高,可能表明与更高电位短路,或存在阻止正常二极管导通至(可能接地的)VDD引脚的问题。

FAIL - 开路:如果引脚开路,当强制注入正电流时,电压通常会升至ATE的正电压钳位值 。

D. I/O引脚至VSS/GND的“L”短路

· 原理与目标缺陷

“L”短路测试专门用于检测I/O引脚与低电位电源轨(VSS或GND) 之间是否存在意外的低阻抗路径(短路)。此测试同样间接检验了连接I/O引脚与VSS的ESD保护二极管的完整性。此外,它还可以检测某些内部I/O缓冲器故障,例如一个卡死的NMOS下拉晶体管 。

· 机制与测试执行(以FIMV为例)

所有其他I/O引脚和VDD引脚通常保持在0V或已知电位(VDD引脚可能保持在0V以隔离VSS二极管测试)。在ATE仪器上设置一个负电压钳位(例如,-2.0V), 从被测引脚(PUT)抽取一个小的负电流(例如,-100µA,这意味着ATE从引脚吸收电流), 测量PUT上的电压。

· 预期结果与失效标准

PASS - 引脚良好,未与VSS短路:如果VSS保护二极管完好无损,并且没有与VSS短路,则测得的电压将大约是此二极管阴极所连接电位(即引脚本身,电流被抽出,因此引脚相对于VSS变为负电位)以下一个二极管正向压降。如果VSS为0V,则V_put ≈ -0.7V。3给出的通过范围是-1.5V到-0.2V。

FAIL - 与VSS短路或VSS侧问题:如果引脚直接与VSS (GND) 短路,测得的电压将非常接近0V(VSS电位),如果VSS保护二极管短路,电压也将接近0V。

FAIL - 开路:如果引脚开路,ATE无法抽取强制电流,测得的电压通常会达到ATE的负电压钳位值 3。

H和L测试在很大程度上是对称的,分别针对互补的保护二极管和电源轨。CMOS I/O结构通常具有连接到VDD和VSS电源轨的对称保护 5。由于各种缺陷机制,短路可能发生在任一电源轨。因此,全面的测试需要独立检查与VDD的短路(H测试)和与VSS的短路(L测试)。测试方法(例如FIMV)是相似的,但电流方向和电压极性相反。这意味着ATE硬件(PPMU)必须能够提供和吸收电流,并测量正负电压,同时具有适当的钳位功能,才能有效地执行H和L测试。

VI. 为何IO引脚要区分“H”(高)和“L”(低)短路测试?

A. 全面的故障隔离与识别特定缺陷

H/L的区分直接有助于缩小故障的可能物理原因范围。不同的物理缺陷表现为与不同电源轨的短路。例如,I/O缓冲器中PMOS晶体管的缺陷更可能导致与VDD短路,而NMOS缺陷可能导致与VSS短路。ESD二极管故障特定于连接VDD的二极管或连接VSS的二极管。外部污染物可能桥接到最近的电源轨。通过识别短路是到H轨还是L轨,失效分析工程师可以将其调查重点放在芯片或封装的特定部分。

与VDD短路(H-Short)可能表明:

· 颗粒物将引脚走线桥接至VDD走线。

· 有缺陷(短路)的至VDD的ESD保护二极管。

· 输出驱动级中卡死的PMOS晶体管 9。

· 金属迁移或枝晶生长至VDD线。

与VSS短路(L-Short)可能表明:

· 颗粒物将引脚走线桥接至VSS走线。

· 有缺陷(短路)的至VSS的ESD保护二极管。

· 输出驱动级中卡死的NMOS晶体管 9。

· 金属迁移或枝晶生长至VSS线。

B. 确保两个电源域及相关电路的功能完整性

I/O缓冲器被设计为驱动或接收相对于VDD和VSS的信号。短路会损害这一基本操作。当I/O引脚输出时,它应该能够在VSS和VDD之间(或接近它们)摆动。当输入时,它应该根据其相对于VDD/VSS参考的VIL/VIH阈值正确感知外部电平。与VDD短路会阻止引脚有效地拉低。与VSS短路会阻止引脚有效地拉高。因此,通过H和L短路测试是I/O引脚可靠数字和模拟功能的前提。这些测试验证了I/O引脚在应有隔离时与VDD和VSS均正确隔离,并确认了两组保护二极管(至VDD和至VSS)的功能。下表总结了“H”和“L” I/O引脚短路测试的主要区别:

| 特性 | “H”(高)短路测试 | “L”(低)短路测试 |

| 目标电源轨 | VDD (高电位电源) | VSS/GND (低电位电源/地) |

| 主要测试二极管 | I/O焊盘至VDD的保护二极管 | I/O焊盘至VSS的保护二极管 |

| 典型电流施加 | 向引脚注入正电流 | 从引脚抽取负电流 |

| 典型电压测量 | 正电压 (例如, 若VDD=0V则约为0.7V) | 负电压 (例如, 约 -0.7V) |

| 与目标轨短路 | 电压接近VDD (若VDD激活) 或低电压 (若VDD=0V且二极管短路) | 电压接近VSS (例如, 约0V) |

| 开路指示 | 电压钳位在高电平 (ATE正向钳位) | 电压钳位在低电平 (ATE负向钳位) |

| 相关缺陷 | PMOS卡死, VDD侧ESD失效, 桥接到VDD | NMOS卡死, VSS侧ESD失效, 桥接到VSS |