|

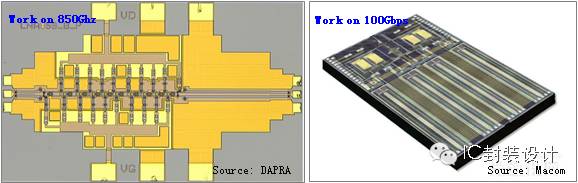

市场的需求,推动技术进步。今天物联网、大数据、云计算等新一波浪潮来袭,万物互联必将产生海量的数据,数据的传输需要硬件来承载。信号的频率越来越高,khz、Mhz、Ghz,目前Thz芯片已经慢慢的开始商用。数据传输的速率也越来越快,尤其是光传输技术的发展,光模块的小型化,使得光通信技术慢慢从网络产品普及到桌面产品上来。动辄几十上百Gbps的传输速率,给SI设计带来挑战。如此高的频率和速率,电信号在传输时,以前不太关注的芯片封装,现在也必须考虑进来。

图1 Thz芯片和100Gbps光芯片

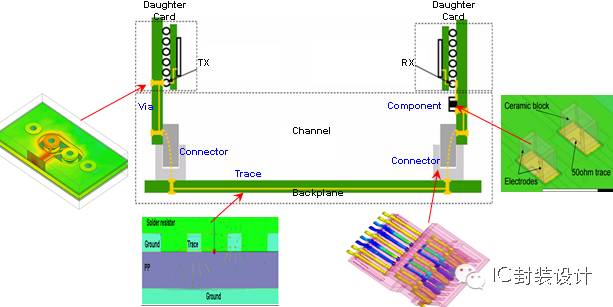

电性优化的目的,本质上来说就是最大提升传输效率,减少传输损耗。过去我们优化设计主要着眼于系统和PCB这个级别,很少触及到封装和芯片。这个级别的仿真优化,主要集中在器件引脚、过孔、接插件等结构不连续的地方(图2)。

图2 系统级SI仿真优化

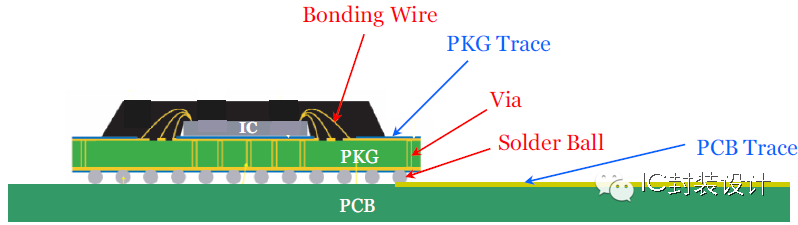

封装是芯片到PCB的过渡,这里的信号传输路径处处存在着不连续(图3),优化这些结构上的不连续点,使其保持电性上的连续,减少信号的反射,就是封装SI优化的目的。接下来我们参照图3的互联结构,逐一简要介绍各不连续点的优化方向,仅供参考。

图3 封装上的互联结构

1. Bonding Wire

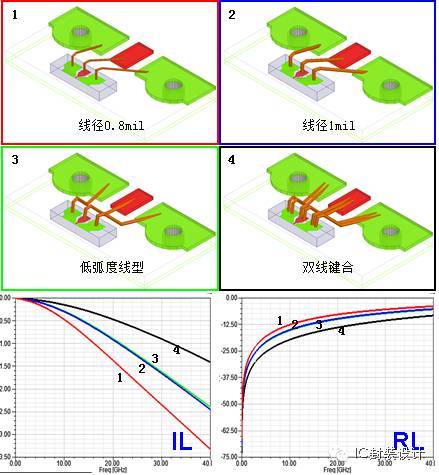

关于Bonding Wire的优化,主要涉及到信号和回流地的布置,金线的长度、直径、线型、线数等。这里只对其他几个参数再做讨论。

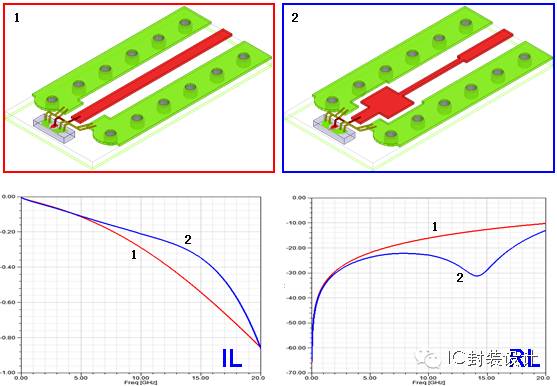

Bonding Wire从芯片键合到载板,仿真结构建模如图4;端口1设在芯片端,CPW结构,阻抗50Ohm;端口2设在载板端,GCPW结构,阻抗50Ohm;分别调整线径,线型、线数三个因子,仿真频率扫描0~40Ghz,后处理对比S21和S11参数。

图4 Bonding wire对传输特性的影响

结论:

1. 金线直径越大,传输特性越好;

2. 键合线弧度越低,传输特性越好;

3. 双线键合,传输特性优于单线键合。

对于超高频应用,仅仅通过调整以上参数来优化传输特性,依然满足不了应用,键合线匹配就派上了用场。由于整个键合结构在一定频率范围内可以等效为电感,这样我们就可根据射频理论进行阻抗匹配。对比下面键合线匹配前后的传输特性,可以看出匹配在感兴趣的频段内,极大的优化了传输特性。

图5 键合线匹配对传输特性的影响

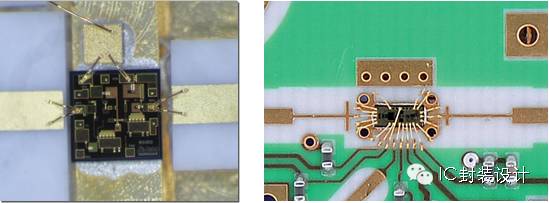

下图是Wedge-Wedge低弧型双线键合和金线阻抗匹配的应用案例。

图6 低弧度双线键合和金线阻抗匹配

2. PKG Trace

PKG Trace即封装基板上的走线,由于这段是均匀传输结构,结构上没有需要优化的点。我们更多关注在仿真时建模的准确性,考虑阻焊的厚度、Mold compond,以及不同的基板工艺带来的线路图形差异。

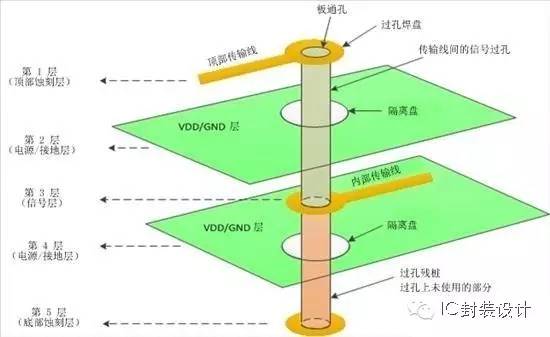

3. Via

影响过孔传输特性的参数,包括孔大小、孔壁厚度、Pad大小、Anti-pad大小、回流地孔的数量、距离等等,网络上关于PCB过孔优化的文章非常多,封装基板过孔优化可以借鉴,建模时注意封装基板工艺带来的过孔结构差异(叠孔、填铜等)即可,其他不赘述。

图7 Via结构

4. Solder Ball

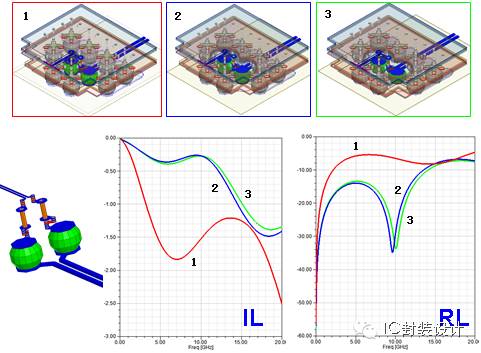

Solder Ball是封装和PCB的互联界面,因此这里的优化涉及到两个部分——封装基板和PCB,涉及到的结构有Ball Pad,Solder ball大小、高度、间距、回流Ball位置等。下图,100Ohm差分阻抗走线,从封装基板(4+2+4叠层结构)通过Via和Solder ball过度到PCB上的100Ohm差分走线。

这里我们仅对基板和PCB的Ball Pad阻抗优化,以及降低Solder Ball的高度,仿真对比传输特性。由于Ball Pad为处阻抗被拉低,我们通过挖空参考层的方法提高其阻抗(在“优化封装以满足SerDes应用键合线封装规范”已有描述),减小突变;降低Solder Ball的高度,减小回路电感。通过对比仿真结果我们可以看出,以上两措施均对传输特性均有提高,尤其挖空Ball pad参考层的措施。

图8 Solder Ball互联界面结构及优化

5. Bump

由于Flipchip的Bump与BGA的Solder Ball结构相似,所以Flipchip可用同样的方法优化传输特性。另外,Ball和Bump在高频时呈感性,同样可以用阻抗匹配的方法进行优化,下图是优化案例。

图9 Bump阻抗匹配

本文主要着眼于封装结构的电性仿真,讨论了Bonding Wire、Bump、PKG Trace、Via、Solder Ball等对传输特性的影响。以上都是针对结构上的讨论,对于封装工艺、材料等对电性的影响,后面我们单独开篇再作讨论。

|