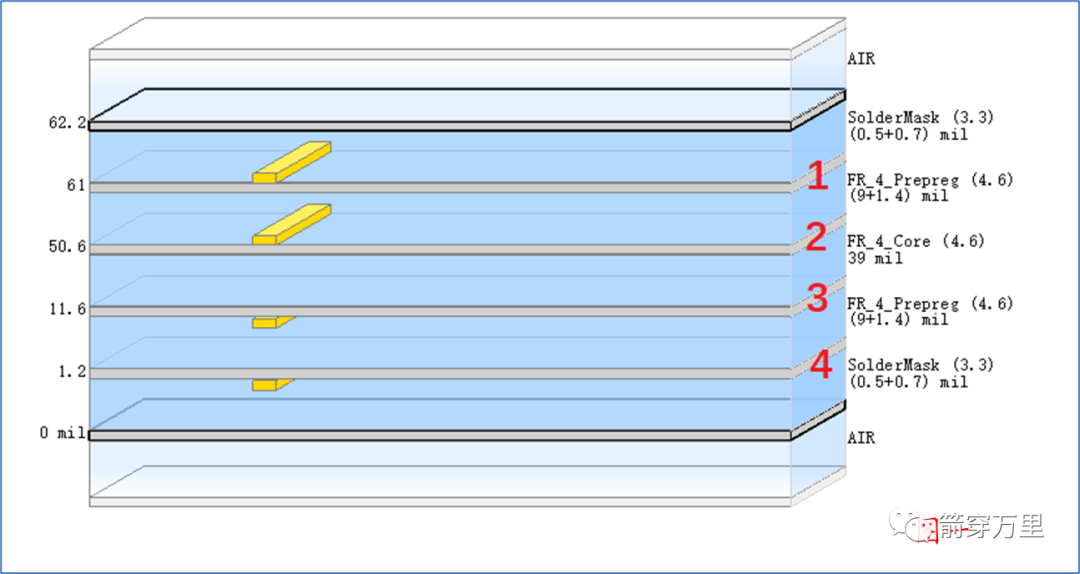

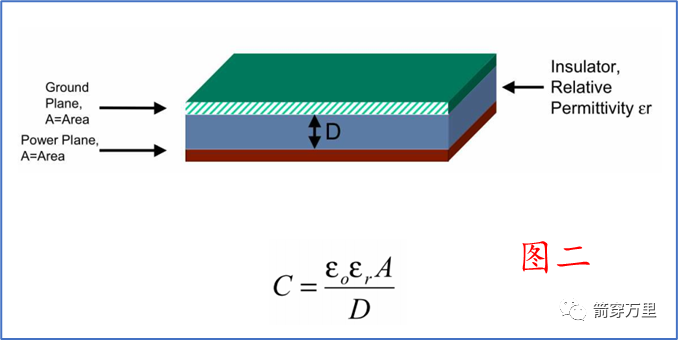

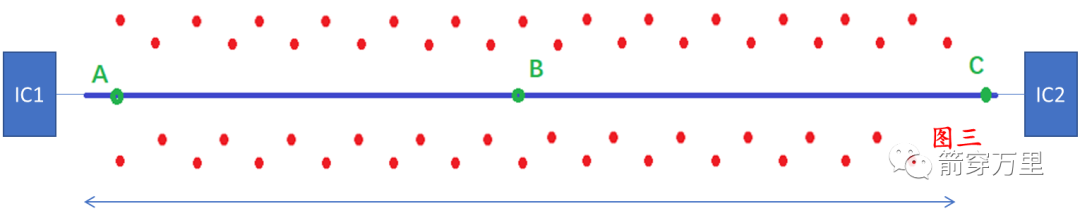

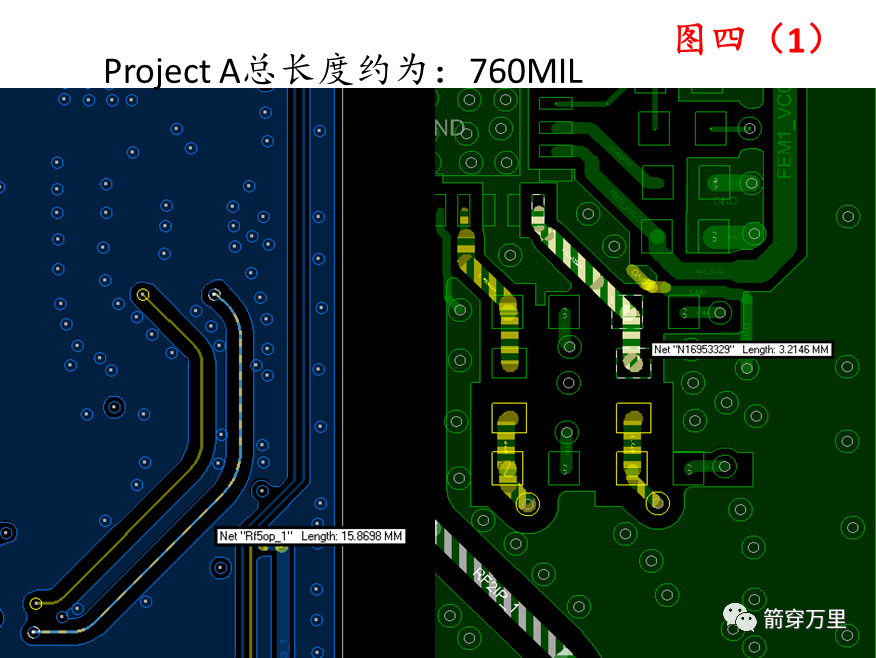

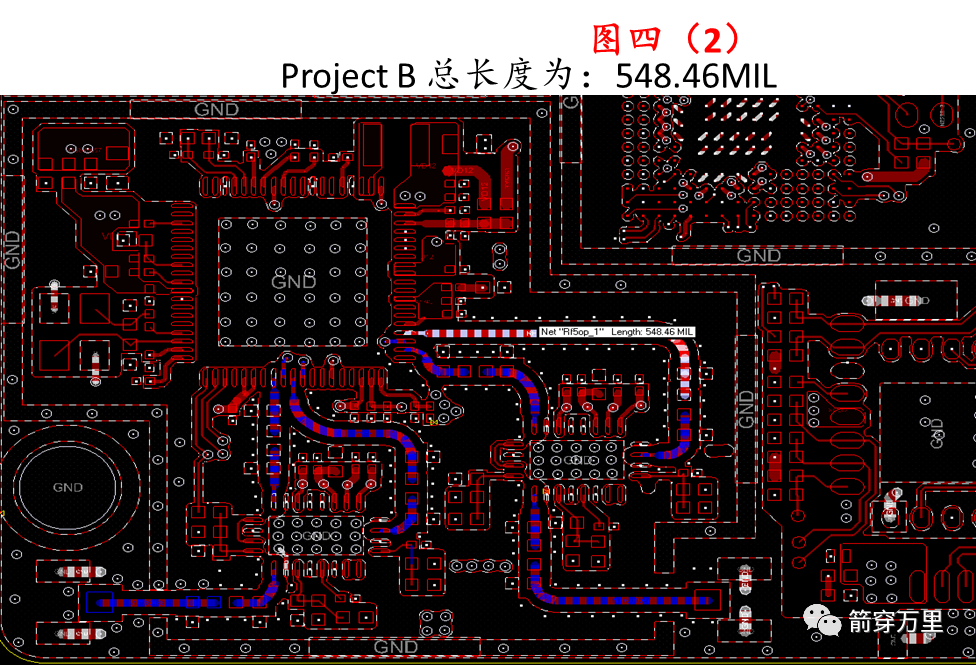

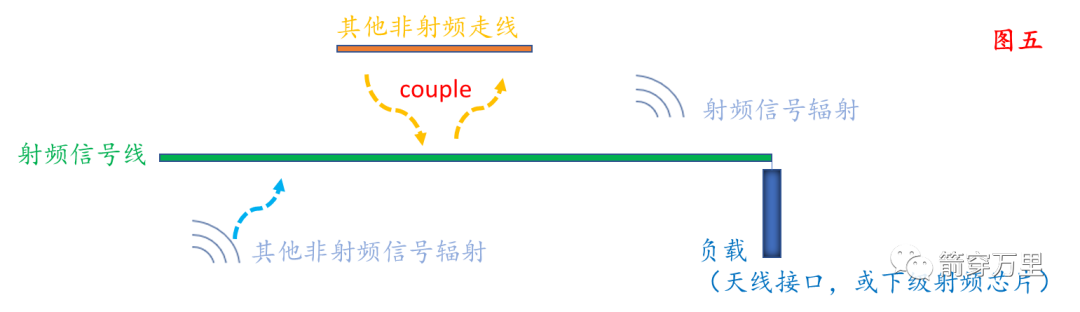

一、走最短的线,让其他信号无路“可走”我们经常会听到,RF走线越短越好,那么是为什么呢?①使阻抗可控 看一下PCB架构模型(以四层板为例)如图一: 最上方和最下方为空气环境,第二和第五为Solder Mask(在实际的layout软件中,这两层是不算叠层结构的),图中红色数字为实际的有金属材质的导电层,他们中间为绝缘体介质  我们知道,两个相互靠近的导体,中间夹一层不导电的绝缘介质,会构成电容器(如图二)。  那么射频走线上,必然会有寄生电容产生。 故此我们在将Gerber文档提供给PCB板厂的时候,通常会要求板厂在射频走线上,做50Ω阻抗控制。 张三说道:既然我们做了50Ω阻抗控制了,那么就可以忽略了这些寄生电容和电感了啊! 不然,PCB是做好了,但当我们将器件打在板子上的时候,就会发生变化。 李四又说,我的IC都是50Ω输入输出啊! 对的,实际上芯片很难100%做到50Ω的输入输出,基本上都是接近50Ω,如果走线阻抗在有误差,就射频线路上就偏差变大了。 汪二说:可是,我们很多板子打好,焊接后,没有调试,输出结果也和规格书一样啊。 汪二别捣乱,这里面就牵扯到50Ω阻抗的来源,请听我接着说。 在微波应用最初的时候,人类使用线缆传输并没有意识到阻抗的重要性,用着用着,发现有很多问题,能量损耗,传输的越远,损耗越大。有时候会发现电缆被烧坏了。 为了满足实际使用需求,降低损耗,提升安全性能,在1929年,贝尔实验室做了很多实验,最终发现符合这种大功率传输,损耗小的同轴电缆其特征阻抗分别是30欧姆和77欧姆,当然最低损耗的空气填充线的阻抗是93欧姆(这个没有被采用)。 即:30Ω是最大功率输出的最佳阻抗,77Ω为损耗最小的最佳阻抗。 为了满足大功率传输和低损耗需求,工程上采取了折中处理方案,一群人采用了算数平均值:53.5Ω,另一群人采用了几何平均值约48(几何平均数是n个变量值连乘积的n次方根)。 随着半导体的发展,业内为了行业发展有序(这里面还有欧美争抢标准的戏码,不再赘述),采用了美国的50Ω阻抗作为标准。 所以,如果你的阻抗在50Ω附近的话,对于输出输入的影响不是很大。 也可以说明“我们在实际调试中,基于L,C的实际使用值的限制,在史密斯圆图上调到50附近即可以满足实际使用需求的原因” 扯远了,回到正题。 在实际设计中PCB 射频走线 layout,很少有精准50Ω控制的,大的PCB板厂相对好些,很多小厂就呵呵了,我亲身经历的过小厂的PCB阻抗控制,EVT调试阶段还好好的,结果DVT, MP的时候,大量的阻抗不良,说多了都是泪。 所以这就需要我们去做阻抗调试了。 汪二:这个和射频走线长短有啥关系? 我:就你事多!再啰嗦,下次你不用出场,割掉算了! 如果阻抗做的好,寄生电容影响就越小,但是再小的影响也架不住数量啊,量变引起质变,加上板其他noise干扰,走线越长,影响越大。  如果走线很长的话,走线中还有拐角的并且还有过孔走线,就需要在走线上加三个“π”或者“L”型的匹配预留电路如图三(前,中,后)。 举个“栗子”(如图四):   Project A花了两周完成两路调试和优化阻抗(刚打出来的板子-TX:13dBm,EVM:-21) Project B 打完板子就可以使用(802.11g,54Mbps,TX:21dBm,EVM:-26),花3天时间优化两路阻抗。(这两个项目,受限于没有网分的原因,采用盲调方式。) ②减少干扰(射频信号干扰其他器件,或其他器件干扰射频信号)  这些干扰,可能是改变阻抗,可能是产生了杂讯,不管哪一种都不是我们期望的 |