|

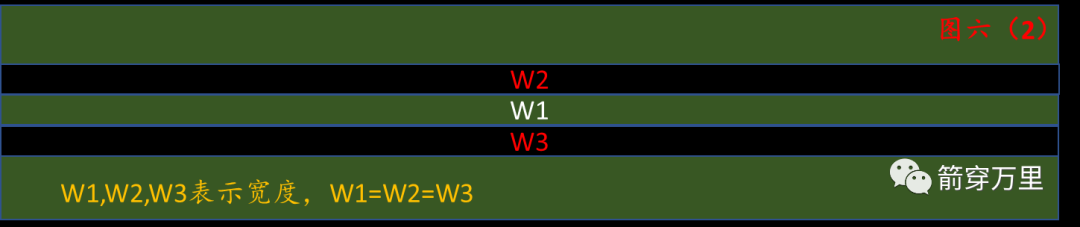

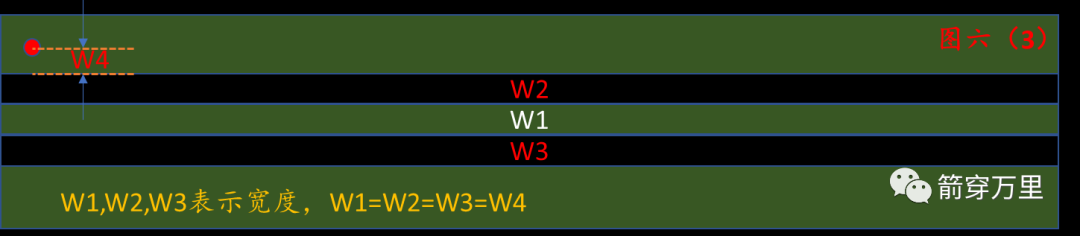

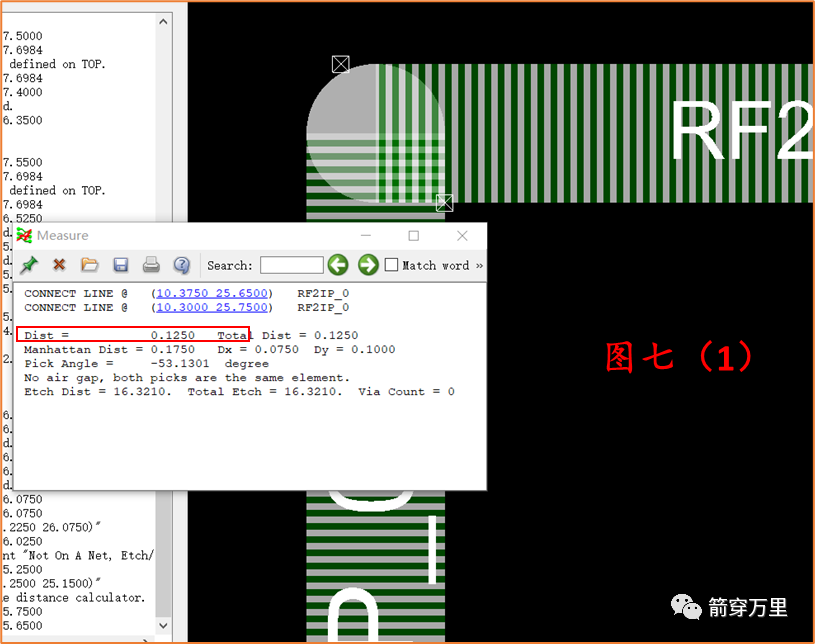

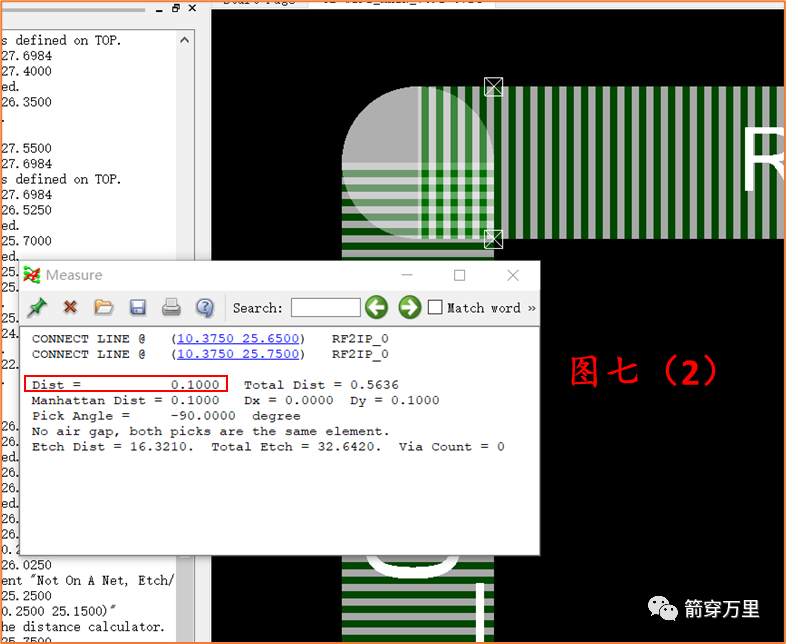

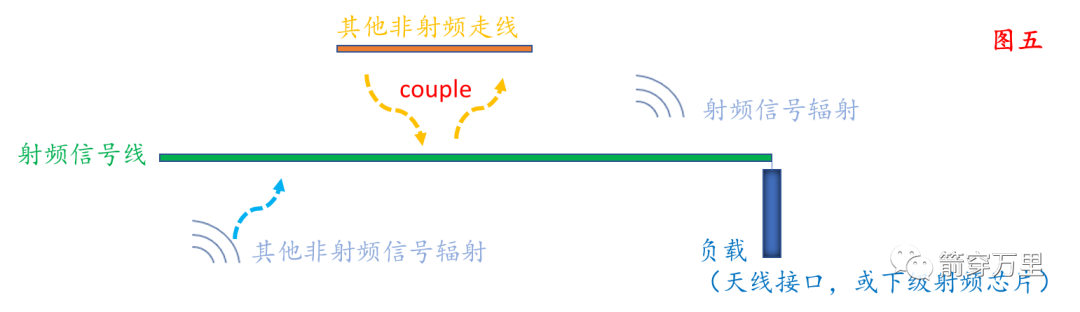

二、走线遵循“3W” 原则,同时添加VIA。 ①走线宽度 射频走线不能太细,也不可太宽。 太细的话,PCB板厂做不到(大部分板厂工艺控制是≥4mil),太宽的话,阻抗和板厚不好控制在需求范围,小功率信号(P1≤4W)控制在6~15mil,大功率的信号还需要考虑功放的偏置电压电路的电流所需承载宽度(比如有的8W的平均输出功率的管子走线,其偏置电压电路和射频走线会有重叠交叉,这里就要考虑射频走线增加宽度了,其宽度可能需要和0805电容宽度近似:1.25mm),具体走线宽度还是需要和实际应用相结合。 ②走线两侧净空区 不管什么走线,两边都是挖空的,不挖空就短路了。 既然我们知道了PCB板有寄生电容,外部干扰等因素,我们就要做隔离。 第一步隔离走线两侧净空区(即挖空区域),净空区宽度遵循3W原则: 为了保证线与线之间的距离足够大,当线与线中心间距不少于3倍线宽,如果线中心距不少于3倍线宽时,则可保持70%的线间电场不互相干扰,称为3W规则(实际上,在射频里面,我们很少会让两根射频线靠地很近,但是我们走线两侧的净空区也遵循3W原则,太近了抗干扰能力差,靠远了,焊接元件不方便) 如图六   第二步放置VIA VIA中心和走线净空区边上的距离要大于1个W,射频走线两侧放置VIA. 也不要距离太远,太远的话隔离效果变差。VIA边和VIA边之间保持8mil。   三、走线尽量走直线,弧线或45°线,不要走≤90°!条件允许的话,最好是走直线或弧线 走≤90°线会引起阻抗不连续的问题 我们可以看到直角走线,在传输线拐角处,会改变线宽,90°拐角处线宽约为正常线宽的1.2~1.414倍(如图七),由于线宽改变了,那么对应的阻抗也会改变,造成了阻抗不连续,还会引起造成信号的反射。 如果走锐角,那么在PCB导线相交锐角处,会造成一种叫酸角“acid traps”的问题,在pcb制板过程中,在pcb线路蚀刻环节,在“acid traps”处会造成pcb线路腐蚀过度,带来pcb线路虚断的问题。   四、射频走线尽量不要过孔 射频信号线尽量不要过孔,除了阻抗连线性问题,还有衰减,每一个过孔大概有0.5dB左右的信号衰减。 如果信号一定要交叉走内层的话(例如4层板就走L3),建议2G优先于5G(这个问题,大家可以从不同频率的衰减程度来思考一下),RX优先于TX(RX辐射小,TX辐射强度大对应的耦合几率高) 五、射频走线附近尽量不要有其他高速信号走线 在layout的时候,我们通常有许多线需要过孔,走第三层,第四层。从图五,我们可以知道,射频走线附近(不论是在同层还是在不同层)尽量不要走高速信号线(特别是射频芯片正下方叠层不可以走),或干脆不走信号线,避免相互干扰.  这样的话,其他谐波就很少会串扰到主信号上,导致我们认证不过。 |