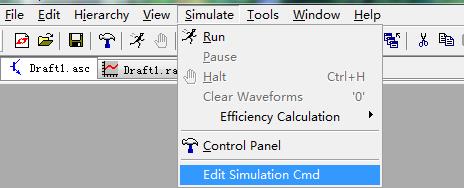

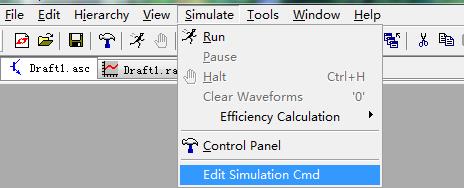

我们知道,运放在实际应用中可能会出现自激振荡现象,基于辅助运放的测试电路也是这样。自激振荡一旦产生,轻则导致测试时间增加,严重的话,会导致测试结果不准确,产生质量隐患。下面我们用 LTSpice IV 来仿真一下。(《测试基础篇-电容与电感对电流测试的影响》 文中有 LTSpice IV 的下载链接。)电路画好之后,可参考下面来设置,截止时间设置为10mS。  |

我们知道,运放在实际应用中可能会出现自激振荡现象,基于辅助运放的测试电路也是这样。自激振荡一旦产生,轻则导致测试时间增加,严重的话,会导致测试结果不准确,产生质量隐患。下面我们用 LTSpice IV 来仿真一下。(《测试基础篇-电容与电感对电流测试的影响》 文中有 LTSpice IV 的下载链接。)电路画好之后,可参考下面来设置,截止时间设置为10mS。  |