|

接上电源滤波,下面将讲解阻抗匹配,传输线路等方面问题,继续学习。我们先来了解一下什么是传输线:

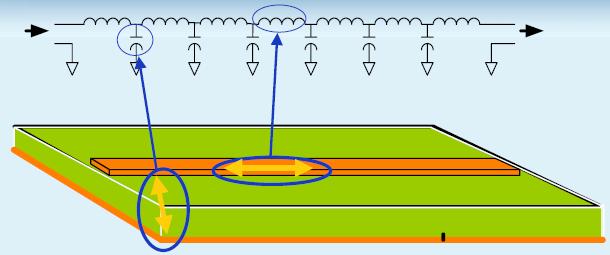

传输线是将电磁波(能量)从源位置传到目标(负载)位置的一对导电体,在电路板(PCB) 上,它们由线路和基准金属结构(通常是电源层或接地层)组成,任何其它导电结构也能构成,串联的过孔、连接器、相邻线路、PCB 铜多边形甚至金属盒

一块PCB上其传输线的电子模型可以如下图示意:

典型的PCB 线路传输线路是

低通滤波器-是其频散特性的结果

延时线路

具有插入损失(输出= 输入-损失)

具有固定的特性阻抗

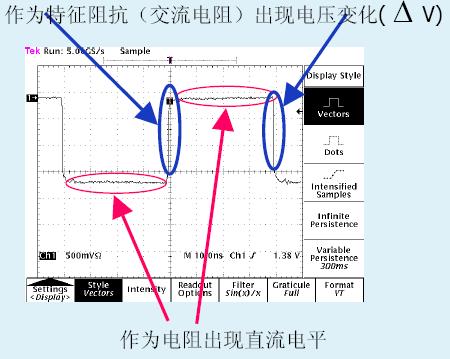

其传输线效应如下:

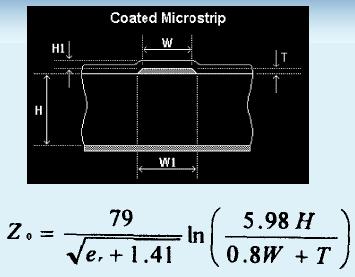

其传输线阻抗计算公式(表面微波传输线)如下:

Er= 材料介电常数

H = 线路到层的距离

W = 线路宽度

T = 线路厚度

Zo= 线路的特征阻抗

PCB 传输线阻抗因素

PCB传输线的物理厚度(宽度 上,Z 下)

PCB传输线的物理宽度(宽度上,Z 下)

容纳介质

PCB 基层的介电常数(Er)(宽度上,Z 下)

焊接掩膜(如果存在)的Er(Er上,Z 下)

焊接掩膜的厚度(厚度上,Z 下)

物理邻接任何基准导体

(通常为PCB 电源层)(距离?,Z 上)

物理微扰

过孔(电容上Z 下)

过渡(例如线路到连接口Connector)(上或下)

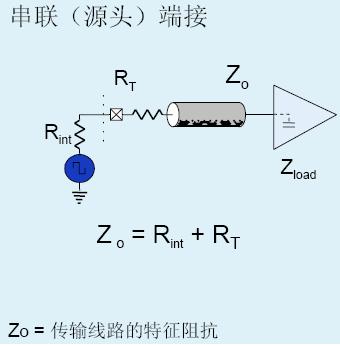

传输线端接

端接通过使能量波在希望的物理点消耗能量,从而削弱能量反射

在无内部端接的信号环境中(PECL、CML、HSTL 和ECL)下拉电路的质量直接影响波形下降沿时间和质量

即使有的元件提供了片内端接ODT (On Die Termination), 系统设计师也要考虑是否需要电路板上端接

传输线串联端接:特别适合无需直流偏压的低阻抗输出驱动器,包括CMOS 和ECL 源驱动器。

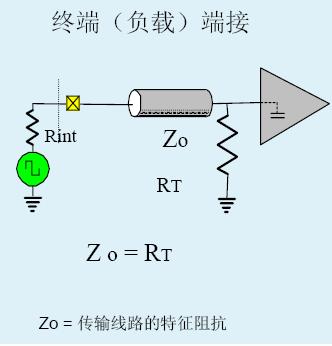

传输线终端端接:可以用于无需直流偏压的TTL,CMOS 源驱动器。有时通过将端接电阻连接到VCC 而不是接地,可能有利于弱的上拉驱动器。

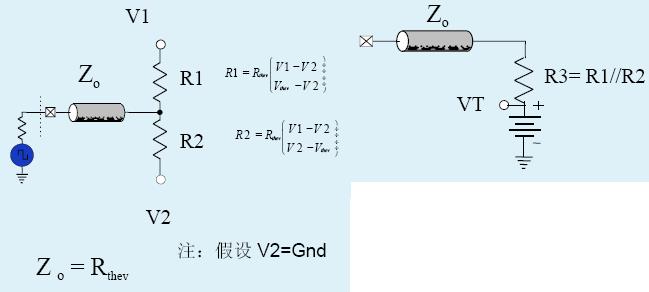

传输线并联端接:用直流偏压进行分流负载端接,主要用于需要直流偏压ECL端接。直流偏压点最可能设于阀值电压点。消耗直流电流。

差动传输线的端接,差动信号端接布局

一个电阻的端接(上图):可以削弱能量反射,抑制差动噪声干扰,共摸噪声的抗干扰能力不足。

更佳的端接(下图):可以更好地抵抗差动干扰和共摸噪声的干扰。

至此我们来简单总结一下本文所学到的知识:

1、了解系统抖动率敏感性(例如周期差抖动、长期抖动或周期抖动)

2、根据需要设计最有效的滤波电路

3、使用高频RF PCB 布线技巧

4、使用控制阻抗传输线路

5、正确端接传输线

以下网站提供了优秀的旁路和传输线阻抗计算软件和参考资料:

www.ultracad.com

www.polar.com

参考书

使抖动率最小的电源和布线考虑因素 徐建梅

《印刷电路手册》”Printed Circuit Handbook”

Clyde Coumbs著

ISBN:0-07-012608-9

《高速数字设计》”High Speed Digital Design”

Howard Johnson 著

ISBN:0-13-395724-1

|